1 、引言

ARM(Advanced RISC Machines)既可以認(rèn)為是一個公司。也可以認(rèn)為是對一類微處理器的統(tǒng)稱,還可以認(rèn)為是一項技術(shù)。基于ARM技術(shù)的微處理器應(yīng)用約占據(jù)了32位RISC微處理器75%以上的市場份額,ARM技術(shù)正在逐步滲入到人們生活的各個方面。到目前為止,ARM微處理器及技術(shù)已經(jīng)廣泛應(yīng)用到各個領(lǐng)域,包括工業(yè)控制領(lǐng)域、網(wǎng)絡(luò)應(yīng)用、消費(fèi)類電子產(chǎn)品、成像和安全產(chǎn)品等。

FPGA(Field Programmable Gate Array)是一種高密度現(xiàn)場可編程邏輯器件,其邏輯功能是通過把設(shè)計生成的數(shù)據(jù)文件配置到器件內(nèi)部的靜態(tài)配置數(shù)據(jù)存儲器(SRAM)來實(shí)現(xiàn)的。FPGA具有可重復(fù)編程性,能靈活實(shí)現(xiàn)各種邏輯功能。

基于SRAM工藝的FPGA具有易失性。系統(tǒng)掉電以后其內(nèi)部配置數(shù)據(jù)容易丟失,因此需要外接ROM保存其配置數(shù)據(jù),系統(tǒng)上電后必須重新配置數(shù)據(jù)才能正常工作。目前有兩種方案可以實(shí)現(xiàn),一種是使用專用的PROM,以Xilinx公司FPGA,XCFxx系列PROM為例,能夠提供FPGA的配置時序,上電時自動加載PROM中的配置數(shù)據(jù)到FPGA的SRAM中;另一種是在含有微處理器的系統(tǒng)(如嵌入式系統(tǒng))中采用其他非易失性存儲器如E2PROM、Flash存儲配置數(shù)據(jù),微處理器模擬FPGA的配置時序?qū)OM中的數(shù)據(jù)置入FPGA。與第一種方案相比,該方案節(jié)省成本、縮小系統(tǒng)體積。適用于對成本和體積苛刻要求的系統(tǒng)。

在便攜式虛擬儀器設(shè)計中,使用嵌入式系統(tǒng)和FPGA實(shí)現(xiàn)系統(tǒng)功能。嵌入式微處理器采用Samsung公司的ARM7TDMI系列處理器S3C44BOX:FPGA采用Xilinx公司的Spartan-3E系列XC3S100E,采用S3C44BOX完成對XC3S100E的配置。取得了良好效果。

2 、從串配置的原理

2.1從串配置原理

Xilinx公司的Spartan-3E系列FPGA產(chǎn)品是采用90 nm工藝的2.5 V低電壓FPGA器

件,具有高性能、低功耗、可無限次編寫的特點(diǎn)。XC3S100E是Spartan-3E系列FPGA中的一款,總門數(shù)達(dá)10萬門,可采用從串、主串、從并、主并、JTAG等模式對其進(jìn)行配置[2]。XC3S100E與從串配置模式相關(guān)的主要引腳功能如下:

M[2:0]:配置模式選擇。M2、M1、M0均接上拉電阻,即M[2:0]:111時為從串模式;

CCLK:配置時鐘,微處理器提供時鐘源,且上升沿有效:

DIN:串行配置數(shù)據(jù)輸入:

DOUT:串行數(shù)據(jù)輸出,用于菊花鏈?zhǔn)脚渲茫?/p>

PROG_B:低電平異步復(fù)位FPGA內(nèi)部邏輯,內(nèi)部可配置:Memory完全復(fù)位后,該引腳指示高電平。

當(dāng)此引腳為高時,才能配置FPGA:

INIT_B:由低電平到高電平跳變時,采樣配置模式,即M[2:0]的值確定配置方式;配置過程中若出現(xiàn)配置錯誤,INIT_B將呈現(xiàn)低電平;

DONE:復(fù)位時為低電平。若配置成功,則為高電平。

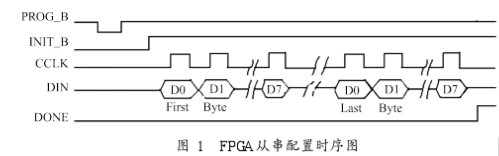

2.2微處理器從串配置:FPGA的時序

FPGA的配置過程如下:

系統(tǒng)上電后,將PROG_B拉低以復(fù)位FPGA內(nèi)部邏輯重新配置FPGA,充分復(fù)位內(nèi)部邏輯后(約100μs),將PROG_置高。

INIT_B為低電平,PROG_B拉高保持300 ns后,F(xiàn)PGA將INIT_B置高。在INIT_B由低向高跳變的瞬間,采樣配置模式M[2:0]。此系統(tǒng)采用從串配置模式。

在FPGA采樣配置模式后,微處理器就可以向FPGA配置時鐘CCLK和數(shù)據(jù),在CCLK的上升沿,傳輸數(shù)據(jù)至DIN,數(shù)據(jù)字節(jié)先發(fā)送低位,再發(fā)送高位。配置過程中若發(fā)生錯誤,則INIT_B為低電平。

所有的配置數(shù)據(jù)傳送完成,CRC校驗無誤。則DONE為高電平,否則為低電平。

DONE為高電平,F(xiàn)PGA釋放全局三態(tài)(GTS),激活I(lǐng)/O引腳,釋放全部置位復(fù)位(GSR)和全局寫使能(GWE)有效,開始執(zhí)行配置區(qū)的邏輯。

微處理器從串配置FPGA的時序如圖1所示。

2.3 配置文件的產(chǎn)生方法

利用Xilinx公司提供的開發(fā)工具ISE8.1,經(jīng)過綜合、映射、布局布線后可產(chǎn)生編程文件,編程文件含有.bit、.bin、.mcs、.tek、.hex等格式。其中,.bit格式用于JTAG下載,其他幾種格式用于專用PROM編程。首先按照產(chǎn)生專用PROM編程文件的方法來產(chǎn)生.bin文件.然后將該.bin文件轉(zhuǎn)換成ASCⅡ碼文件的存儲形式,并且各個字節(jié)之間用逗號分隔。再將該配置數(shù)據(jù)存放在系統(tǒng)程序的一個頭文件的數(shù)組config_data_array[]中,作為系統(tǒng)程序源代碼的一部分,并和其他程序一起編譯。

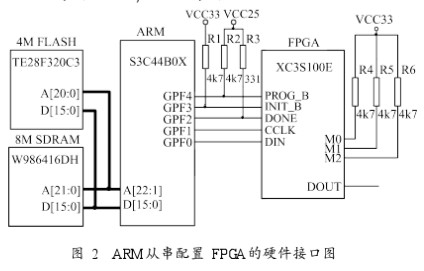

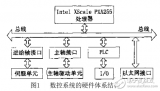

3、 硬件設(shè)計

嵌入式微處理器S3C44BOX內(nèi)置ARM7TDMI核,集成了豐富的外圍功能模塊,內(nèi)部8 kB Cache大大提高了性能。S3C44BOX可訪問256MB的地址空間,最高工作頻率達(dá)66 MHz。采用4 MBFlash作為程序存儲器,可用于存放系統(tǒng)運(yùn)行的代碼。XC3S100E從串配置程序和配置文件都固化于其中保存,該Flash支持低電壓(1.65V~3.3 V)寫操作。8MB的SDRAM是程序的運(yùn)行空間,直接運(yùn)行Flash中的代碼,但速度非常慢。通常是將Flash中的代碼移至SDRAM中。S3C44BOX與XC3S100E主要通過PROG_B、INIT_B、DONE、CCLK、DIN 5根信號線連接,如圖2所示。其中VCC33表示3.3V,VCC25表示2.5 V。

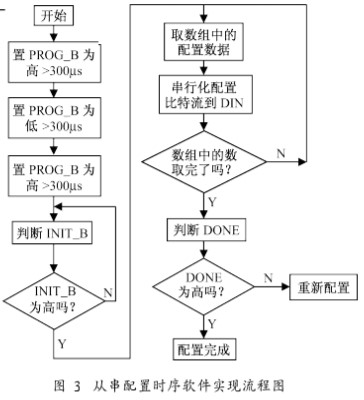

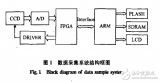

4、 軟件設(shè)計

軟件設(shè)計流程如圖3所示。配置軟件的編程要確保ARM完全按照配置信號的時序工作,關(guān)鍵問題

是采用S3C44BOX的通用I/O口GPF0、GPF1、GPF2、GPF3、GPF4模擬DIN、CCLK、DONE、INIT_B、PROG_B的時序。

在S3C44BOX中,大多數(shù)引腳都是多功能引腳,可以通過端口配置寄存器選擇相應(yīng)的引腳功能。

以端口F為例,控制寄存器rPCONF用作設(shè)定引腳的輸入、輸出或特殊功能;數(shù)據(jù)寄存器rPDATF[0:8]對應(yīng)于GPF0~GPF8引腳上的數(shù)據(jù)。讀寫寄存器rPDATF的各個位對應(yīng)于引腳的讀或?qū)憽@纾珻CLK上升沿時序是向GPF1先寫0,再寫1得到,延時程序則由for循環(huán)實(shí)現(xiàn)。

則一直循環(huán)等待

CCLK在每個上升沿把1 bit的數(shù)據(jù)置入DIN中,先將GPF1置低,在GPF0準(zhǔn)備好1 bit數(shù)據(jù),再將GPF1置高即可,以此循環(huán)將config_data_array[]中的每個字節(jié)按先低位再高位的次序?qū)懭隖PGA。

Xilinx的FPGA配置文件大小相同,與FPGA內(nèi)部邏輯設(shè)計的復(fù)雜度無關(guān)。以Spartan_3E系列的10萬門FPGA XC3S100E為例,它的配置文件固定為581 344 bit,若CCLK的時鐘周期置為2μs,配置時間約為1.2 s。

5 、實(shí)驗結(jié)果驗證

驗證環(huán)境:硬件采用自行開發(fā)的實(shí)驗板和武漢創(chuàng)維特公司的:JTAG硬件仿真器;軟件則使用Xilinx公司的開發(fā)工具ISE8.1和武漢創(chuàng)維特公司的集成開發(fā)環(huán)境ADT 1000(支持ARM7,ARM9)。

利用VerilogHDL編寫程序led.v在七段數(shù)碼管上循環(huán)顯示0~F,采用:ISE8.1編譯、綜合、映射、布局布線。生成用于編程專用PROM的led.bin文件。用一個簡單的C程序?qū)?bin文件轉(zhuǎn)換成ASCⅡ碼文件,再將ASCⅡ碼文件復(fù)制到配置數(shù)據(jù)數(shù)組config_data_array[]中,然后在ADT環(huán)境下編譯配置程序、配置數(shù)據(jù)和系統(tǒng)程序,將生成的.bin文件通過JTAG口燒寫到Flash中。重新上電后,F(xiàn)PGA配置正常,實(shí)驗結(jié)果與預(yù)設(shè)相一致。

6、 結(jié)束語

基于ARM的FPGA從串配置方案結(jié)構(gòu)簡單、接線容易、軟件編程簡單,非常適用于嵌入式系統(tǒng)設(shè)計。雖然該控制電路是為Xilinx公司Spartan-3E系列的FPGA設(shè)計的,但稍加修改也可用于其他系列FPGA器件,故具有一定的通用性。另外,由于FPGA具有可重復(fù)配置的靈活性,在嵌入式系統(tǒng)中可通過串口、網(wǎng)口遠(yuǎn)程燒寫Flash,重構(gòu)系統(tǒng)功能,這種在線重構(gòu)技術(shù)為設(shè)備的智能化在線維護(hù)、功能重組和在線升級等提供了可能,而且靈活性很強(qiáng)。本文提出的方案對數(shù)字系統(tǒng)設(shè)計具有借鑒意義,有著廣闊的應(yīng)用前景。

-

FPGA

+關(guān)注

關(guān)注

1646文章

22059瀏覽量

619118 -

ARM

+關(guān)注

關(guān)注

134文章

9361瀏覽量

378039 -

嵌入式

+關(guān)注

關(guān)注

5153文章

19707瀏覽量

318035

發(fā)布評論請先 登錄

基于ARM和FPGA的嵌入式數(shù)控系統(tǒng)設(shè)計

基于ARM的嵌入式系統(tǒng)中從串配置FPGA的實(shí)現(xiàn),不看肯定后悔

一種適用于嵌入式系統(tǒng)的模塊動態(tài)加載技術(shù)

基于ARM和DSP的嵌入式導(dǎo)航計算機(jī)方案設(shè)計

基于EmJTAG的ARM嵌入式系統(tǒng)調(diào)試工具

一種基于嵌入式系統(tǒng)和Internet的FPGA動態(tài)配置方案

基于ARM的嵌入式數(shù)控系統(tǒng)方案研究與應(yīng)用

基于FPGA的嵌入式Linux操作系統(tǒng)解決方案

基于ARM的FPGA嵌入式系統(tǒng)實(shí)現(xiàn)

ARM嵌入式系統(tǒng)

評論