H.264以其高復雜度為代價獲得了優異的編碼效率, 其中除部分控制流程的復雜模塊外,H.264中的很多模塊適合用硬件實現。應用中通常使用CPU+FPGA結構,將耗時較多的模塊用FPGA實現,CPU僅負責一些低復雜度的算法和編碼流程參數的設置。

介紹了整數變換量化的硬件實現,但沒有考慮數據在處理過程中的寬度問題,因此會造成FPGA資源的浪費。本文充分考慮了數據在處理過程中的動態范圍,使用更少的FPGA資源來實現H.264中的整數變換量化模塊。

結合實際應用,文中對該軟核在計算速度和硬件資源方面分別做了優化。經過速度優化的軟核性能明顯優于設計,經過消耗資源優化的軟核也完全能夠勝任高分辨率的實時編碼。

1 整數變換

在完成幀內和幀間預測以后,需要對圖像參差數據進行整數變換和量化,使圖像數據的能量集中到一小部分系數上,進一步降低碼流速率。

1.1 整數變換原理

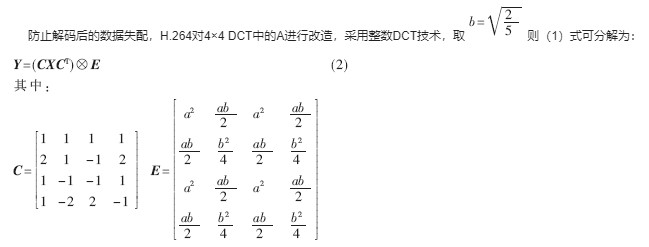

H.264中對圖像參差進行二維DCT變換,表達式為:

其中:

X為輸入數據,A為變換矩陣,Y為變換結果。H.264對4×4的圖像塊進行操作,則相應的4×4 DCT變換矩陣A為:

與E的乘法被歸納到量化運算中,這樣(CXCT)中只剩下整數的加法、減法和移位運算,因此可以大大降低硬件實現的復雜度,變換結果最多只需要16位的數據。

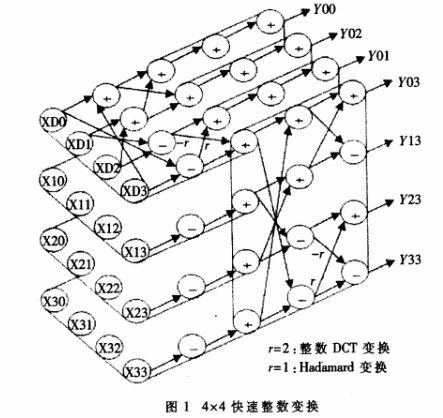

1.2 整數變換硬件結構

本設計H.264中的4×4整數變換采用蝶形快速算法,如圖1所示。首先對4×4塊的每一行做一維整數變換,然后再對行變換結果做列的一維整數變換,最終得到4×4的整數變換結果。圖1模塊需要32個加法器和32個減法器,這樣在一個時鐘周期內就可以完成一個4×4塊的整數變換。

整數變換通常的做法是全部使用16位加法器和減法器,這樣可以簡化設計。然而在實際應用中,輸入的像素點范圍是[0,255],如果第一級變換就使用16位,則數據寬度無疑會占用更多的硬件資源。根據分析可知,計算一維行變換以后,數據輸出范圍為[-765,1020],只需使用11位二進制數表示。計算一維列變換以后,數據輸出范圍是[-3 060,4 080],需要使用13位二進制數表示。因此整數變換模塊的數據寬度可以確定為:進行一維行變換時的加法器和減法器使用11位數據寬度,一維列變換的加法器和減法器使用13位數據寬度。

由于數據單向流動的特點,即沒有反饋,可以使用流水線提高系統性能。使用流水線時需要注意前后模塊處理速率的匹配。如本模塊中在行變換與列變換插入緩存構成前后模塊,前后模塊用同一時鐘,并且整個模塊的工作頻率以最低工作頻率的模塊來確定。本設計用1級流水線來提高工作頻率。如果流水線級數過多會消耗大量FPGA資源,仿真實驗證明,此模塊使用1級流水線時,只增加極少FPGA資源。

2 量化

為了進一步降低圖像傳輸碼率,需要對圖像進一步壓縮,方法是使用變換編碼及量化技術。

2.1 量化原理

H.264中采用標量量化器。標量量化器的原理是:

其中,y為輸入樣本點編碼,Qstep為量化步長,FQ為y的量化值。H.264標準支持52個量化步長。量化的簡化操作如下:

其中,Wij為輸入樣本點編碼,MF是標準中定義的值,QP為量化系數,f為偏移量,對幀內預測圖像塊f取2qbits/3,對幀間預測圖像塊f取2qbits/6。

2.2 量化器實現

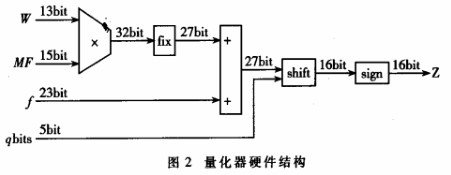

量化器硬件結構如圖2所示,其結果是實現對式(4)和式(5)的組合電路。W是需要量化的數據,MF是根據QP和當前點位置在查找表中得到的值。f和qbits是根據QP查表的輸出。

為了硬件資源消耗最少,需要分析數據在計算過程中的動態范圍,使用最少的數據寬度來表示傳輸的數據,從而使用最少的硬件資源來實現組合運算邏輯。W是整數變換結果,根據整數變換部分的分析,其取值范圍是[-3 060,4 080],MF最大取13 107,乘法器輸出動態范圍是[-40 107 420,53 476 560],至少用27位二進制數表示。本量化器的乘法器使用Vetex-Ⅱ中的18×18硬件乘法器,因此在輸入加法器之前需要將數據寬度調整為27bit。加法器輸出的27位數據通過移位模塊調整為16位數據寬度。

綜合考慮工作頻率和資源占用率,設計中使用2級流水線來提高性能。

2.3 量化器優化

本量化器一次只能量化一個點,無法滿足高質量圖像編碼的要求。針對高質量圖像編碼對此量化器進行速度優化,即將n個量化器并聯,一個時鐘周期計算n個點。n根據實際需要進行選擇。考慮到與變換模塊的速度匹配,選擇16個量化器并聯。

3 軟核設計及測試

3.1 PLB總線的軟核結構

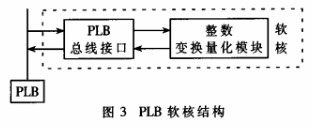

PLB(Processor Local Bus)總線是IBM開發的一種高性能片上總線,主要應用于PowerPC405處理器系統中,它支持32位、64位和128位數據寬度。本設計使用64位總線寬度,最大速據傳輸速率達800Mb/s。

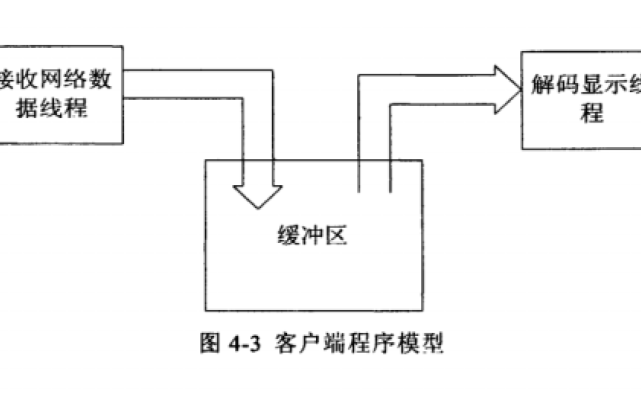

如圖3,PLB的軟核設計分為總線接口和H.264整數變換量化模塊兩部分。PLB總線接口是與硬件體系結構相關的部分,它是整數變換量化模塊與PLB總線上其他設備進行交互的橋梁。整數變換量化模塊與體系結構無關,它也可以被移植到ARM體系結構中。

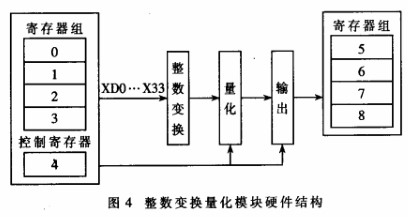

整數變換量化模塊的硬件結構如圖4。寄存器組包含9個32bit的寄存器,0、1、2、3為輸入的4×4參差數據寄存器;5、6、7、8為輸出數據寄存器;4為控制寄存器,包括go、done、reset、intra、DCT、ZSCAN、QP、datacount,分別對應啟動、完成、復位、幀內/幀間、DCT/Hadamard變換、Z掃描輸出、量化級數、數據輸出計數器。第二個模塊對寄存器組中數據進行4×4整數變換,使用1級流水線。第三個模塊對輸入的整數變換結果按QP進行量化,量化模塊中的MF、f、qbits使用FPGA中的查找表保存。數據輸出模塊受ZSCAN位控制,當ZSCAN=1時,輸出數據寄存器中的數據按Z掃描排列;ZSCAN=0時,按矩陣排列。

3.2 軟核的測試

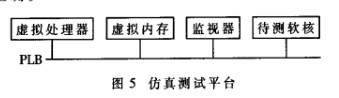

首先使用IBM的CoreConnect工具和Modelsim6.0a來仿真設計的軟核并使用虛擬平臺進行測試,仿真的目的是保證PLB總線接口能被處理器正確訪問。仿真測試平臺結構如圖5所示。通過虛擬處理器將虛擬內存中的數據寫入待測軟核,然后讀取待測軟核中的數據并判斷是否正確。

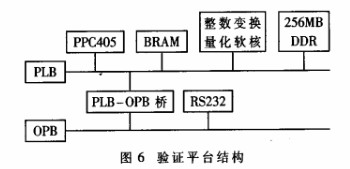

仿真通過以后,再將軟核集成到系統中,以便驗證軟核在實際系統中的工作是否符合要求。驗證平臺系統結構如圖6,軟核驗證使用PC機和目標板相結合的方法,目標板使用Xilinx公司XUP Virtex-II PRO開發板,內部含有兩個PowerPC內核。

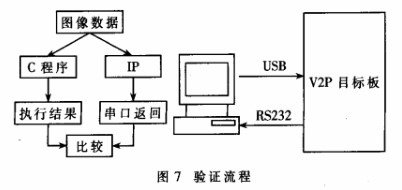

驗證流程如圖7。首先通過USB口下載目標板程序,程序開始運行以后通過RS232從上位機下載待編碼的圖像參差數據,下載的數據保存在目標板上的256MB DDR SDRAM中。數據下載完畢后,程序將待編碼數據依次寫入軟核并啟動轉換,并將計算完的數據寫入DDR SDRAM,待全部數據編碼完畢,PowerPC將處理結果一起發送給上位機。上位機將結果與本機C代碼執行結果相比較,最終確認軟核是否正確工作。

4 綜合結果分析

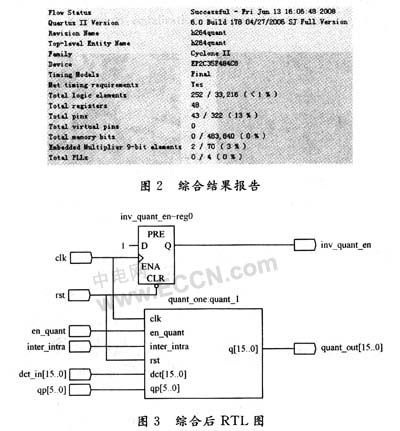

本設計中的整數變化量化模塊在Xilinx的XC2VP30 FPGA中進行綜合。XC2P30含有13 696個Slices和136個18×18乘法器。綜合工具使用Xilinx的ISE9.1。

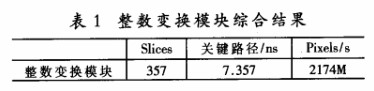

整數變換模塊綜合結果如表1。

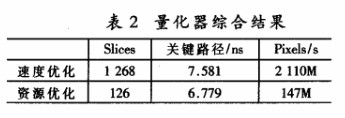

對量化器在速度和硬件資源上分別做了優化,表2給出了兩種優化的綜合結果。

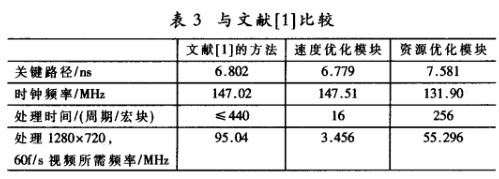

表3給出本設計整數變換量化模塊與文獻[1]的比較結果。對照發現速度優化軟核編碼性能遠遠高于文獻[1]的設計,資源優化的軟核性能也略高于文獻[1]的設計。

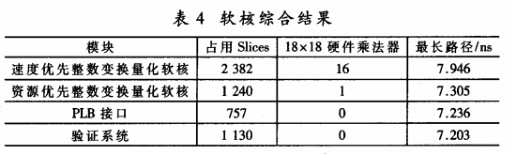

軟核綜合結果如表4。目前該軟核中的PLB接口部分資源占用較大,后續工作對這部分進一步優化。

本文將H.264中的整數變換量化與微處理器系統相結合,針對不同的應用場合實現了兩個基于PLB總線的H.264 整數變換量化軟核,并在Xilinx XUP Virtex-II PRO開發板中做了驗證。實驗結果表明,兩個軟核均能在系統中穩定工作,并能滿足不同分辨率的實時應用。

-

FPGA

+關注

關注

1630文章

21759瀏覽量

604359 -

微處理器

+關注

關注

11文章

2271瀏覽量

82571 -

總線

+關注

關注

10文章

2891瀏覽量

88179

發布評論請先 登錄

相關推薦

基于Blackfin533的H.264編碼

基于FPGA的H.264去塊濾波系統的優化設計

H.264視頻編碼在DM642上的實現與優化

基于TMS320DM642平臺的H.264編碼器優化

基于H.264逆量化IP的硬件實現

H.264/AVC中量化的Verilog方法介紹及實現

H.264視頻編碼器在DM6437上的優化實現

基于FPGA的H.264 DCT算法的硬件實現

基于FPGA硬件實現H.264變換量化整體結構的設計方案

如何在Linux下實現H.264解碼器的優化

利用PLB總線和FPGA技術對H.264整數變換量化軟核實現優化設計

利用PLB總線和FPGA技術對H.264整數變換量化軟核實現優化設計

評論