光柵位移傳感器是基于莫爾條紋測量的一種傳感器,要提高其測量分辨率,對光柵輸出信號進行細分處理是必要環節.在實際應用中,通常采用四倍頻的方法提高定位精度.四倍頻電路與判向電路設計為一個整體,稱為四倍頻及判向電路。能夠實現四倍頻的電路結構很多,但在應用中發現,由于某些四倍頻電路的精度或穩定性不高,使傳感器整體性能下降.作者在分析幾種常見四倍頻電路的基礎上,針對不同的應用,設計了兩種不同的四倍頻電路實現方案,并對這兩種方案的結構和使用方法進行了比較和仿真.

1 四倍頻電路設計原理

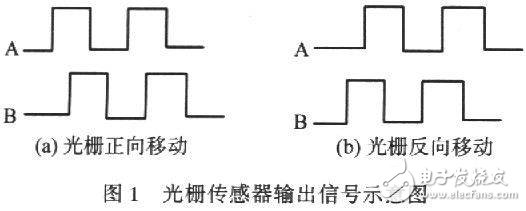

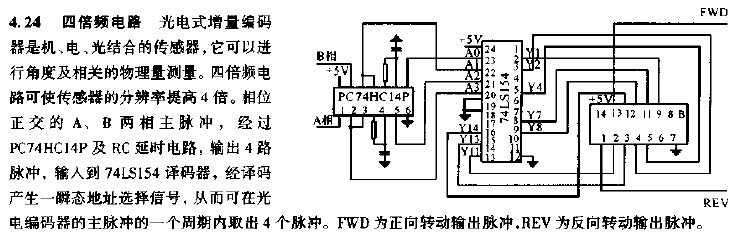

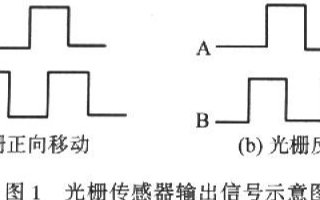

光柵傳感器輸出兩路相位相差為90的方波信號A和B.如圖l所示,用A,B兩相信號的脈沖數表示光柵走過的位移量,標志光柵分正向與反向移動.四倍頻后的信號,經計數器計數后轉化為相對位置。計數過程一般有兩種實現方法:一是由微處理器內部定時計數器實現計數;二是由可逆計數器實現對正反向脈沖的計數.

光柵信號A,B有以下關系.

①當光柵正向移動時,光柵輸出的A相信號的相位超前B相90,則在一個周期內,兩相信號共有4次相對變化:00→10→11→01→00.這樣,如果每發生一次變化,可逆計數器便實現一次加計數,一個周期內共可實現4次加計數,從而實現正轉狀態的四倍頻計數.

②當光柵反向移動時,光柵輸出的A相信號的相位滯后于B相信號90,則一個周期內兩相信號也有4次相對變化:00→01→11→10→00.同理,如果每發生一次變化,可逆計數器便實現一次減計數,在一個周期內,共可實現4次減計數,就實現了反轉

狀態的四倍頻計數.

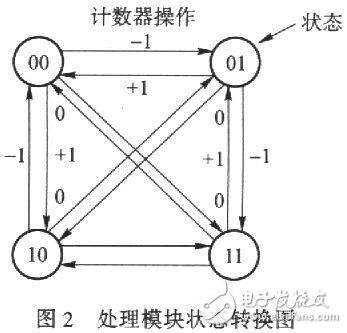

③當線路受到干擾或出現故障時,可能出現其他狀態轉換過程,此時計數器不進行計數操作.

綜合上述分析,可以作出處理模塊狀態轉換圖(見圖2),其中“+”、“-”分別表示計數器加/減1,“0”表示計數器不動作.

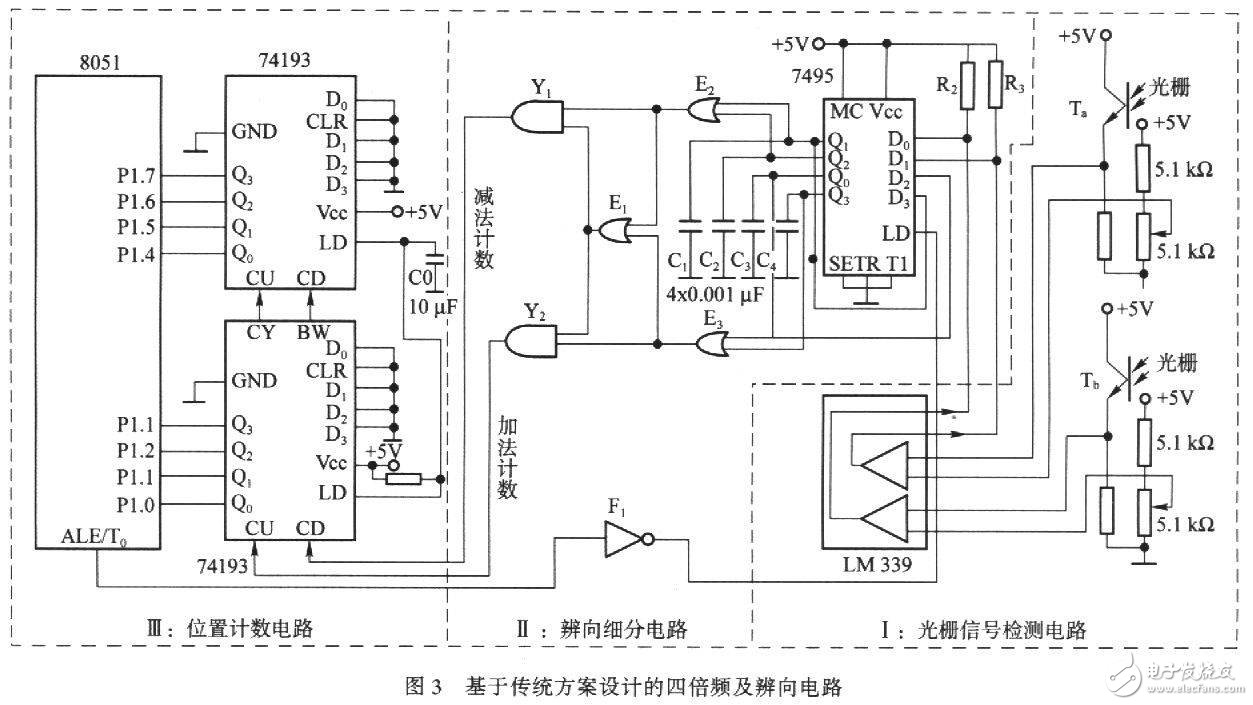

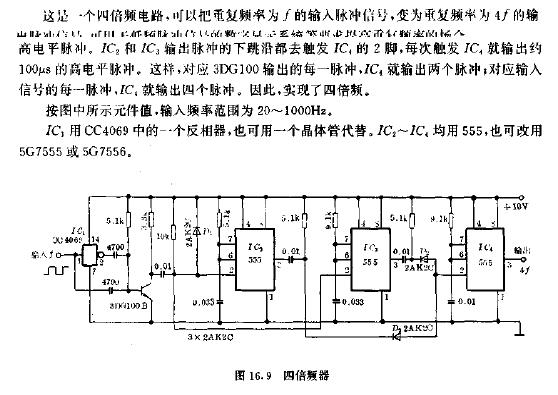

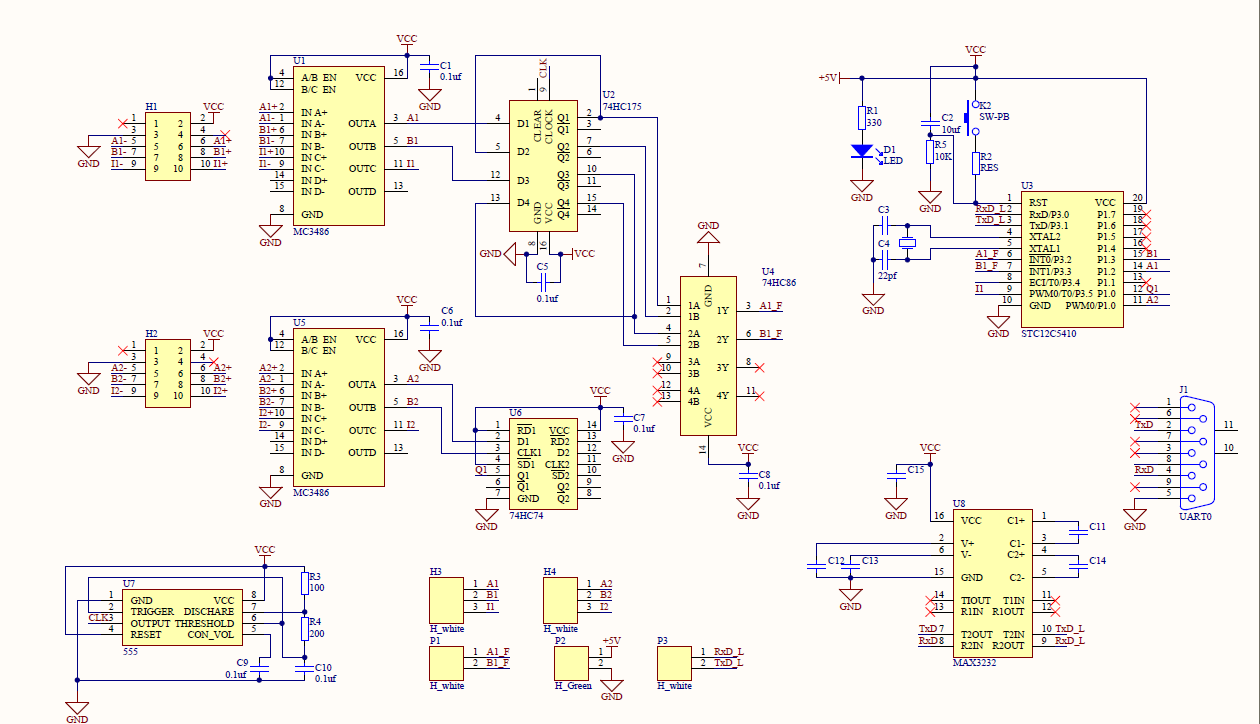

2 傳統模擬細分電路

傳統的倍頻計數電路如圖3所示,它由光柵信號檢測電路,辨向細分電路,位置計數電路3部分組成.光柵信號檢測電路由光敏三極管和比較器LM339組成.來自光柵的莫爾條紋照射到光敏三極管Ta和Tb上,它們輸出的電信號加到LM339的2個比較器的正輸入端上,從LM339輸出電壓信號Ua,Ub整形后送到辨向電路中.芯片7495的數據輸入端Dl接收Ua,D0接收Ub,接收脈沖由單片機的ALE端提供.然后信號經過與門Y1,Y2和或門E1,E2,E3組成的電路后,送到由2片74193串聯組成的8位計數器.單片機通過P1口接收74193輸出的8位數據,從而得到光柵的位置.

采用上述設計方案,往往需要增加較多的可編程計數器,電路元器件眾多、結構復雜、功耗增加、穩定性下降.

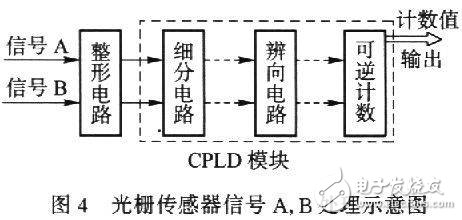

3 基于CPLD實現的光柵四細分、辨向電路及計數器的設計

采用CPLD實現光柵傳感器信號的處理示意圖如圖4所示,即將圖3中3個部分的模擬邏輯電路全部集成在一片CPLD芯片中,實現高集成化。由于工作現場的干擾信號使得光柵尺輸出波形失真,所以將脈沖信號通過40106施密特觸發器及RC濾波整形后再送入CPLD,由CPLD對脈沖信號計數和判向,并將數據送入內部寄存器.

3.1 CPLD芯片的選擇

CPLD芯片選用ALTERA公司的MAX7000系列產品EPM7128S,該芯片具有高阻抗、電可擦、在系統編程等特點,可用門單元為2 500個,管腳間最大延遲為5μs工作電壓為+5 V.仿真平臺采用ALTERA公司的QUARTUSⅡ進行開發設計.

3.2 四細分與辨向電路

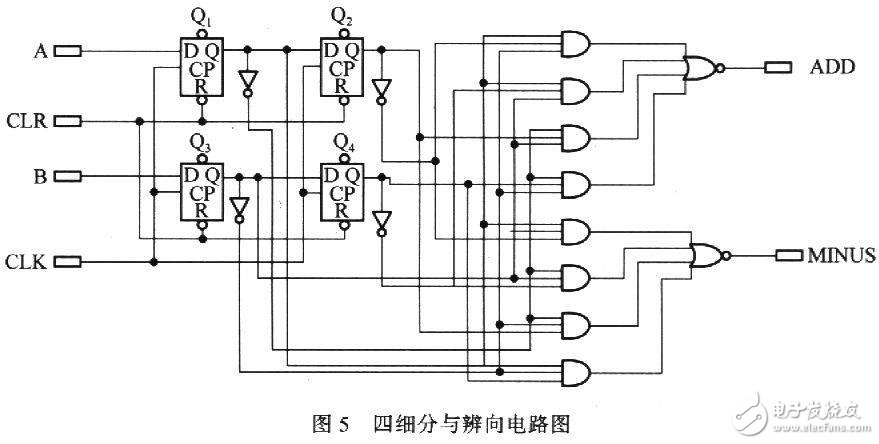

四細分與辨向模塊邏輯電路如圖5所示,采用10MB晶振產生全局時鐘CLK,假設信號A超前于B時代表指示光柵朝某一方向移動,A滯后于B時表示光柵的反方向移動.A,B信號分別經第一級D觸發器后變為A',B'信號,再經過第二級D觸發器后變為A″,B″信號.D觸發器對信號進行整形,消除了輸入信號中的尖脈沖影響,在后續倍頻電路中不再使用原始信號A,B,因而提高了系統的抗干擾性能.在四倍頻辨向電路中,采用組合時序邏輯器件對A'A″,B'B″信號進行邏輯組合得到兩路輸出脈沖:當A超前于B時,ADD為加計數脈沖,MIMUS保持高電平;反之,當A滯后于B時,ADD保持高電平,MINUS為減計數脈沖.

對比圖5和圖2可以看出,新型設計方法使用的器件數較傳統方法大大減少,所以模塊功耗顯著降低。系統布線在芯片內部實現,抗干擾性強。由于采用的是可編程邏輯器件,對于系統的修改和升級只需要修改相關的程序語句即可,不用重新設計硬件電路和制作印刷電路板,使得系統的升級和維護的便捷性大大提高。

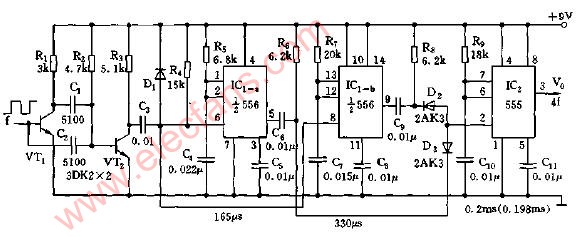

4 四倍頻細分電路模塊的仿真

根據圖2所示的狀態轉換圖,利用硬件描述語言Verilog HDL描述該電路功能,編程思想為將A,B某一時刻的信號值的狀態合并為狀態的判斷標志state,并放入寄存器prestate.當A,B任一狀態發生變化時,state值即發生改變,將此時的state值與上一時刻的prestate進行比較,則能根據A,B兩個脈沖的狀態相對變化確定計數值db的加減,得出計數器輸出值的加減標志.

仿真結果如圖6所示.當信號A上跳沿超前于B時,計數值db進行正向計數;當A上跳沿滯后于B時,計數值db進行反向計數.即db將細分、辨向、計數集于一身,較好地實現了光柵細分功能.

比較圖3和圖5可以看出,用FPGA設計信號處理模塊,設計過程和電路結構更加簡潔。另外,在應用中需注意FPGA時鐘周期應小于光柵信號脈沖的1/4.

5 結論

①新型設計方法結構簡單,集成度高,比傳統設計方法所用器件數大大減少.

②集成化設計使系統功耗降低,抗干擾性增強.

③用Verilog HDL設計電路,改變電路結構只需修改程序即可,且系統維護和升級的便捷性提高.

-

傳感器

+關注

關注

2550文章

51038瀏覽量

753086 -

芯片

+關注

關注

455文章

50719瀏覽量

423164 -

三極管

+關注

關注

142文章

3611瀏覽量

121877

發布評論請先 登錄

相關推薦

光柵位移傳感器中四倍頻細分電路模塊的設計與仿真研究

光柵位移傳感器中四倍頻細分電路模塊的設計與仿真研究

評論