HSDI(High Speed Direct Injection)是一種可配置的高速數據接口。例如,德州儀器公司生產的集成式1394a鏈接層控制器與艤端口物理層控制器TSB43DA42和TSB43DB42分別包括3個高速數據端口(HSDI)。每個端口均支持數據I/O,能專門負責一個同步數據路徑,所有端口都支持與各種編解碼器的無縫連接,能夠根據IEC61883標準實現壓縮的A/V數據與數字音頻的傳輸。還有就是Freescale公司計劃開發的UWB系列產品。這些UWB網卡符合美國聯邦通訊委員會(FCC)現行擬定的UWB標準,支持多種操作系統;同時,這些產品將擁有mini-PCI和SDIO模組外形結構,并且,還將具有PCI、mini-PCI、HSDI、PCI-Express、USB 2.0和IEEEl394等各種界面。下面就Freescale公司的一種UWB網卡上的HSDI接口作一介紹。

MC270143 MAC是Freescale公司UWB網卡XSllO上的一部分。它直接與基帶控制器MC270123相連,當和MC270123控制器以及MC270113 RF發送器結合使用時,可以提供一種完全端到端的WPAN/WLAN芯片集解決方案,并具備低成本、低功耗和高速數據傳輸速率。

由于Freescale公司的UWB網卡遵循IEEE 802.15.3網絡層協議標準,那么對于其上的HSDI接口,從主機來說,遵循IEEE 802.15.3協議標準的請求和響應消息是從HSDI的A口輸入的,而確認和指示消息是從HSDI的B口輸出給當地主機的;通過空中鏈路去往另一個UWB設備的數據信息,從HSDI的A口進入,另一個UWB設備從B口輸出。在HSDI并行接口中,是以字節為單位來傳輸數據的,并且字節與字節之間沒有延時。

1 HSDI接口硬件結構

圖1為Freescale公司XSIlO網卡上MC270143模塊的HSDI接口硬件結構框圖。

①HSDI A和HSDI B用于傳輸高速數據流或者命令和控制信號,它們支持傳輸同步或異步的數據流以及命令消息和相關的響應消息。HSDI A只能配置成輸入接口,HSDI B只能配置成輸出接口。HSDIA和HSDI B都是由8位并行端口和輸入時鐘以及相關控制信號組成的。

②每個FIFo的容量為512×32位。

③O_hsdiahalt信號用來阻止數據從HSDI A接口輸入,O_hsdiahaltxin信號產生后MC270143最多還可以接收16字節的數據。也就是說,外部時鐘必須在16個時鐘周期之前產生O_hsdiahalt。

④任何從MC270143接收輸出數據的設備必須能夠在產生I_hsdibhalt后再接收至少1 6字節的數據,也可配置MC270143上的HSDI B模塊忽略產生I_hsdibhalt信號。

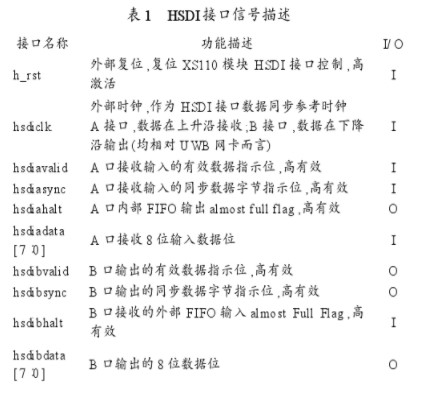

2 HSDl接口信號描述

整個XSll0模塊的外部接口主要為:輸入是天線部分,輸出是HSDI接口。接口(相對UWB網卡而言)說明如表l所列。

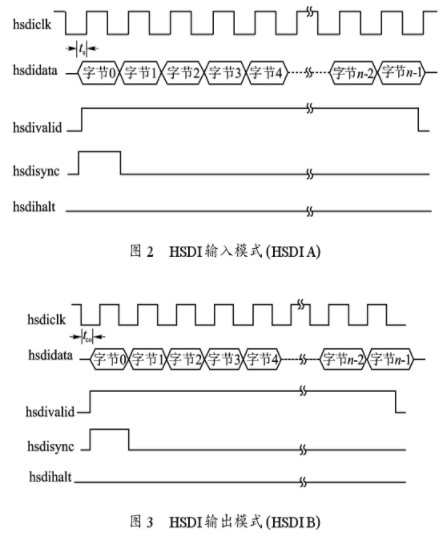

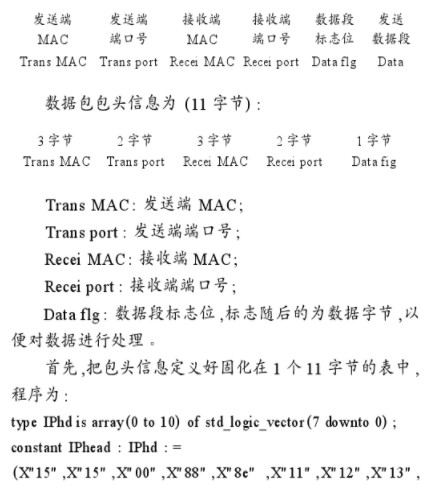

HSDI接口可以配置成發送和接收定長/可變長度的數據包。定長數據包模式包括HSDI輸入模式(HSDI A)和HSDI輸出模式(HSDI B):所有輸入到HSDI接口的數據都是在hsdiclk的上升沿采樣輸入;輸出數據在hsdi-clk的下降沿輸出。相應的時序圖如圖2和圖3所示。

說明:在定長和可變長數據包類型下,HSDI接口信號描述是相同的;惟一的不同在于,在可變長模式下,hsdisync信號與最后一個有效字節對齊,而在定長模式下與第一個有效字節對齊。

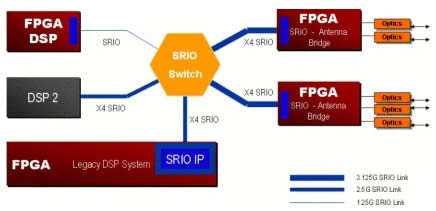

3 基于FPGA實現HSDI接口的設計

利用FPGA硬件處理速率高的特點,通過普通數據包的發送可實現發送端HSDI接口的設計,并把數據通過HSDI接口發送到UWB網卡,再由UWB網卡發送出去,隨后由另外的UWB網卡接收相應的數據。

發送端FPGA負責把數據打包并生成相應的數據有效信號和同步信號,然后通過HSDI接口發送給UWB網卡。FPGA與HSDI的接口定義如圖4所示。

4 打包發送模塊程序設計

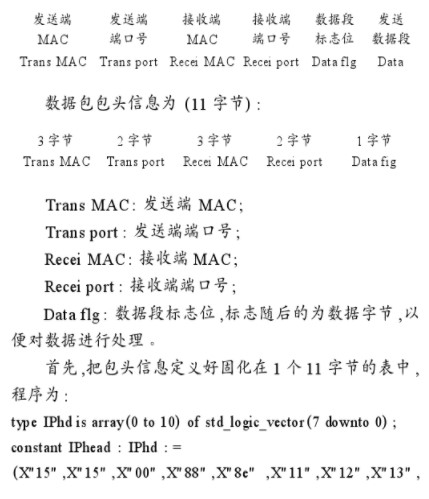

由于USB網卡遵循IEEE 802.15.3網絡層協議標準,考慮到發送端和接收端.做簡單的應用層協議如下:

其次,按照HSDI傳輸格式,可以確定的是在發送hsclivalid、hsdisync、hsdidata信號的時候要用lasdiclk的下降沿送出,以保證網卡的正確采樣。(VHDL程序見本刊網站www.mesnet.com.cn——編者注)

①hsdidata數據信號的生成:將發送包的包頭信息存放在一個固化的小表里(內部的自建存儲器)。數據的打包發送主要由2個與時鐘同步的計數器datacntl和datacnt2(hsdiclk下降沿產生)控制。datacntl為4位,控制發送11位包頭信息,根據不同計數器的值決定發送包頭信息位數據。發送到最后1位包頭信息時。啟動datacnt2計數,開始發送包數據,且發送的數據和計數器datacnt2的值是相等的,以確保接收端檢測數據傳輸的正確性。

②hsdivalid信號的生成:由datacnt2來控制。hsdi-valic初始化為0,在計數器datacnt2記到x“FF”時為0,其他情況下為l即可標志一個包的有效數據位。

③hsdisync信號的生成:由datacntl來控制。hsdi-sync韌始化為0,由于采用的是定長數據包模式,所以在計數器記到x“00”時為1,標志包數據的第1位,其他情況下為0。modelsim仿真得到的時序如圖5所示。QuartusⅡ仿真結果如圖6所示。

5 結論

本文詳細討論了HSDI接口的硬件結構以及接口信號的時序和功能操作。結合FPGA高處理速度的特點,實現了基于FPGA的HSDI接口設計,最后結合實例成功地進行了仿真和驗證,并在實際硬件平臺上實現了發送和接收解析數據包。

-

FPGA

+關注

關注

1630文章

21761瀏覽量

604442 -

芯片

+關注

關注

456文章

50967瀏覽量

424940 -

控制器

+關注

關注

112文章

16404瀏覽量

178638

發布評論請先 登錄

相關推薦

基于FPGA的高速數據采集系統接口設計

基于FPGA的高速數據采集系統該怎么設計?

利用FPGA怎么實現數字信號處理?

FPGA的高速數據處理系統結構和硬件設計

利用FPGA平臺解決接口的速度瓶頸

利用FPGA 實現與TS201 的LinkPort 高速數據

利用串行RapidIO實現FPGA協處理

基于SRIO協議設計和實現了DSP與FPGA之間的高速數據通信

利用FPGA硬件處理速度性能實現HSDI高速數據接口的設計

利用FPGA硬件處理速度性能實現HSDI高速數據接口的設計

評論