目前,以太網802.3協議和TCP/IP協議是現今嵌入式系統接入Internet的首選協議。而以太網(Ethernet)的核心思想是多用戶使用共享的公共傳輸信道,它通過帶沖突檢測的載波偵聽多路訪問協議(CSMA/CD)來控制對介質的訪問。

本文給出了完全用FPGA的控制邏輯來實現嵌入式系統Internet接人中的底層以太網控制器的設計方法。并最終設計出符合IEEE 802.3標準的控制器,從而實現了10 Mbps和100 Mbps兩種傳輸速率以及半雙工和全雙工兩種工作模式,并可通過IEEE802.3標準定義的介質獨立接口(MII)與以太網物理層芯片相連接。

1 總體設計方案

以太網控制器的FPGA設計工作包括以太網MAC子層的FPGA設計、MAC子層與上層協議的接口設計以及MAC與物理層(PHY)的MII接口設計。

該以太網控制器的總體結構設計框圖如圖1所示。整個系統分為發送模塊、接收模塊、MAC狀態模塊、MAC控制模塊、MII管理模塊和主機接口模塊六部分。發送模塊和接收模塊主要提供MAC幀的發送和接收功能,其主要操作有MAC幀的封裝與解包以及錯誤檢測,它直接提供了到外部物理層芯片(PHY)的并行數據接口(MII)。MAC控制模塊則用于執行全雙工模式中的流量控制功能。MAC狀態模塊可用來監視MAC的操作過程的各種狀態信息,并作修改。MII管理模塊提供了標準的IEEE 802.3介質獨立接口(MII),可用于連接以太網的鏈路層與物理層(PHY)。主機接口則提供有以太網控制器與上層協議(如TCP/IP協議)之間的接口,以用于數據的發送、接收以及對控制器內各種寄存器(控制、狀態和命令寄存器)的設置。

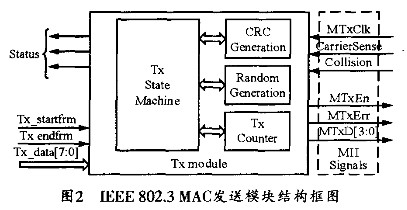

2 MAC發送模塊

MAC發送模塊可將上層協議提供的數據封裝之后通過MII接口發送給PHY。發送模塊可接收主機接口模塊的數據幀開始和數據幀結束標志,并通過主機接口從外部存儲器中讀取要發送的數據,然后對數據進行封裝,然后通過PHY提供的載波偵聽和沖突檢測信號,在信道空閑時通過MII接口將數據以4位的寬度發送給PHY,最后由PHY將數據發送到網絡上。

發送模塊由CRC生成模塊(crc_gen)、隨機數生成模塊(random_gen)、發送計數模塊(tx_cnt) 和發送狀態機(tx_statem_模塊等四個子模塊組成。

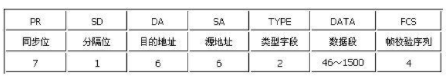

2.1 CRC生成模塊(crc_gen)

該模塊用于計算發送數據的CRC值,并將CRC值添加到數據幀的幀校驗序列字段(FCS)內。為了提高效率,并考慮到MAC與PHY的數據通道為4位,設計時可采用4位并行CRC計算方法,算法中可使用一個次態函數,并通過循環迭代來模擬移位操作。這樣,發送模塊就可以在邊發送數據到PHY的同時,一邊計算CRC,這樣當數據發送完時,CRC值也計算完成了。

2.2 隨機數生成模塊(random_gen)

如在發送過程中檢測到沖突,發送模塊就先發送擁塞碼(jam),隨后停止發送。在下次重新發送之前,發送模塊會先執行一個后退(backoff)操作,即發送模塊等待一個半隨機(生成的隨機數有范圍限制)的時間之后再開始發送。該隨機數就是由隨機數生成模塊產生的,它采用經典的截斷二元指數后退算法,后退的時間是一個與發生沖突次數有關的隨機數,隨著沖突的次數增多,用于生成該隨機數的范同也將逐漸增大,以減少沖突的概率。

2.3 發送計數模塊(tx_cnt)

發送計數模塊由半字節計數器(nibcnt)、字節計數器和重試次數計數器(retrycnt)三個計數器組成。其中重試次數計數器(retrycnt)可對發送某個幀時產生沖突次數進行計數。當計數器的值達到最大重試次數時,它將放棄重試,并丟棄發送緩沖器內的數據。同時,重試計數器的值還被隨機數生成模塊用于計算下次重試之前需要后退(backoff)的時隙的個數。

半字節計數器和字節計數器分別用于對發送過程中的半字節(bibble)和字節進行計數。

信道忙時,發送模塊會一直等待,半字節計算器一直計數。當計數到額定等待時間時(最大幀長度的兩倍,即3036字節時間),系統會根據設置放棄發送或是一直等待(可選功能)。一旦信道空閑再進入幀間間隙周期(≥96個比特時間),南半字節計數器從零開始計數。幀間間隙分為兩個部分,在前2/3個周期中,如果檢測到信道忙信號,則半字節計數器復位,發送模塊重新開始等待;在后l/3周期中,即使檢測到信道忙信號,半字節計數器也不會復位,而是繼續計數,以保證每個站點公平的競爭信道。而當半字節計數器的值達到幀問間隙周期時,此時如果有數據等待發送,發送模塊就開始發送數據。此外,半字節計算器還用于前序碼的生成和短幀的判斷,在數據幀的長度小于最小幀時,發送模塊必須根據系統設置進行填充或不填充。

字節計算器還可用于滯后沖突(late collision)和超長幀的判斷。當滯后沖突發生時,正在發送的數據將被丟棄。超長幀的判斷則是從對幀內容(包括FCS)進行字節計數,如果字節計數器的值大于最大有效幀的長度(1518個字節),發送模塊就根據系統設置(是否支持超長幀)丟棄或發送。

2.4 發送狀態機模塊(tx_statem)

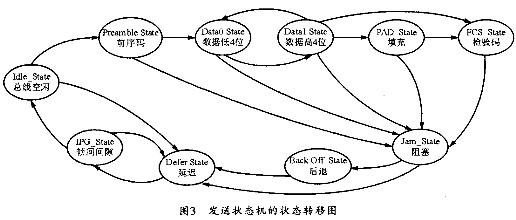

發送狀態機模塊是整個發送模塊的核心,主要用于控制整個發送過程。發送狀態機由I-die_State、Preamble_State、 Data0_State、 Da-tal_State、 PAD_State、 FCS_State、 IPG_State、Jam_State、BackOff_State、Defer_State等十個狀態組成。

系統復位后,發送模塊即進入Defer_State狀態,并一直檢測載波偵聽(CarrierSense)信號。當載波偵聽信號變成無效(表示信道空閑)時,狀態機進人IPG_State狀態。爾后,在等待一個幀間間隙之后,狀態機則進入Idle_State狀態。如果在幀間間隙的前2/3個周期檢測到信道忙信號,狀態機將重新回到Defer_State狀態。

狀態機進入Idle_State狀態之后,發送模塊將檢測載波偵聽信號和主機接口的發送請求。若主機模塊請求發送,狀態機將進入Preamble_State狀態,發送模塊即通知PHY發送開始,同時開始發送前序碼(7個0x5),然后發送幀起始定界符(SFD,0xd)。狀態機進入Data0_State后,發送模塊將發送一個數據字節的低4位(LSB nibble),將當其進入Data1_State狀態后,發送模塊則發送數據字節的高4位(MSB nibble)。隨后,狀態機一直在data0和data1之間循環,直到數據發送完畢。當還剩一個字節時,主機模塊將通過發送幀結束信號來通知發送模塊。如果數據幀的長度大于最小幀并且小于最大幀,狀態機就進入FCS_State狀態,此時發送模塊則將CRC生成模塊生成的CRC值添加到幀的FCS字段中并發送給PHY。幀發送完之后,狀態機進入Defer_State狀態,之后是IPG_State和Idle_State狀態。此后狀態機又回到初始狀態,以重新等待新的發送請求。

如果數據幀的長度小于最短幀,狀態機就進入PAD_State狀態,發送模塊根據系統設置是否在數據之后來添加填充碼。然后,狀態機進入FCS_State狀態。如果數據幀的長度大于最大幀,而系統設置又支持發送超長幀,那么,狀態機就進入FCS_State狀態;如果不支持發送超長幀,發送模塊將放棄發送,狀態機直接進入Defer狀態,然后是IPG狀態,最后回到Idle狀態。

在發送數據的過程中,發送模塊會一直檢查沖突檢測信號(collision detected)。如果發現沖突且狀態機正處于Preamble_State,狀態機將在發送完前序碼和SFD之后進入Jam_State,并發送擁塞碼,然后進入BackOff狀態,以等待重試。之后,狀態機經過Defer和IPG回到Idle狀態。如果此時重試次數計數器的值沒有達到額定值,發送模塊將重新開始發送剛才的幀,并將重試次數計數器的值加1;如果發現沖突且狀態機處于data0、da-tal或FCS狀態,而且沒有超過沖突時間窗,那么狀態機將馬上進入Jam狀態發送擁塞碼,之后經過BackOff、Defer、IPG、回到Idle,并根據重試計數器的值決定是否重新發送剛才的數據幀;如果檢測到發生沖突的時間超過了沖突時間窗,狀態機將進入Defer狀態,然后經過IPG到IDLE狀態,并放棄重試。

在全雙工模式中發送幀時,不會進行延遲(defer),發送的過程中也不會產生沖突。此時,發送模塊將忽略PHY的載波偵聽和沖突檢測信號。當然,幀與幀之間仍然需遵守幀間間隙的規則。因此,全雙工模式下的發送狀態機沒有Jam_State、。BackOff_State、Defer_State三個狀態。

3 MAC接收模塊

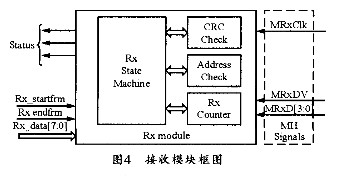

MAC接收模塊負責數據幀的接收。當外部PHY將通信信道的串行數據轉換為半字節長的并行數據并發送給接收模塊后,接收模塊會將這些半字節數據轉換為字節數據,然后經過地址識別、CRC校驗、長度判斷等操作后,再通過主機接口寫入外部存儲器,并在主機接口模塊的接收隊列中記錄幀的相關信息。此外,接收模塊還負責前序碼和CRC的移除。

接收模塊由CRC校驗模塊、地址識別模塊、接收計數器模塊和接收狀態機模塊等四部分組成。

接收模塊中的CRC校驗模塊可通過檢查輸入幀的CRC值來驗證幀的正確性。其算法與CRC生成模塊相同。

地址識別模塊用于決定是否接收收到的幀,接收模塊首先接收輸入幀而不管目的地址,隨后由地址識別模塊檢查幀中的目的地址。若MAC被設置為混雜模式(Promiscuous mode)且目的地址為廣播地址,同時允許接收廣播幀,幀則被接收。否則,幀被丟棄。

接收計數器模塊由字節計數器(Bytecnt)和幀間間隙計數器(IFGcnt)組成。字節計數器在接收幀過程中將對字節進行計數,以用于識別幀中的各個字段(前序碼、目的地址字段、數據、FCS等)以及判斷超長幀。幀間間隙計數器則對兩幀之間的間隔時間進行計數,以用于判斷下一幀數據的開始。IEEE 802.3規定,兩幀之間的間隔至少必須為96個比特時間(10 Mbps中為9 600ns,100 Mbps中為960 ns)。如果兩幀之間的間隔小于要求,幀將被丟棄。

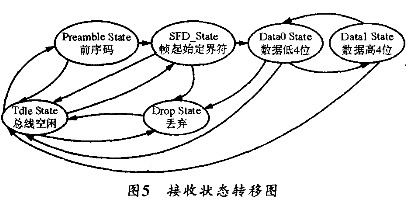

接收狀態機為接收模塊的核心,用于控制整個接收過程。接收狀態機由Idle_State、Drop_State、Preamble_State、 SFD_State、 Da-ta0_State、Data1_State等六個狀態組成。

系統復位后,狀態機處于Drop_State。如果此時MII的數據有效信號(MRxDV)無效,狀態機馬上進入Idle_State狀態,并一直處于Idle等待接收輸入幀。

當接收模塊檢測到數據有效信號之后,狀態機將進入Preamble_State,并開始接收前序碼。此后再狀態機進入SFD_State,接收一個字節的幀起始定界符,之后,根據IFGcnt計數器的值進入不同的狀態。如果,IFGcnt所確定的時間大于96個比特時間,狀態機將進入Data0狀態以接收字節的低4位,然后是Data1狀態,并接收字節的高4位,之后又回到Data0狀態。狀態機就一直在這兩個狀態之間循環,直到數據接收完畢(PHY清除MRxDV信號)后進入Idle,以重新等待接收新的數據;如果接收到幀起始定界符時,IFGcnt計數器所確定的時間小于96個比特時間,那么狀態機將進入Drop_State狀態,并一直維持該狀態直到數據有效信號結束(PHY清除MRxDV信號)。之后,狀態機再同到Idle等待接收新的數據。

如果在接收前序碼、幀起始定界符和數據期間,數據有效信號被清除,那么,狀態機將回到Idle。

4 MAC的其它模塊

4.1 MAC狀態模塊

在接收過程的狀態信息中,接收錯誤表明PHY在接收過程中檢測到了錯誤;接收到無效符號則表明接收到的幀中包括無效(PHY無法識別)的符號;滯后沖突表明接收幀時檢測到滯后沖突信號;超短幀表明接收到的幀小于最短有效的長度;超長幀表明接收到的幀大于最大有效幀的長度;半字節對齊錯誤表明接收到的半字節不是偶數(即幀的長度不是字節的整數倍);接收溢出則表明接收模塊來不及處理接收到的數據而導致接收FIFO溢出。

在發送過程的狀態信息中,超過重試限制表示由于沖突導致的重試次數超過了額定值;滯后沖突表示發送幀的過程中檢測到的沖突信號超過了規定的沖突時間窗;延遲,表明在發送幀之前檢測到信道忙。

4.2 MAC控制模塊

MAC控制模塊提供有全雙工操作中的流量控制功能,流量控制可通過發送和接收PAUSE的MAC控制幀來實現。當接收站點的接收緩沖區(Rx FIFO)快溢出而主機接口義來不及取走數據時,系統就會發出流量控制請求。MAC在接收到流量控制請求之后,即發送PAUSE控制幀,以使數據發送站點在指定的時間內暫停發送數據。

數據發送站點接收到PAUSE控制幀后,便可根據幀中的參數設置PAUSE定時器。PAUSE定時器在減到0之前,發送模塊將暫停發送數據(PAUSE控制幀除外)。PAUSE定時器減到0之后,發送模塊將恢復發送數據。

4.3 MII管理模塊

MII管理模塊用于控制MAC與外部PHY之間的接口,以用于對PHY進行配置并讀取其狀態信息。該接口由時鐘信號MDC和雙向數據信號MDIO組成。MII管理模塊則由時鐘生成模塊、移位寄存器模塊和輸出控制模塊三部分組成。

時鐘生成模塊可以根據系統時鐘和系統設置中的分頻系數來產生MII管理模塊的時鐘信號MDC(10 Mbps速率時為2.5 MHz,100 Mbps速率時為25 MHz)。

移位寄存器模塊既可用于對PHY的控制數據進行寫入操作,也可用于對PHY的狀態信息進行讀出操作。寫控制數據時,移位寄存器根據其他模塊的控制信號將并行控制數據轉換為串行數據;而在讀狀態信息時,移位寄存器則將PHY的串行數據轉換為并行數據,MAC中的其他模塊可將該并行數據寫入適當的寄存器。

由于MDIO是雙向信號,因此,輸出控制模塊就用來決定MDIO是處于輸入狀態還是輸出狀態。當MDIO處于輸出狀態時,移位寄存器輸出的串行控制數據在經過時鐘同步后發送到PHY;當MDIO處于輸入狀態時,移位寄存器將數據線上的串行數據轉換為并行數據。

4.4 主機接口模塊

主機接口是運行以太網的上層協議(如TCP/IP協議)與MAC控制器的接口。通過該接口,上層協議可以設置MAC的工作模式并讀取MAC的狀態信息。該接口還可用于上層協議與MAC之間的數據交換。

主機接口模塊內有一組寄存器,可用于存儲上層協議對MAC設置的參數以及MAC的狀態信息。上層協議對MAC設置的參數包括接收超短幀的使能、添加填充碼使能、持發送超長幀的使能、添加CRC校驗值使能、全雙工模式或半雙工模式、持超長延遲(Defer)使能、混雜模式(Promiscuous)、接收廣播幀使能、發送和接收使能、中斷源和中斷使能、幀間間隙的長度、最大幀和最小幀的長度、重試限制和沖突時間窗、MII地址和MII控制命令、接收和發送隊列的長度以及本機MAC地址等。

上層協議通過MAC發送和接收數據的操作主要由主機接口模塊內的兩個隊列來進行管理,這兩個隊列用于對等待發送的多個幀和接收到的多個幀進行排隊。

發送隊列主要記錄等待發送的幀的相關信息、發送該幀時對MAC的設置以及該幀發送完之后產生的狀態信息。幀的相關信息包括幀的長度、幀在外部存儲器中的地址、該幀是否準備好發送以及隊列中是否還有其它幀等待發送;對MAC的設置則包括中斷使能、填充使能、CRC使能;產生的狀態信息包括成功發送之前的重試次數、由于達到重試限制而放棄發送、發送時產生的滯后沖突以及成功發送之前發生過的延遲。

接收隊列主要對接收到的數據幀進行排隊并記錄每個接收到的幀信息。這些信息包括幀的長度、是控制幀還是普通數據幀、幀中包含無效符號、接收到的幀太長或太短、發生CRC錯誤、接收的過程中發生滯后沖突、幀是否接收完、隊列中是否還有其它已接收到的幀以及幀存儲在外部存儲器中的地址等。該位同時隊列中還有針對每個幀的設置位,用來設置是否在接收到幀時產生中斷。

發送隊列和接收隊列的長度都可以在控制寄存器中進行設置。

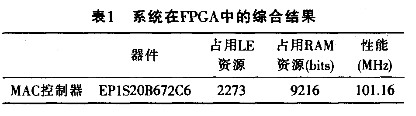

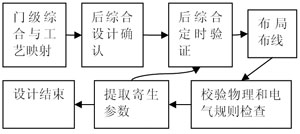

5 綜合結果

本設計采用Verilog語言描述,FPGA芯片使用Altera公司的Stratix-6,整個設計經Synplicity公司的Synplify Pro 8.1綜合后,可在Altera公司的Quartus II 4.2下布局布線,最后用Mentor Graphics公司的ModelSim軟件進行仿真。表1所列是Syn-plify Pro 8.1綜合結果。

該以太網控制器使用的邏輯單元為2273,占用的存儲器資源為9 216 bits,最終的時鐘頻率可達到101.16 MHz,因此,能夠滿足100 Mbit/s的速率要求。

6 結束語

本文給出了完全用FPGA實現嵌入式以太網控制器的設計方法,該方法只需要外接物理層芯片(PHY)和集成有TCP/IP協議的單芯片(即硬協議)或在嵌入式操作系統中運行TCP/IP協議(即軟協議)就可以實現嵌入式系統的高速互聯網接入。從而有效地降低成本,減小版面積和布線復雜度,提高整個系統的集成度。因此,該方法具有一定的實際意義。

-

控制器

+關注

關注

112文章

16412瀏覽量

178713 -

嵌入式

+關注

關注

5087文章

19150瀏覽量

306358 -

以太網

+關注

關注

40文章

5447瀏覽量

172135

發布評論請先 登錄

相關推薦

基于Xilinx FPGA的千兆以太網控制器的開發

以太網控制器(MAC)的基本框架怎么搭建

以太網控制器如何工作

8位單片機與以太網控制器

基于以太網的指紋門禁控制器設計與實現

以太網接口的數據采集控制器

基于FPGA的以太網MAC控制器的設計與實現

如何通過MAX5969B和MAX5971B用電設備控制器實現以太網供電系統

如何使用51單片機控制RTL8019AS實現以太網通訊

AT89C52單片機實現以太網接口的控制設計

基于RTL8019AS以太網控制器實現以太網通訊的應用方案

利用FPGA控制邏輯實現以太網控制器的設計方法

利用FPGA控制邏輯實現以太網控制器的設計方法

評論