關鍵字:D類功放設計

D功放是基于脈沖寬度調制技術的開關放大器,包括脈沖寬度調制器(幾百千赫茲開關頻率),功率橋電路,低通濾波器。本文從構成、拓撲結構對比、MOSFET的選擇與功率損耗、失真和噪音產生、音頻性能等D類音頻功率放大器設計有關的基礎問題作分析,并例舉D類功率放大器參考設計。

1、 D類功放基本構成

目前有很多種不同種類的功放,如:A類、B類、AB類等。但D類功放與其不同的是基本是一個開關功放或者是脈寬調制功放。為此,主要將對說明這類D類功放作以說明。

在這種D類功放中,器件要么完全導通,要么完全關閉,大幅度減少了輸出器件的功耗,效率達90-95%都是可能的。音頻信號是用來調制PWM載波信號,其載波信號可以驅動輸出器件,用最后的低通濾波器去除高頻PWM載波頻率。

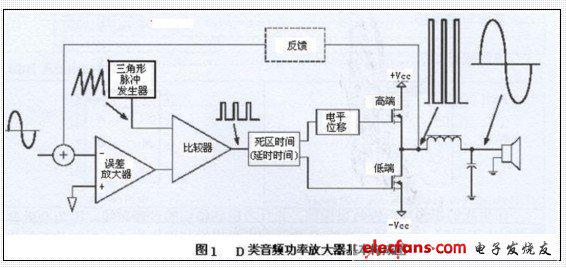

眾所周知, A類、B類和AB類功放均是線形功放,那么D類功放與它們究竟有什么不同?我們首先應作討論。圖1是D功放原理框圖,在一個線性功放中信號總是停留在模擬區,輸出晶體管(器件)擔當線性調整器來調整輸出電壓。這樣在輸出器件上存在著電壓降,其結果降低了效率。

而D類功放采用了很多種不同的形式,一些是數字輸入,還有一些是模擬輸入,在這里我們將集中討論一下模擬輸入。

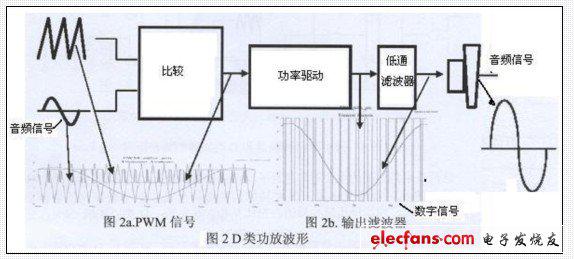

上面圖1顯示的是半橋D類功放的基本功能圖,其中給出了每級的波形。電路運用從半橋輸出的反饋來補償母線電壓的變化。那末D類功放是如何工作的呢?D類功放的工作原理和PWM的電源是相同的,我們假設輸入信號是一個標準的音頻信號,而這個音頻信號是正弦波,典型頻率從20Hz到20kHz范圍。這個信號和高頻三角或鋸齒波形相比可以產生PWM信號,見圖2a中所示。這個PWM信號被用來驅動功率級,產生放大的數字信號,最后一個低通過濾波器被用在這個信號上來濾掉PWM載波頻率,重新得到正弦波音頻信號,見圖2b中所示。

2、 從拓撲結構對比-看線性和D類不同

值此將討論線性功放(A類和AB類)和D類數字功放的不同之處。這兩者之間主要的不同是效率,這也是為什么要發明D類功放的原因。線性功放就其性能而言具有固有的線性,但是即使是AB功放其效率也只有50%,而D類功放的效率很高,在實際的設計中達90%。

增益-線性功放增益不受母線電壓影響而變化,然而D類功放的增益是和母線電壓成比例的。這就意味著D類功放的電源抗擾比率是0dB,而線性的PSRR(電源供應抑制比率)就很好。在D類功放中普遍用反饋來補償母線電壓變化。

能量流向-在線性功放中,能量是從電源到負載,雖然在全橋D類功放中也是這樣,但半橋D類功放還是不同的,因為能量可以雙向流動而導致“母線電壓提升”現象產生,這樣會造成母線電容被從加載來的能量充電。這個主要發生在低頻上,如低于100Hz是這樣。

3、 D類功放與Buck降壓轉換器類拓撲差異

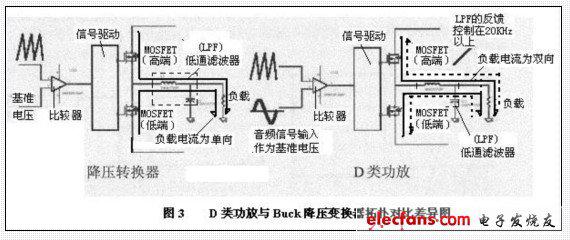

在D類功放和同步降壓轉換器拓撲原理作如圖3所示。這兩個電路之間的主要不同有三:其一、對于同步降壓轉換器,其基準電壓來自反饋電路的慢慢變化的穩定電壓;而D類功放的參考信號是一個不斷變化的音頻信號。也就是說,同步降壓轉換器的占空比是相對穩定的,而D類以圍繞50%占空比不斷地改變。其二、在同步降壓轉換器中負載電流的方向總是朝著負載,即電感電流為單向,見圖3左所示。但是在D類功放中電流是朝著兩個方向的,即電感電流為雙向,見圖3右所示。最后的不同是MOSFET的優化方式。同步降壓轉換器對于高低端的晶體管有著不同的優化,較長的周期需要較低的Rds(on),而較短的周期需要低的Qg(柵極電荷),即兩個開關作用不同。但D類功放對兩個MOSFET有著相同的優化方式。高低端器件有相同的Ras(on),即兩個開關作用相同。

4、 D類功放中MOSFET的選擇

在功放中要達到高性能的關鍵因素是功率橋電路中的開關。在開關過程中產生的功率損耗、死區時間和電壓、電流瞬時毛刺等都應該盡可能的最小化來改善功放的性能。因此,在這種功放中開關要做到低的電壓降,快速的開關時間和低雜散電感。

由于MOSFET開關速度很快,對于這種功放它是你最好的選擇。它是一個多數載流子器件,相對于IGBT和BJT它的開關時間比較快,因而在功放中有比較好的效率和線性度。而MOSFET的選擇是基于功放規格而定。因而在選擇器件以前要知道輸出功率和負載阻抗(如100W 8Ω),功率電路拓撲(如半橋梁或全橋),調制度(如89%—90%)。

5、 MOSFET中的功率損耗

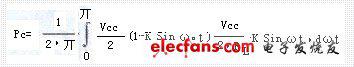

功率開關中的損失在AB線性功放和D類功放之間是截然不同的。首先看一下在線性AB功放中的損耗,其損耗可以定義如下:

K是母線電壓與輸出電壓的比率。

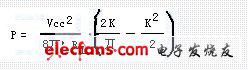

對于線性功放功率器件損耗,可以簡化成下面的公式:

需要說明的是AB功放功率損耗與輸出器件參數無關。

現在一起看一下D類功放的損失,在輸出器件中的全部損耗如下:

Ptotal=Psw+Pcond+Pgd

Psw是開關損耗

Pcond是導通損耗,

Pgd是柵極驅動損耗

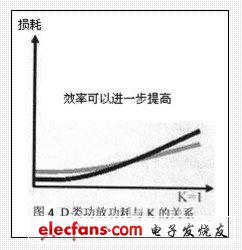

從上式可看于D類功放的輸出損耗是根據器件的參數來定的,即基于Qg(柵極電荷)、Rds(on)(靜態漏源通態電阻)、Coss(MOSFET的輸出電容)和tf(MOSFET下降時間),所以減少D類功放損耗應有效選擇器件,圖4是D類功放的功率損耗和K的函數關系。

6、 半橋和全橋結構拓撲的對比

和普通的AB類功放相似,D類功放可以歸類成兩種拓撲,分別是半橋和全橋結構。每種拓撲都各有利弊。簡而言之,半橋簡單,而全橋在音頻性能上更好一些,全橋拓撲需要兩個半橋功放,這樣就需要更多的元器件。盡管如此,橋拓撲的固有差分輸出結構可以消除諧波失真和直流偏置,就像在AB功放中一樣。一個全橋拓撲允許用更好的PWM調制方案,比如量化幾乎沒有錯誤的三水平PWM方案。

在半橋拓撲中,電源面臨從功放返回來的能量而導致嚴重的母線電壓波動,特別是當功放輸出低頻信號到負載時。能量回流到電源是D類功放的一個基本特性。在全橋中的一個臂傾向于消耗另一個臂的能量。所以就沒有可以回流的能量。

7、 不完美失真和噪音產生

一個理想的D類功放沒有失真,在可聽波段沒有噪音且效率足100%。然而,實際的D類功放并不完美并且會有失真和噪音。其不完美是由于D類功放產生的失真開關波形造成的。原因是:

*從調制器到開關級由于分辨率限制和時間抖動而導致的PWM信號中的非線性。

*加在柵極驅動上的時間誤差,如死區時間,開通關斷時間,上升下降時間。

*開關器件上的不必要特征,比如限定電阻,限定開關速度或體二極管特征。

*雜散參數導致過度邊緣的震蕩。

*由于限定的輸出電阻和通過直流母線的能量的反作用而引起得電源電壓波動

*輸出LPF中的非線性。

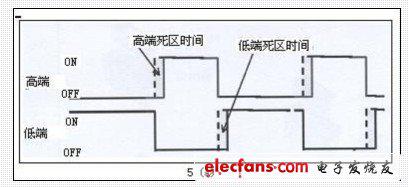

一般來講,在柵極信號中的開關時間誤差是導致非線性的主要原因。特別是死區時間嚴重影響了D類功放的線性。幾十納秒少量的死區時間很容易就產生1%以上的THD(總諧波失真),見圖5(c)所示。

8、 死區時間(見圖5(a)所示是如何影響非線性的)

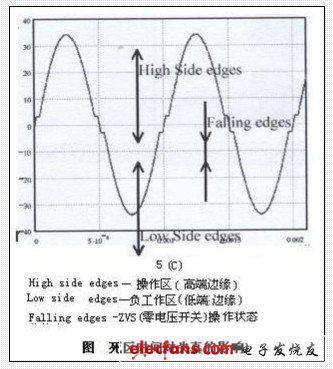

其圖5(a)(b)(c)為死區時間(或稱延時時間)對失真的影響示意圖。D類輸出級中的工作模式可以根據輸出波形如何跟隨輸入時間可歸類成三個不同的區域。在這三個不同的工作區,輸出波形跟隨高低端輸入信號的不同邊緣而變化的。

讓我們檢查一下第一個操作區(見圖5c所示High side edges),在這里電流比電感器波紋電流還大時,輸出電流就從D類功放流向負載。高端器件在低端器件開通之前關斷,輸出節點就會被轉到負母線。這個過程與低端器件開通時間無關,它是通過從解調電感的換向電流自動造成的。因此輸出波形與嵌入到低端器件開通前的死區時間無關。因此PWM波形只被嵌入到高端柵極信號的死區短路了,而造成所希望的輸入占空比的輕微電壓增益降低。

有個相似的情況發生在負工作區(見圖5c所示Low side edges),輸出電流從加載流向D類功放。電流高于電感波紋電流。在這種情況下,輸出波形的時間并沒有受嵌入高端開通沿的死區時間的影響,而總是允許低端輸入時間。因此,PWM波形只被嵌入到低端器件柵極信號的死區時間短路。

在以前描述的兩個操作模式中存在一個區域,在這個區域中輸出時間與死區時間是獨立的。當輸出電流小于電感波紋電流時,輸出時間跟隨每個輸入的關斷沿。因為在這個區域,是ZVS(零電壓開關)操作狀態(見圖5c所示Falling edges),因此在中間區域就不會有失真。

當輸出電流隨著音頻輸入信號的不同而變化時,D類功放將改變它的操作區,這樣每個都會有細小的不同增益。在音頻信號的周期中的這三個不同區域增議會歪曲輸出波形。

圖5(b)顯示的是死區時間如何影響THD性能的。一個40nS死區時間可以產生2%的THD。這個可以通過減小死區時間到15nS提高到0.2%。這個標志著更好線性與高低端開關器件轉換過程的重要性。

9、 音頻性能測量

有著AESl7網絡過濾器的音頻測量儀器是很必需的。當然,像傳統音頻分析器HP8903B,加上合適的前級低通濾波器也可以使用。在這里需要重要考慮的是D類功放的輸出信號在其波形上仍然含有大量的開關載波頻率,這樣就造成錯誤的讀取。這些分析器也許很難防止D類功放的載波泄露。

10、防止直通

盡管如此,一個狹窄的死區時間在大量生產中是很危險的。因為一旦高低端晶體管被同時打開,那么直流母線的電壓就會被晶體管短路,大量的直通電流將開始流動,這便會導致器件損壞。我們應該注意到有效的死區時間對每個功放是不同的,與元件參數和芯片溫度有關。對于一個D類功放的可靠設計來講確保死區時間總是正的而決不是負的來防止晶體管進入直通,這是非常重要的。

11、關于電源吸收能量

另外一個在D類功放中引起明顯降額的原因是母線充電,當半橋拓撲在給負載輸出低頻時可以看到。要時刻記住,D類功放的增益與母線電壓直接成比例關系。因此,母線電壓波動產生失真,而D類功放中的電流流動是雙向的,則就存在了從功放返回到電源時期。大量流回到電源的能量來自于輸出LPF的電感存儲的能量。通常,電源沒有辦法吸收從負載回流過來的能量。因此,母線電壓上升,造成電壓波動。母線電壓上升并不是發生在全橋拓撲上,因為從開關橋臂同儲到由源的能源熔會在另一個橋臂消耗掉。

12、對EMI(電磁輻射)的考慮

在D功放設計中的EMI(電磁輻射)是很麻煩的,像在其他開關應用中一樣。EMI的主要來源之一是來自從高到低流動的MOSFET二極管的反向恢復電荷,和電流直通很相象。在嵌入到阻止直通電流的死區過程中,在輸出LPF中的電感電流打開體二極管。在下一個階段中,當另外一端的MOSFET在死區未打開時,體晶體管保持導通狀態,除非儲存的大量少數載波被完全復合。這個反向的恢復電流趨向于形成一個很尖的形狀,和由于PCB板和封裝雜散電感因起步希望的震蕩。因此,PCB布線設計對減小EMI和系統可靠性至關重要的。

13、D類功放中MOSFET選擇的其他考慮

*選擇合適的封裝和結構

*功放的THD、EMI和效率,還受FET的體二極管影響。縮短體二極管恢復時間(工R的并聯肖特基二級管的FET);降低反向恢復電流和電荷,能改善THD;EMI和效率。

*FET結殼熱阻要盡可能小,以保證結溫低于限制。

*保證較好可靠性和低的成本條件下,工作在最大結溫。用絕緣包封的器件是直接安裝還是用裸底板結構墊絕緣材料,依賴于它的成本和尺寸。

14、D類功放參考設計見圖6所示

*拓撲:半橋

*選用IR2011S(柵極驅動IC,最高工作電壓200V,Io+/-為1.0A/1.0A,Vout為10-20V,ton/off為80&60ns,延時匹配時間為20ns);IRFB23N15D (MOSFET功率管ID=23A,R DS=90mΩ,Qg=37nC Bv=150V To-220封裝)

*開關頻率:400KHz(可調)

*額定輸出:200W+200W/4歐

*THD:0.03%-1mhz半功率

*頻率響應:5Hz-40KHz(-3dB)

*電源:~220v±50V

*尺寸:4.0“×5.5”

15、結論

如果我們在選擇器件時很謹慎,并且考慮到精細的設計布線,因為雜散參數有很大的影響,那么目前高效D類功放可以提供和傳統的AB類功放類似的性能。

-

放大器

+關注

關注

143文章

13583瀏覽量

213367 -

功放

+關注

關注

97文章

795瀏覽量

103372 -

調制器

+關注

關注

3文章

840瀏覽量

45142

發布評論請先 登錄

相關推薦

D類音頻功率放大器設計基礎,D類功放設計

D類音頻功率放大器設計基礎,D類功放設計

評論