啟動和關閉時序

為了優化開關機的POP 聲和避免DC Detect 功能的誤觸發,在系統設計時需要注意主芯片和功放 器件的啟動時序。啟動時序分為電源時序和使能時序兩種,電源時序是指系統中各種芯片電源供電或斷電的時序。而使能時序可理解為系統供電穩定后由系統主控決定的器件功能使能的先后次序。

對于電源時序來說,由于多數主芯片的音頻輸出在上電和斷電過程中不太穩定,理想的上電次序是系統主芯片先于功放 上電。然后功放 的PVCC 再供電。斷電的理想時序正好相反,為功放 的電源先切斷,然后再切斷主控芯片的供電。

但是通常功放 的PVCC 取自于系統的主電源,該電源一般在開機后最先輸出。隨后再通過DC/DC 或LDO 降壓給主芯片供電。所以功放 一般在主芯片穩定前已經供電并啟動。這種設計中,上電時必須保證TPA311x 的/SD 腳處于拉低狀態,避免主芯片上電過程中的POP 聲輸出。掉電時,也需要將功放 置于standby 狀態,避免主芯片掉電時的POP 聲輸出。通常上電過程的POP 聲較容易解決,但系統掉電時需要使用掉電檢測電路來強制將功放 的/SD 快速拉低來解決掉電POP 聲的問題。

使能時序:由于主芯片音頻模擬輸出的偏置電壓一般在輸出使能后建立,此時需要保持功放 的/SD 拉低,等待主芯片模擬輸出的偏置電壓穩定后才可以將/SD 置高開啟功放。相反,需要關閉主芯片音頻模擬輸出功能時,需要先拉低/SD 將功放關閉后,再關閉主芯片的模擬輸出信號。這樣的時序是為了保證主芯片模擬輸出的偏置電壓掉電時不會引起POP 聲。

輸入級模型

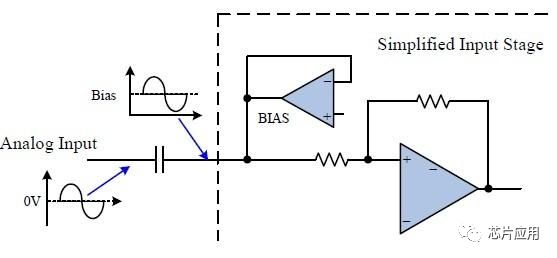

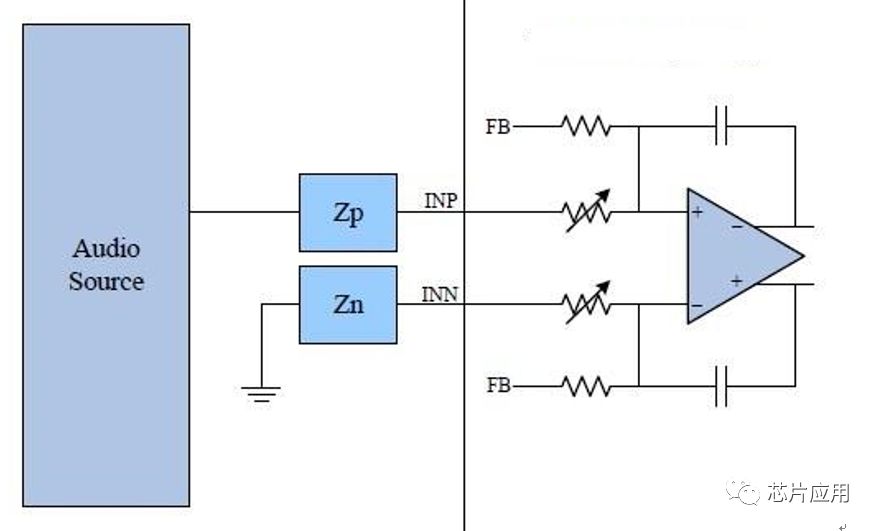

功放 是單電源供電的模擬輸入Class D 功放,這類功放的模擬輸入必須工作在直流偏置(DC BIAS)點上才可以正常傳輸交流音頻信號,簡化的輸入級模型如圖1 所示。功放 的直流偏置電壓設定在3V。

圖 1. 模擬輸入級等效模型

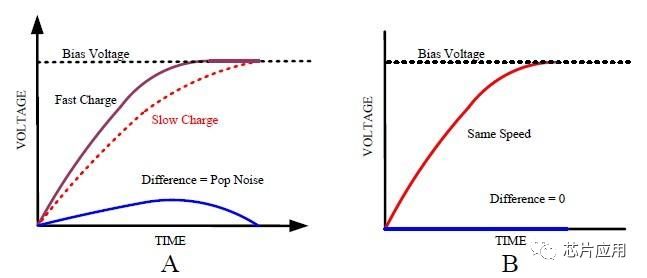

功放在啟動時,偏置電壓會從0V 上升到額定的偏置電壓,該過程的時間長短取決于內部偏置電壓源對外部阻抗網絡的充電速度。

圖 2. 差分輸入偏置電壓建立過程

功放 差分輸入INN 和INP 的輸入偏置電壓建立的過程如圖2所示,若差分輸入N 和P 端的輸入偏置電壓建立速度不一樣則兩者之差會形成差分信號輸入功放并被放大輸出,形成啟動時的POP 聲。差分輸入端偏置電壓建立過程的不平衡通常是因為輸入級INN 和INP外部的阻抗不匹配所致。這種情況最容易出現在差分輸入用作單端輸入狀態。

功放 的單端輸入方式

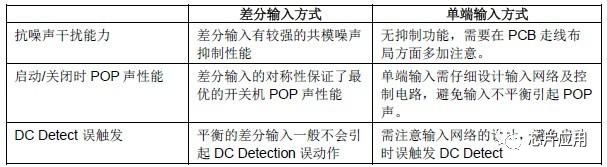

功放 器件的模擬輸入是標準的差分輸入接口。在系統設計中,推薦使用差分輸入方式來接駁主芯片的音頻輸出。使用差分輸入方式可以不僅POP 聲的控制相對簡單、信號抗干擾能力強,而且不會引起DC Detection 功能的誤動作。差分輸入方式和單端輸入方式的對比如下表所示:

表 1. 差分、單端輸入方式對比表

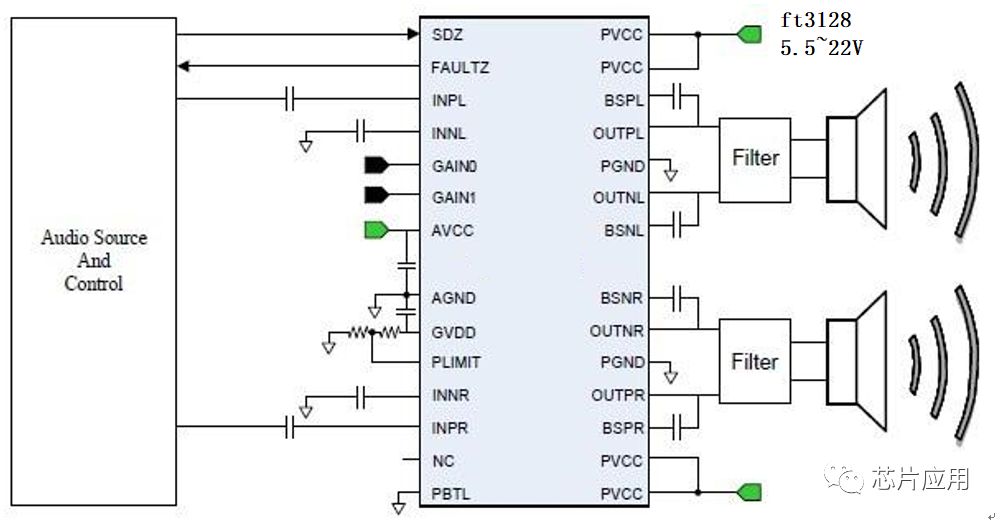

不過在實際應用中,由于多數主芯片的音頻模擬輸出是單端模式, 功放 的差分輸入必須配置為單端接法才能使用。如圖3 所示,單端輸入時,主芯片輸出通過耦合電容連接功放INP(INN) 腳。INN (INP)輸入通過電容耦合到地即可。

圖 3. 功放 單端輸入接法

使用單端輸入模式時需注意以下幾點:

1. 單端輸入模式應用時需要更加注意音頻信號的走線和地平面的分布,因為單端輸入模式沒有能力抑制系統中的公模干擾信號。

2. 相比差分信號輸入模式下,單端輸入,需要輸入兩倍的輸入信號電平來達到相同的輸出功率。

3. 單端輸入模式必須注意P/N 腳電路網絡的阻抗匹配,盡量不要在輸入級使用復雜的濾波網絡。不合適的阻抗網絡不僅會引起開關機的POP 聲,也有可能引起DC Detection 功能的誤觸發,導致功放鎖死。若必須在輸入級進行濾波或增益設置,請參考使用運放來進行濾波及增益的調節。

輸入阻抗網絡的匹配

若使用單端輸入的方式連接功放 ,則必須注意輸入阻抗網絡的匹配問題。如圖5 所示,功放的INN 輸入端外部阻抗為Zn,通常Zn 為耦合電容。主芯片輸出阻抗一般很小,可認為輸出阻抗為零,則INP 輸入端外部阻抗約為Zp。功放啟動時內部的偏置電壓會逐步建立,其過程即為向Zn 和Zp 阻抗網絡充電的過程。若Zn 和Zp 阻抗相差太大,INN 和INP 之間就會形成較大的差分信號,該差分信號被功放放大之后則形成POP 聲。

功放設計的啟動時間舉例30ms,該時間是從/SD 被拉高到功放輸出聲音的時間。若上述啟動時對輸入阻抗網絡的充電穩定時間少于30mS,則因阻抗不匹配引起的差分輸入也不會被放大而帶來POP 聲的問題。減小Zn 和Zp 中的電容參數可以縮短輸入級穩定時間,但減小電容會使得低頻增益降低,用戶需酌情考慮。

圖 4. 匹配輸入阻抗

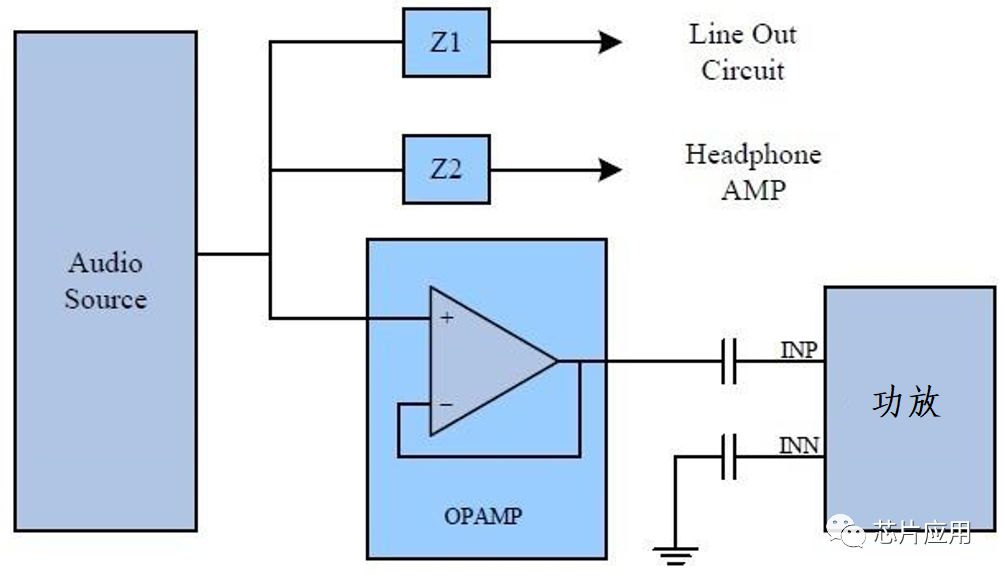

使用運放建立隔離系統

在某些系統中,主芯片的音頻信號輸出不僅需要連接到功放輸入,還要輸出到Line Out(線路輸出),或者其他的芯片進行處理。該種情況下輸入級的網絡比較復雜,單端輸入模式的阻抗匹配不容易實現。為了解決這個問題,可以使用運放接成一個簡單的跟隨器來建立一個隔離的阻抗輸入系統。跟隨器的輸入阻抗很高,對源信號沒有影響。其輸出阻抗非常低,可良好匹配功放 的輸入阻抗網絡。圖 5 給出了使用跟隨器來建立一個隔離的輸入阻抗網絡的電路。需要時,還可將運放用來調節信號增益及濾波。

圖 5. 使用運放建立隔離的阻抗網絡

功放 Pop 聲分析及解決方案

1 POP 的原因及調試方法

功放 的Pop 聲有兩種可能的原因:輸入阻抗不匹配及不合理的系統時序

輸入阻抗不匹配:

輸入阻抗不匹配會引起器件啟動和關閉時差分輸入端產生電壓差,這種POP 聲是在/SD 電壓變化時產生的,發生在功放 輸入端的Bias(偏置電壓)的建立過程中。遵從匹配輸入級阻抗網絡的方法即可解決該種POP 聲。

不合理的系統時序

如 1 節所述,主芯片啟動或關閉時,模擬輸出的偏置電壓也需要一個建立的過程,而且主芯片上電過程中也有可能輸出不可控的POP 聲。所以在上電過程中,必須保證功放處于Standby 狀態下。避免將前級芯片產生的POP 聲放大輸出到喇叭。

POP 聲的最終表現一樣,但根本原因可能有不同,以下是推薦的查找POP 聲原因的調試方法:

1. 隔離功放輸入和主芯片輸出;出現POP 聲后,首先要將主芯片的輸出斷開,并將功放輸入電路部分通過電容交流短路到地。此時可以控制/SD 腳電平模擬開關機過程。若POP 聲仍然存在,則說明功放啟動時P/N 腳對外部網絡的充電速度不一致,導致差分輸入存在壓差所致。若POP 消失,則可進行下一步驗證。

2. 確認功放無輸入情況下開關無POP 聲之后,可使用外部電源給主芯片供電。保持主芯片電源不切斷是為了排除主芯片輸出在掉電時產生POP 聲的影響。此時進行整個系統正常的開關機驗證POP 聲。若POP 聲消除,則可判斷主芯片掉電時序和功放的掉電時序不匹配,導致主芯片掉電時產生的POP 聲被功放放大輸出。部分系統中電源并未完全關閉,系統有待機模式時可用待機芯片的I/O 口進行時序的控制,若系統的開關機是電源硬關斷模式則需要進行系統電源時序的優化。部分情況下,需要添加上電/掉電檢測電路來控制POP聲。

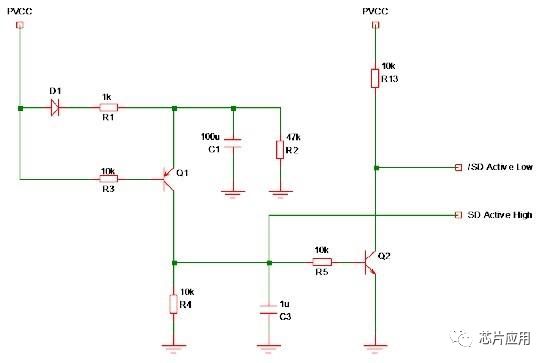

2 掉電檢測電路

在使用硬件開關直接關閉主電源的系統中,掉電時的POP 聲控制較為困難。因為該類系統無法提前預知系統掉電,無法在掉電之前使用控制器I/O 口靜音或關閉功放。這時就必須使用如圖76所示的掉電檢測電路來解決該問題。該電路可在系統電壓跌落初期提供控制信號,使用該控制信號拉低/SD 腳即可在掉電初期快速關閉功放。

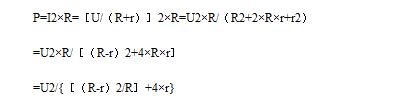

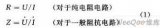

掉電檢測電路在正常供電時PVCC 會通過二極管D1 和電阻R1 向C1 大電容充電。掉電初期,Q1 的基極電壓將隨著PVCC 的跌落降低,直到跌落到Q1 三極管打開后,C1 的電壓將通過Q1送給Q2 的基極,Q2 導通,/SD 被拉低。根據上述原理,可由以下計算出電壓跌落的位置Vdrop:

該例中,PVCC 為12V, Vf 和Veb 為0.7V, 則掉電保護點約在10.3V 左右,與波形圖8 吻合。

圖 6. 掉電檢測電路

圖 7. 掉電檢測電路示例波形

掉電檢測電路在應用時需要注意調整R1 和R2 的數值,選擇合適的掉電保護點。避免電源的紋波觸發掉電保護電路導致誤觸發靜音。電路中給出了Active High 和Active Low 兩種邏輯供用戶選擇。可以根據功放所需的邏輯自行選用。

-

阻抗匹配

+關注

關注

14文章

358瀏覽量

31446 -

PoP

+關注

關注

0文章

33瀏覽量

16036

原文標題:音響的各種pop音分析及功放的阻抗匹配

文章出處:【微信號:gh_4cd31d714d67,微信公眾號:芯片應用】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

淺析阻抗匹配及其應用

TPA3110D2正常工作過程中產生的POP音,是不是輸入阻抗匹配的問題,輸入阻抗應該怎么改呢?

音頻輸入和功放之間的阻抗匹配

基于Ansoft Designer的射頻功放電路阻抗匹配優化

怎樣理解阻抗匹配_pcb阻抗匹配如何計算

評論