在像PCIE這樣的高頻環境中,傳送線在信號線上驅動電壓變化時會出現阻抗,信號線的寬度和到接地的距離都會影響其阻抗,所以在設計PCB時需要參考PCIE總線規范,特別要注意考慮信號阻抗匹配。以下供設計PCB時作為參考:

● 插卡從金手指邊緣到PCIE芯片管腳的走線長度應限制在4英寸(約100mm毫米)以內。超過該長度后需要使用高頻差分傳輸線,我們可以提供延長300mm以上的技術方案。

● PCIE的PERPN,PETPN,PECKPN是三個差分對線,其中PECKPN是100MHz頻率的差分信號線,需要注意保護,前兩對是2.5GHz頻率的差分信號線,更需要注意保護。

● 差分對線中的兩條走線要同步布線。如果走線要轉彎,那么兩條走線應該同步轉彎,并且轉彎要避免銳角、直角,而應該使用弧線或者鈍角轉彎。

● 差分對線走線過程中盡量避免使用VIA過孔,如果一定要通過過孔換層,那么兩條走線應該同步做過孔,并且應該在靠近信號對線過孔處放置GND地信號過孔,條件允許時適當增加周邊GND地信號過孔數量。

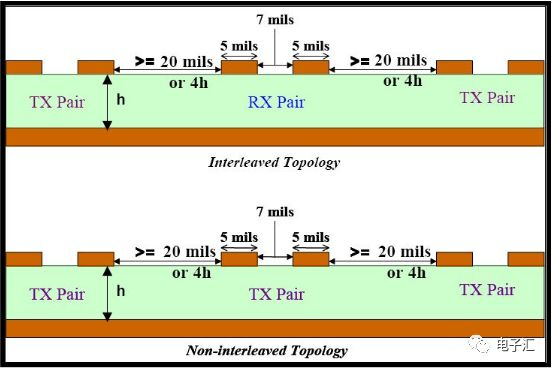

● 差分對線中的兩條走線的長度差應該控制在5mil之內,最大10mil(約0.25mm)。PCB走線的線寬建議是7mil(約0.18mm),兩條走線的凈間距建議是7mil。有關線寬和線間距的詳細分析請參考PCIE規范。

● 兩對差分對線之間的距離(例如PER對與PECK對)、或者差分對線和其它非PCIE信號的距離,建議不小于20mil(約0.5mm),以減少相互之間的串擾和電磁干擾(EMI)的影響。建議在兩對差分對線之間用GND地線隔離,例如,從左向右是:GND、PECK對線、GND、PER對線、GND、PET對線、GND。

● PCIE芯片,尤其是PCIE信號線的PCB反面,應該盡量避免走高頻信號線,最好全GND地鋪銅。例如,CH367芯片的SCL信號線、IORD信號線是相對的高頻信號線,建議不要穿越PCIE芯片走線。

● PCIE需要在發送端(PETPN)和對方的接收端之間進行交流耦合,差分對的兩個交流耦合電容必須有相同的封裝尺寸,位置要對稱,并且要擺放在靠近金手指這邊。建議選擇容量為0.1uF的高頻電容,封裝尺寸推薦使用0402,另外0603也可以接受,但是不允許使用直插封裝的電容。

● 在設計PCB時,應該在PCIE芯片的每對電源引腳(VCC18GND、VCC33GND)附近放置一個容量為0.1uF左右的高頻退耦電容,離芯片的距離不能太遠。另外,整個芯片的VCC18和VCC33各需要一個容量不小于10uF的鉭電容進行中低頻退耦。

● 由于PCB過孔(VIA)電阻較大并且容易受長期高溫老化影響而不穩定,為了減少其消耗的電壓降,考慮到VCC18VCC33與GND之間的數百mA電流,建議連接PCIE芯片的電源或者GND走線上的過孔使用大過孔、雙過孔或者使用雙回路電源(兩條路徑)。

● 部分芯片組和主板支持PCIE板卡帶電熱插拔,為了支持帶電熱插拔,板卡設計時需要做兩點額外處理:

一是設計電路原理圖時,請在PCIE芯片的PERST#引腳信號線與GND之間跨接一個1000pF的貼片電容;

二是設計PCB時,請將PCIE的PERST#引腳信號的金手指設計為與PRSNT1#長度差不多的短金手指。

-

pcb

+關注

關注

4320文章

23117瀏覽量

398413 -

總線

+關注

關注

10文章

2890瀏覽量

88159 -

PCIe

+關注

關注

15文章

1241瀏覽量

82747

原文標題:[討論]PCIE總線規范范例:PCI-Express板卡PCB設計

文章出處:【微信號:gh_f97d2589983b,微信公眾號:高速射頻百花潭】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何進行PCI-Express的一致性測試和分析

PCIE總線規范范例:PCI-Express板卡PCB設計

基于PCI-Express的高速數據交換設計及應用

pci express總線概念

基于Virtex5的PCI-Express總線接口設計

PCI-Express插槽

從PCI、PCI-X到PCI-Express之間的連接

PCIE-PCB設計規范

PCIe及PCB設計要求

PCIE總線規范范例:PCI-Express板卡PCB設計

PCIE總線規范范例:PCI-Express板卡PCB設計

評論