在電子設(shè)備和通信系統(tǒng)的設(shè)計和布局中,必須仔細考慮晶體振蕩器和外圍電路,以優(yōu)化性能。作為信號源的核心,晶體振蕩器必須產(chǎn)生很高的精度輸出,因此對高頻率噪聲從其他的板上來說是非常敏感的。

這種電路在設(shè)計時需要明確的注意。這些技術(shù)說明是在一些外圍電路中減少噪音的設(shè)計指南,在這些電路中高頻噪聲對晶體振蕩器的輸出尤其有利。

噪聲來源

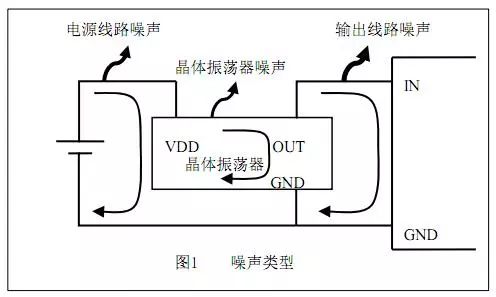

首先,在圖1中,我們指出了典型的由晶體振蕩器和外圍電路產(chǎn)生的噪聲。

有三個主要的噪聲源:

1.電源線路噪聲

2.輸出線路噪聲

3.晶體振蕩器的噪聲

通常被稱為“噪聲”的是這三個因素的累積結(jié)果。

下面我們將對地址類型的噪聲進行解釋。

1、電源線路噪聲

電壓波紋和開關(guān)噪聲通常是由電源線發(fā)出的。這種噪聲會影響晶體振蕩器的輸出。此外,有必要確保晶體振蕩器產(chǎn)生的波紋噪聲不會流到電源線上。實施這些措施還可以改善隔離,防止其他設(shè)備產(chǎn)生的外部噪聲流入晶體振蕩器,從而保證晶體振蕩器的穩(wěn)定性。

2、輸出線路噪聲

輸出線噪聲是指輸出線作為天線的晶體振蕩器輸出的信號。對于輸出信號和物理跟蹤,應(yīng)該實現(xiàn)降低噪聲的技術(shù)。

3、晶體振蕩器噪聲

晶體振蕩器的噪音是指晶體振蕩器內(nèi)部集成電路和電路發(fā)出的噪聲。要解決這一噪聲,需要確保晶體振蕩器穩(wěn)定的電源供應(yīng),并確保所需波形的形成,以實現(xiàn)晶體振蕩器的穩(wěn)定運行。

這些噪聲源依賴于上述的原因,并可通過本文稍后所提到的功率線和輸出線技術(shù)間接地減輕。

上述電源發(fā)出的噪聲水平與電流和電流環(huán)路徑成正比。因此,電流或電流回路阻抗的降低會導(dǎo)致發(fā)射噪音的降低。一般來說,電流和電流環(huán)路徑長度與晶體振蕩器及其外圍電路有關(guān)。

電流量: 電源線=晶體振蕩器>輸出線

電流環(huán)大小: 輸出線>電源線>晶體振蕩器

輸出線噪聲對晶體振蕩電路有最大的影響,其次是功率線的噪聲貢獻。實際晶體振蕩器所發(fā)出的噪聲比其他兩種來源的噪聲要低得多。

噪音對策

在這些技術(shù)說明中,我們已經(jīng)研究了晶體振蕩器及其外圍電路中的噪聲來源。在這里,我們解釋減少噪音的措施。主要有三種降噪措施:

1.建立穩(wěn)定的電源和接地連接。

2.安裝濾波器以防止電源線產(chǎn)生噪聲。

3.在主板上配置一條穩(wěn)定的輸出線。

1、穩(wěn)定的電源和接地連接

穩(wěn)定的電源和接地是指在寬頻帶(特別是高頻率)的極低的阻抗水平,以及在帶寬的所有點上達到均勻電勢的導(dǎo)體。特別是,接地線代表電路的基本電勢,因此必須達到最大的穩(wěn)定水平。這就需要設(shè)計一種具有不收縮的寬表面積的接地平面。

在多層板上,額外的接地平面用來在獨立層上配置電源線和地線。當設(shè)計涉及焊點,更廣泛的接觸面積確保更低的阻抗,因此更少的噪音。

2、電源線濾波器

通常,在電源線和地線之間放置一個濾波器,以防止晶體振蕩器的噪音泄漏到電源或接地線,反之亦然,以防止電源線的噪音進入晶體振蕩器。通常,旁路電容器用作電源線和地線的濾波器。下面提供詳細的解釋。

A.旁路電容

旁路電容器可以降低相互作用的阻抗,并幫助穩(wěn)定電路的工作,同時吸收電力線上存在的噪聲。這是一種眾所周知的消噪方法。用適當?shù)碾娙葜蛋惭b電容器將解決大部分與噪音有關(guān)的問題。

I、旁路電容容量值

標準旁路電容值在0.01μF和1μF之間。該值應(yīng)盡可能低,但在電源端子VCC和電源線阻抗相對于地面的頻率范圍內(nèi)是晶振頻率的三倍。在這里,您必須確認此頻率的頻率特性,以確保高頻側(cè)或低帶側(cè)的阻抗電平不增加。

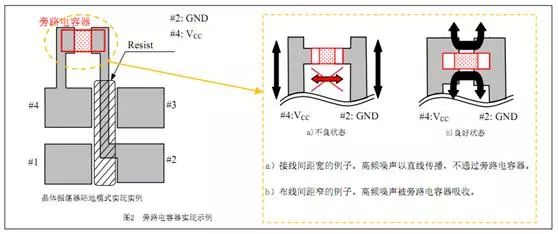

II、安裝旁路電容器

為了減小噪聲,旁路電容應(yīng)盡可能靠近晶體振蕩器安裝。隨著跟蹤長度的增加,寄生電感將增加,并導(dǎo)致更高頻率的阻抗增加。旁路電容的跟蹤長度應(yīng)配置,以便信號通過連接到電源線。這將迫使噪聲通過旁路電容器,并改善噪聲消除效果。

避免在圖2a中顯示的類型。安裝旁路電容器時。高頻噪聲通常以直線的方式傳播,所以如果采用如圖2a所示的模式,噪聲就不會通過旁路電容器。因此,使用圖2b中所示的模式。

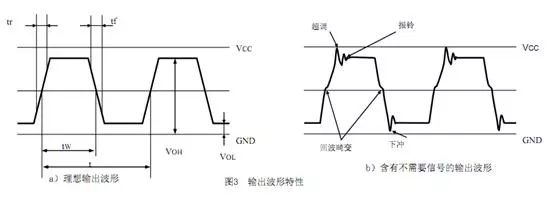

III、配置穩(wěn)定的輸出行

穩(wěn)定的輸出線是指能夠有效地將晶體振蕩器的輸出波形轉(zhuǎn)換為所需輸入的信號,并且具有最小的失真和電磁輻射。配置穩(wěn)定輸出線的關(guān)鍵在于確保輸入所需的波形屬性,如tr、tf、VOH、VOL等。

此外,穩(wěn)定的輸出線需要消除不必要的信號,如超調(diào)、低射、振鈴和回聲,如圖3b所示。為了減少不必要的輻射,了解跟蹤的天線效率也是很重要的。

防止輸出波形失真的措施包括:

a.配置串行電阻

b.配置終端電阻

c.配置過濾器

d.匹配輸出線阻抗

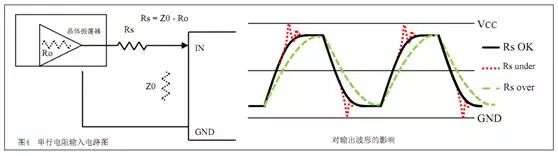

a.配置串行電阻

連接一個晶體振蕩器輸入設(shè)備通常在波形失真,包括過沖,下沖和振鈴的生產(chǎn)結(jié)果。這些扭曲的高頻成分,3-7倍的振蕩頻率和產(chǎn)生噪聲,應(yīng)取消發(fā)射。

為了消除這種失真,串行電阻連接在晶體振蕩器的輸出端和輸出線之間,如圖4所示。電阻值可以使晶體振蕩器的輸出阻抗的總和(RO)和串聯(lián)電阻(RS)相當于輸出線路阻抗(Z0)。

可以進行測試,以確定串行電阻的最佳值。測試方法包括用示波器測量輸出波形,并從低到高的值進行串聯(lián)電阻的轉(zhuǎn)換。最優(yōu)阻值是指超沖、低射和振鈴的值都被消除了。

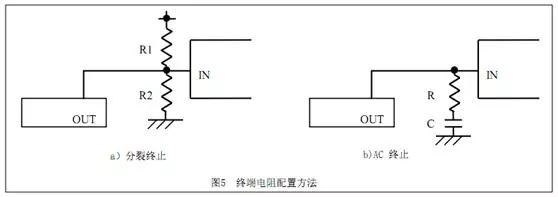

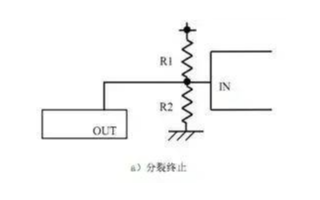

b.配置終端電阻

終端電阻的配置在很大程度上取決于接口的類型和使用的時鐘線的類型。配置將根據(jù)這些因素而變化。

一般來說,當輸出線上的阻抗與設(shè)備輸入的阻抗不匹配時,輸出波形會發(fā)生失真。當阻抗不匹配時,行波不能完全接收,部分信號被反射回振蕩器,從而導(dǎo)致輸出波形失真。這導(dǎo)致高頻噪聲。

當分支晶體振蕩器輸出到多個設(shè)備時,這種波形失真會導(dǎo)致觸發(fā)錯誤。因此,正確的終止和阻抗匹配是至關(guān)重要的。

為了防止來自接收設(shè)備的回聲,輸入端應(yīng)與輸出線上的阻抗值相同。圖5顯示了兩種常見的終止方法:分裂終止和AC終止。

c.配置過濾器

通常,輸出波形失真可以通過串行電阻或終端電阻來解決。在這些方法不能解決問題的情況下使用過濾。濾波器的使用是消除高頻噪聲的一種有效方法,但這種方法會導(dǎo)致TR和TF(波形耗散)的增加。

因此,您必須選擇一個適合TR和TF屬性的過濾器。另外,使用更大的電容器作為濾波器可以導(dǎo)致電流的增加,反之則會導(dǎo)致噪聲的增加。

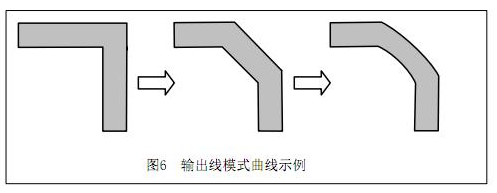

d.輸出線阻抗匹配

減少輸出線上的波形回波要求輸出線阻抗盡可能一致。如圖6所示,實現(xiàn)一致的輸出線路阻抗涉及到輸出線模式曲線配置使直角轉(zhuǎn)變成45o角或,如果可能的話,一個圓形的曲線。另外,避免使用通孔或T形。

最后,我們將介紹兩種最重要的減少噪音排放的方法。

a.使用更短的輸出線

在所有電路中,輸出線最容易產(chǎn)生噪聲。因此,在設(shè)計和布局時,應(yīng)優(yōu)先考慮允許最短輸出線不出現(xiàn)阻抗波動。使用較短的布線將輸出線諧振頻率移到高頻側(cè)。頻率越高,輸出頻率元件就會產(chǎn)生更多的阻尼,從而導(dǎo)致噪聲的降低。

b.使用較短的電流環(huán)路徑

如上所述,輸出線發(fā)出的噪聲電平與當前環(huán)路路徑長度成比例。因此,重要的是,晶體振蕩器和輸入設(shè)備的輸出和接地軌跡應(yīng)盡可能短。實現(xiàn)這一點的一個簡單方法是將接地平面安裝在輸出跟蹤的對側(cè)。

如以上所述,對晶體振蕩器及其外圍電路進行仔細的電路設(shè)計是降低噪聲的關(guān)鍵。最佳電路設(shè)計可以避免與噪聲有關(guān)的問題,并使設(shè)備能夠充分發(fā)揮其性能潛力。

-

電路

+關(guān)注

關(guān)注

172文章

5905瀏覽量

172159 -

振蕩器

+關(guān)注

關(guān)注

28文章

3832瀏覽量

139050 -

噪聲

+關(guān)注

關(guān)注

13文章

1121瀏覽量

47402

原文標題:史上最全!電路降噪指南,告訴你一個正確學習姿勢

文章出處:【微信號:elecfans,微信公眾號:電子發(fā)燒友網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

電源外圍保外圍應(yīng)用電路

電源紋波噪音測試中需要注意的一些問題總結(jié)

如何減少電路板設(shè)計中的串擾

設(shè)計外圍電路時如何減少噪音

數(shù)電中邏輯電路,復(fù)位,處理信號的一些疑問資料下載

一些常用外圍電路的設(shè)計/硬件電路設(shè)計參考及注意事項(個人經(jīng)驗總結(jié))

產(chǎn)生噪音的原因有哪些 怎么去除錄音中的噪音

電感為什么會有噪音?怎樣減少電感器件的噪音?

LED驅(qū)動器應(yīng)用的一些指南和技巧

一些外圍電路中減少噪音的設(shè)計指南

一些外圍電路中減少噪音的設(shè)計指南

評論