當今電力系統中的電能質量問題越來越突出,一方面,大量敏感性負荷對電能質量的要求越來越高,而另一方面,越來越多的非線性負荷不斷接入電網,使電力系統總體的電能質量狀況不斷惡化。

諧波是電能質量中很重要的一個方面,諧波的存在對電力系統產生的危害有以下幾個方面:

1)可能使電力系統繼電保護裝置和自動裝置產生誤動或拒動;

2)使各種電氣設備產生附加損耗和發熱,使電機產生機械振動及噪聲;

3)諧波電流在電網中流動增加損耗,影響電網及各種電氣設備的經濟運行;

4)諧波電流通過電磁感應、電容耦合以及電氣傳導等作用,對周圍的通信系統產生干擾;

5)諧波使電網中廣泛使用的各種測量儀表產生誤差;

6)增加了電網中發生諧波諧振的可能,從而造成很高的過電流或過電壓而引發事故的危險性。

隨著諧波污染的日益嚴重和對電能質量要求的提高,對諧波抑制的要求也越來越高,如何根據現場的諧波污染狀況進行濾波器的投切也變得更加重要。針對這種情況,研制了一種諧波控制器,它可以對現場的諧波和無功等進行監測,根據現場諧波狀況對濾波器進行自動投切,達到抑制諧波、改善電能質量的目的。下面介紹基于DSP芯片TMS32LF2407的諧波控制器的硬、軟件設計。

1 諧波控制器的硬件設計

諧波控制器的基本原理是實時對電流、電壓進行采樣,將采到的數據經過D5P進行數據分析后,得到現場諧波的狀況,從而決策是否對濾波器進行投切。

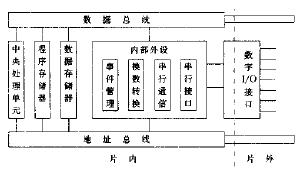

美國TI公司生產的TMS32LF2407型DSP芯片是一款高性能16位定點DSP,該系列DSP控制器將實時信號處理能力和控制器外設功能集于一 身,特別適合于工業控制應用。其芯片供電電壓為3.3V,降低了控制器的功耗。高達40M 1PS的執行速度(工作最高頻率為40MEz),片內有32K字的Flash程序存貯器,544字的DARAM和2K字的SARAM,可以外擴存貯器總共有:194K字空間,片內集成了看門狗(WDT);提供多達16路模擬輸入的10位A/D,最小轉換時間為375ns;高達40個可單獨編程或復用的通用輸入/輸出引腳。具有低成本、低功耗、高速運算能力和高性能處理能力的優點。因此,該DSP芯片可以滿足作為此系統主控芯片的要求。

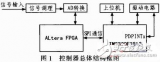

所研制的諧波控制器的硬件結構圖如圖1所示。

通過圖1可知,此硬件電路主要包括采樣電路、中央處理單元、復位電路、鍵盤和液晶顯示功能、執行機構等幾個部分。下面就硬件電路設汁中要特別注意的地方進行闡述:

1.1 采樣電路

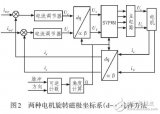

由于TMS32LF2407芯片的AD采樣最大只能送入3.3V的電壓信號,因此,在將電流、電壓信號送到AD口之前要經過電流互感器和電壓互感器進行調理,為了使引入的信號免受外界的干擾,互感器類型的選擇和調理電路的抗千擾要特別地注意。此外,采樣電路還應該要注意的一點是:由于TMS32LF2407的AD口很脆弱,也就是說AD口不能送入峰值超過3.3V的電壓信號,否則AD口將被燒壞,因此,最好添加一個限幅電路。具體的調理電路如圖2所示。

1.2 過零檢測電路

為了使主芯片能夠實現同步采樣,進而提高數據處理的真實性,因此,在電路中應該加入過零檢測電路。過零檢測電路也就是方波發生電路,它對諧波分析同步采樣起著很重要的作用。它將電壓信號變為同頻率的方波信號,DSP通過捕獲方波的上升沿來跟蹤電網頻率,為保證同步采樣提供了條件。具體的檢測電路如圖3所示。

1.3 執行單元

在執行單元中,繼電器的供電電源是12V,而DSP的供電電源和IO口輸出的高電平為3.3V,為防止高于3.3V的電壓引入DSP,導致DSP的損壞,繼電器控制信號的輸出采用了光耦器件817進行隔離,繼電器開關側使用了阻容吸收電路來減小在開關開合時的沖擊。具體電路如圖4所示。

2 諧波控制器的軟件設計

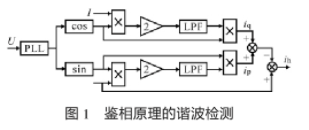

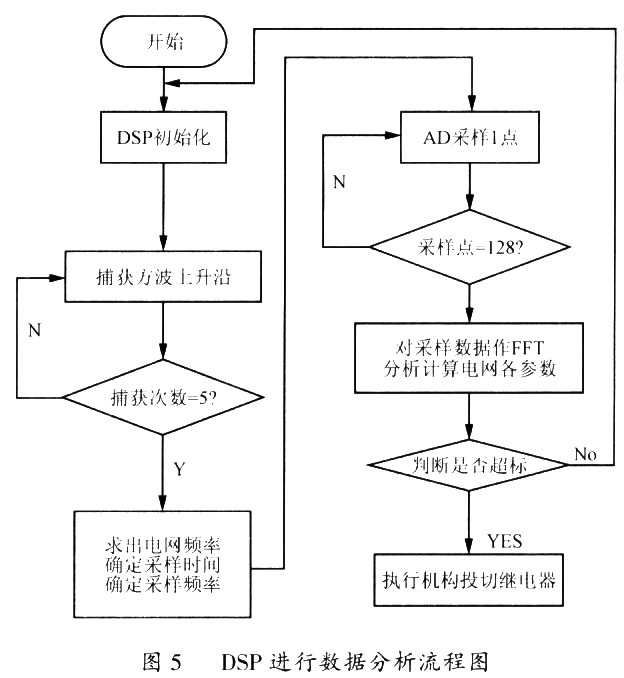

軟件設計的核心就是對信號中的諧波分量進行分析,DSP在兩個信號周期采樣128個點,基于這些采樣點進行快速付里葉變換(FFT)運算,從而分析得到信號中諧波的含量。諧波分量的分析精度取決于FFT的精度和同步采樣。當采樣頻率是信號頻率的整數倍時,即實現同步采樣,采用矩形截斷,并用FFT算法進行頻譜分析,不會產生任何泄漏現象,可以精確重現信號頻譜。如果能自動達到同步采樣,對算法本身的要求就不需要太高,因為,同步采樣后采用矩形窗進行FFT,矩形窗就意味著采樣的數據可以直接作為FFT子函數的輸入。過零檢測電路就是為了實現同步采樣,DSP捕獲方波電路產生的方波上升沿,可以求出方波頻率即信號頻率。根據此頻率可確定采樣時間和兩點間的采樣間隔時間(兩次AD轉換之間的時間),通過這個方法就叮以實現同步采樣,獲得精確的頻譜。每次FFT運算前都會重新根據實際電網情況改變采樣策略,在幾個周期內對電網頻率的變化迅速作出反應,這樣提高測量的可靠性和實吋性。

交流電壓u(t)及電流信號i(t)每個周期進行N次采樣,測得的離散值為u(n)、i(n),得到的離散化電壓、電流有效值和有功功率計算公式為(N為采樣點數)

根據P=UIcosθ可以求出功率因數,進而求得無功。根據FFT的結果可以得出各次諧波的含量,經計算可以得到總的諧波畸變率(THD),為DSP控制繼電器投切濾波器提供了依據。

圖5為DSP進行數據分析的流程圖。

3 抗干擾設計

干擾主要有傳導型和輻射型兩大類,前者表現為干擾電流和電壓,后者表現為干擾電場和磁場。影響智能脫扣器的干擾源有用電設備的浪涌電流;對講機、手機等產生的射頻輻射;智能脫扣器內部的開關電源和斬波釋放電路等。這些干擾源的存在導致程序死掉,將干擾信號引入電流電壓,從而使數據分析結果與實際差距較大,引起繼電器誤投切。為了減少千擾的影響,需要在硬件和軟件上采取相應措施。

3.1 硬件抗干擾

采取的措施有:

1)合理布線,使數字電路地和模擬電路地共點接為懸浮工作方式,即系統各回路的基準電位互相連接在一起而不與大地相連,這樣系統有較強的抗干擾能力;

2)模擬電路地和數字電路地分開接地,最后再匯合到一點;斬波泄放電路在啟動工作后,出現很高的瞬態干擾,把邏輯地(主機)和模擬地(A/D)分開后,這種干擾就降到很低;

3)線路板和元器件表面噴絕緣層,這不僅是防潮和絕緣的需要,而且對防電磁千擾也有很重要的作用;在機殼內涂金屬屏蔽層,形成等電位屏蔽,對電磁干擾也有很大的屏蔽作用;

4)在穩壓電源、隔離變壓器后側安裝濾波線路,這個濾波線路能使火線與零線中的千擾電流得到衰減;

5)弱電和強電之間常常需要隔離,常用的隔離方式有光電隔離、變壓器隔離、繼電器隔離等;本系統中采用光耦器件817對DSP輸出的弱電控制信號與繼電器強電進行隔離,由于光電隔離保證了DSP與繼電器間無電的直接聯系,從而保證了信號的正常傳遞,保證了DSP的安全。

3.2 軟件抗干擾

軟件上抗干擾的方法有以下幾種:

1)為了防止裝置收到干擾進入“死機”狀態,在程序中加入一些監控措施 利用看門狗(watchdog)對程序進行死鎖檢測,在必要的時候自動復位;在未使用的中斷向量區、空白程序區設置軟件陷阱,強迫程序跑飛以后能夠回到正常軌道上來;在必要的地方寫入冗余指令,以調整指令長度,防止程序混亂;

2)對采樣信號進行數字濾波 首先對每一個采樣點進行判別,讓其與相鄰值、前次值以及增值最大值進行比較,根據對稱檢測法、限幅檢測法來判斷是否為干擾信號;對最近采樣的點進行FFT計算得到的數據與前幾次的數據求平均值,舍去“異類”。

此外,在數據處理的算法上進行改進,也能大大提高系統的抗干擾能力,但是,這往往是以犧牲代碼長度為代價的,至于如何取舍視實際項目要求而定。

3.3 其他措施

在本系統中,DSP芯片除了進行數據采集和分析以外,還要實現對鍵盤和液晶顯示的控制,這樣DSP的工作量十分繁重,設計稍不全面就會出現中斷沖突現象,為調試帶來很大的困難。為此,可以采取在系統中添加一塊單片機51芯片,用于管理鍵盤和液晶顯示。現在單片機51芯片的價格十分便宜,系統中引入5l芯片不會導致成本過高。由于在正常運行時候,DSP和單片機通過雙口RAM進行數據交流,其他內部的程序都不會相互干擾,因此,給調試帶來了極大的方便,同時,最大可能地降低了程序跑飛的可能性。

4 結語

無源濾波器是抑制諧波的重要手段,它被廣泛應用于電網的諧波抑制中,目前無源濾波器主要靠手工進行投切,這樣既浪費人力,又達不到理想的效果,不能滿足電能質量日益提高的要求。根據誰污染誰治理的原則,諧波污染也要由用戶自己消除,因此,研制一種能對諧波進行監測控制的裝置既方便了用戶,又有廣闊的市場前景。

-

dsp

+關注

關注

553文章

7987瀏覽量

348773 -

控制器

+關注

關注

112文章

16335瀏覽量

177818

發布評論請先 登錄

相關推薦

基于DSP28335處理器實現單相APF控制器的硬軟件設計

采用DSP芯片的MELP聲碼器的算法設計方案

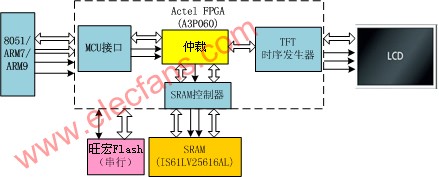

采用Actel FPGA的TFT控制器技術設計方案

基于DSP+FPGA的磁鐵電源控制器的設計

磁鐵電源控制器的設計方案分析

基于DSP的步進電機驅動器設計方案

ADI-ADuM隔離DCDC控制器參考設計方案

ADIDAuM隔離DCDC控制器參考設計方案

淺談采用DSP的諧波控制器的設計方案

淺談采用DSP的諧波控制器的設計方案

評論