目錄

前言... 1

1、DDR4介紹... 2

1.1、DDR4與DDR3不同之處... 2

1.2、POD 和SSTL的比較... 2

1.3、ODT控制... 4

1.4、DDR4高速訊號傳輸技術... 5

2、DDR4 Simulation Challenges. 7

2.1、使用IBIS 5.0 power aware nodel7

2.2、使用Statistical-based analysis. 8

2.3、Random bit pattern with DBI coding. 8

2.4、Unit Interval(UI)單位時間間隔... 9

3、DDR4 3200 Simulation. 9

3.1、no on-die de-cap. 12

3.2、on-die de-cap at TX. 13

3.3、on-die de-cap at TX and Rx. 17

3.4、TransientEYE vs. QuickEYE. 18

3.5、PRBS vs. DBI patterns. 19

4、Compliance Test21

4.1、[Circuit] [Tool Kits] [Virtual Compliance for DDR4]21

4.2、Presetting dialog for assigning net mapping. 21

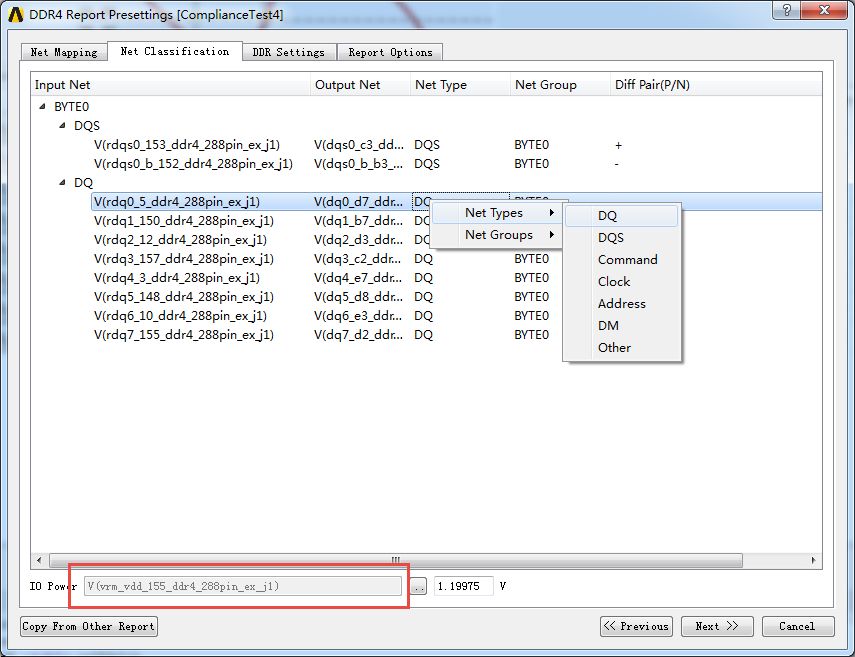

4.3、Net Classification for net type, group and IO power22

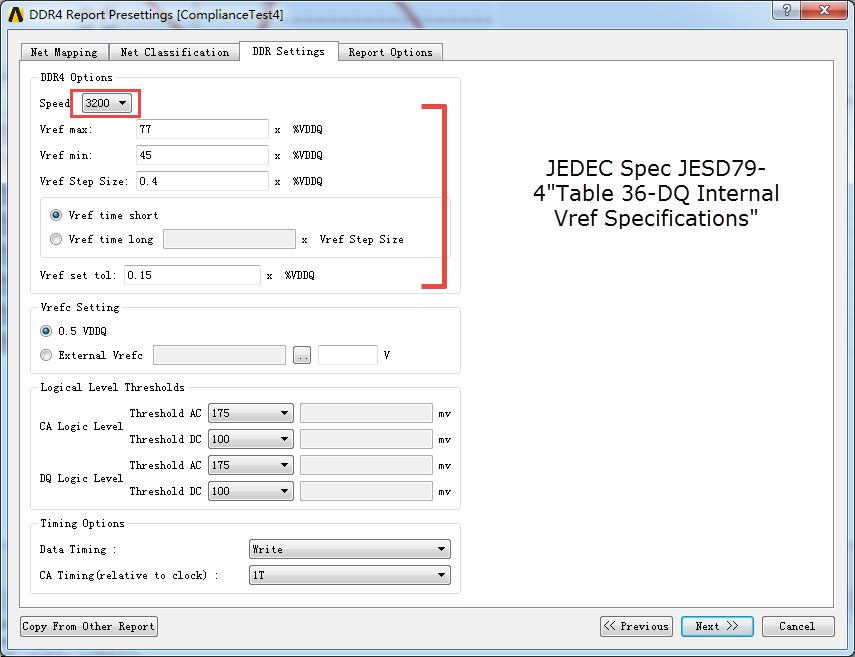

4.4、DDR settings. 22

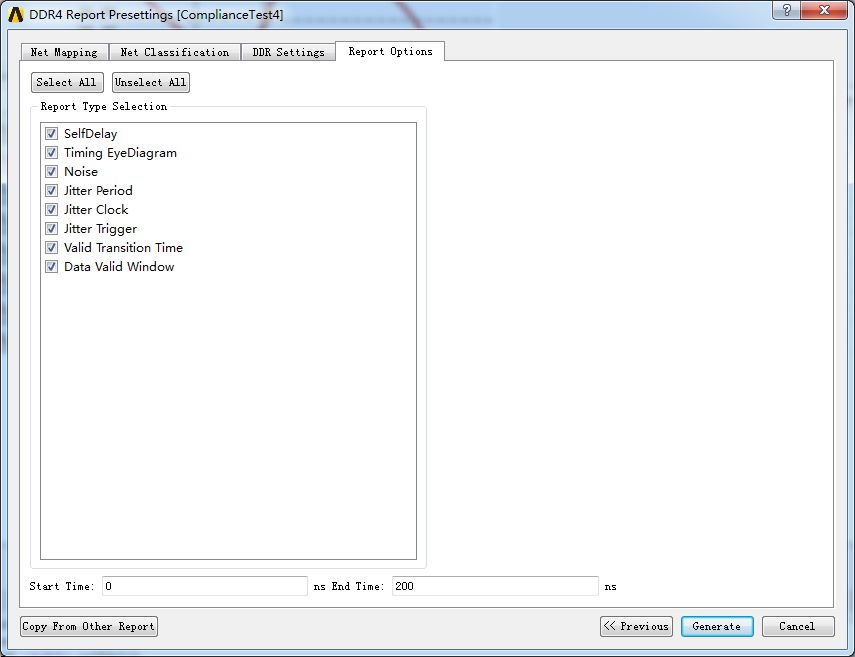

4.5、Report Options. 24

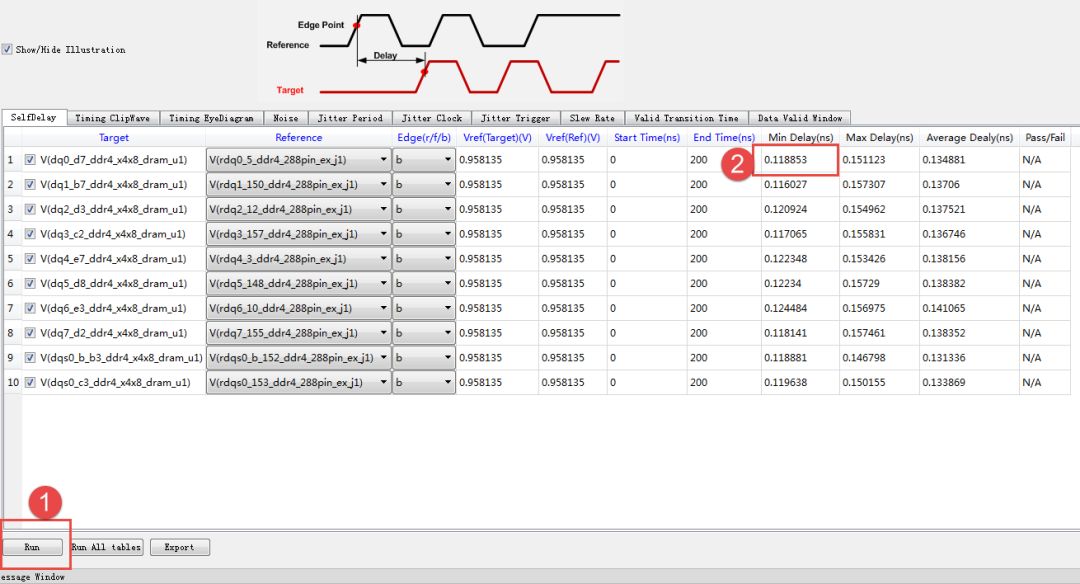

4.6、Self-Delay. 24

4.7、Switch to different tabs and press [Run][Run All tables] to get other reported parameters.26

4.8、Sing-off report28

5、問題與討論Q&A.. 29

參考... 33

前言

DDR4作為目前最新一代的量產SDRAM記憶體,其高速低功耗特性滿足了眾多消費者的需求。但是另一方面,對于硬件設計人員來講,DDR4的高速率非常容易引起SI問題,一旦出現DDR4 Margin測試Fail之類的問題,會讓很多設計者感到頭疼,Debug過程非常困難。

本文介紹了DDR4技術的特點,并簡單介紹了ANSYS工具用來仿真DDR4的過程。文章中主要介紹的對象為DDR4 3200MHz內存,因為硬件極客對DDR4性能的不斷深挖,目前已經有接近5000MHz的量產內存,比如芝奇推出的TridentZ系列速度最快可達到4700MHz,并且還在不斷提高。

本文參考***一個論壇,筆者在學習的過程中,在原作的基礎上進行整理,并且參考鎂光和DesignCon論壇諸多經典文章,總結出了個隨筆,后來發現文章過于冗長,故又刪減了一半多帶給大家。因筆者水平有限,錯誤之處在所難免,希望各位讀者批評指正!

1、DDR4介紹

1.1、DDR4與DDR3不同之處

相對于DDR3, DDR4首先在外表上就有一些變化,比如DDR4將內存下部設計為中間稍微突出,邊緣變矮的形狀,在中央的高點和兩端的低點以平滑曲線過渡,這樣的設計可以保證金手指和內存插槽有足夠的接觸面從而確保內存穩定,另外,DDR4內存的金手指設計也有明顯變化,金手指中間的防呆缺口也比DDR3更加靠近中央。當然,DDR4最重要的使命還是提高頻率和帶寬,總體來說,DDR4具有更高的性能,更好的穩定性和更低的功耗,那么從SI的角度出發,主要有下面幾點, 下面章節對主要的幾個不同點進行說明。

| Items spec | DDR3 | DDR4 |

| Voltage(VDD/VDDQ/VDP) | 1.5 | 1.2 |

| Rate(Mbps) Data | 1600 | 3200 |

| Vref | External(VDD/2) | Internal(Training) |

| Data IO | SSTL | POD |

| Bus Inversion(DBI) Data | No | Supported |

表1DDR3和DDR4差異

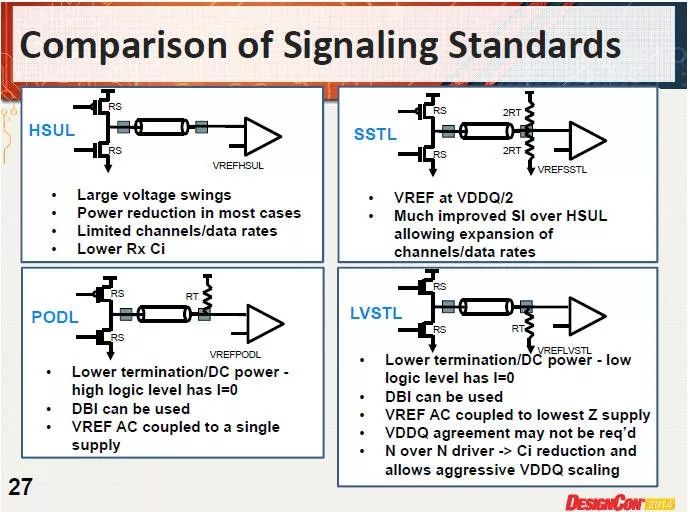

1.2、POD 和SSTL的比較

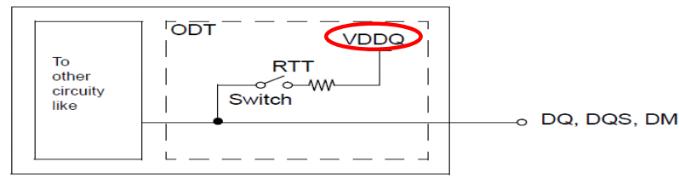

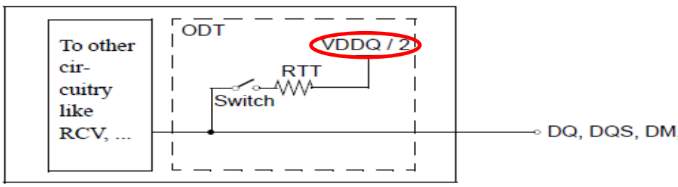

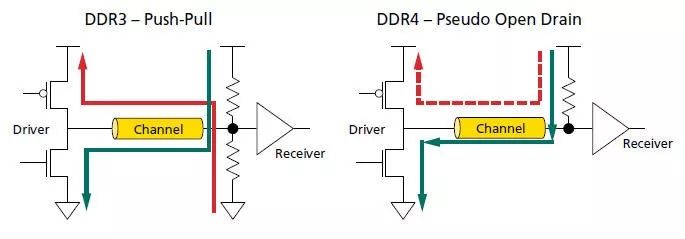

POD作為DDR4新的驅動標準,最大的區別在于接收端的終端電壓等于VDDQ,而DDR3所采用的SSTL接收端的終端電壓為VDDQ/2。這樣做可以降低寄生引腳電容和I/O終端功耗,并且即使在VDD電壓降低的情況下也能穩定工作。其等效電路如圖1(DDR4), 圖2(DDR3)。

圖1 POD ((Pseudo Open Drain)

圖2 SSTL(Stub SeriesTerminatedLogic)

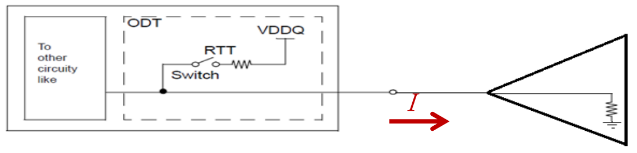

可以看出,當DRAM在低電平的狀態時,SSTL和POD都有電流流動

圖3 DDR4

圖4 DDR3

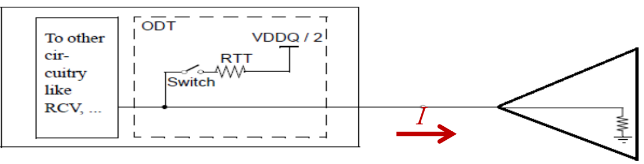

而當DRAM為高電平的狀態時,SSTL繼續有電流流動,而POD由于兩端電壓相等,所以沒有電流流動。這也是DDR4更省電的原因。

圖5 DDR4

圖6 DDR3

對于DDR4的IO來說,drive high時幾乎不耗電(下圖右的紅色虛線是電流路徑),這就是為何采用DBI+POD機制具有優勢的原因[3]p.15,[9]p.80。

圖7 DDR3和DDR4驅動機制

DDR4雖然drive high時候不耗電,但是在drive low的時候會消耗相比于SSTL兩倍的電。所以,勝點的關鍵在于較少輸出0的數量。如果將要輸出的數據bus上0比1多,DDR4會將數據翻轉以達到降低功耗的目的。

1.3、ODT控制

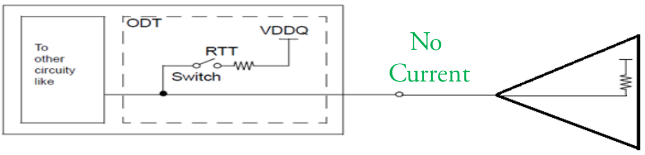

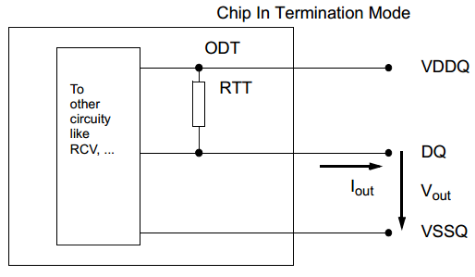

為了提升信號質量, 從DDR2開始將DQ, DM, DQS/DQS#的Termination電阻內置到Controller和DRAM中, 稱之為ODT (OnDieTermination)。Clock和ADD/CMD/CTRL信號仍需要使用外接的Termination電阻。

圖8On Die Termination

在DRAM中,On-Die Termination的等效電阻值通過Mode Register (MR)來設置,ODT的精度通過參考電阻RZQ來控制,DDR4的ODT支持240, 120, 80, 60, 48, 40, 34 歐姆。

和DDR3不同的是,DDR4的ODT有四種模式:Data termination disable, RTT_NOM,RTT_WR, 和RTT_PARK。Controller可以通過讀寫命令以及ODTPin來控制RTT狀態,RTT_PARK是DDR4新加入的選項,它一般用在多Rank的DDR配置中,比如一個系統中有Rank0,Rank1以及Rank2, 當控制器向Rank0寫數據時,Rank1和Rank2在同一時間內可以為高阻抗(Hi-Z)或比較弱的終端(240,120,80,etc.), RTT_Park就提供了一種更加靈活的終端方式,讓Rank1和Rank2不用一直是高阻模式,從而可以讓DRAM工作在更高的頻率上。

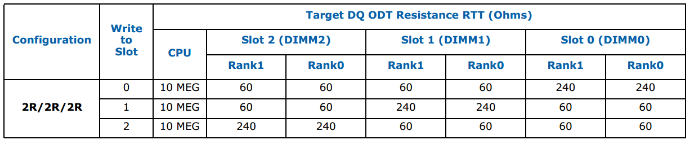

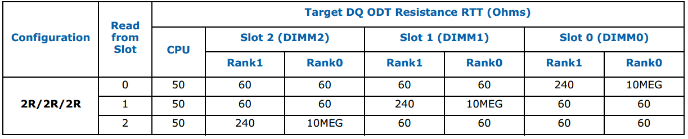

一般來說,在Controller中可以通過BIOS調整寄存器來調節ODT的值,但是部分Controller廠商并不推薦這樣做,以Intel為例,Intel給出的MRCCode中已經給出了最優化的ODT的值,理論上用戶可以通過仿真等方法來得到其他ODT值并在BIOS中修改,但是由此帶來的所有問題將有設計廠商來承擔。下面表格是Intel提供的優化方案。

表2DQ Write ODT Table for 3DPC

表3DQ Read ODT Table for 3DPC

1.4、DDR4高速訊號傳輸技術

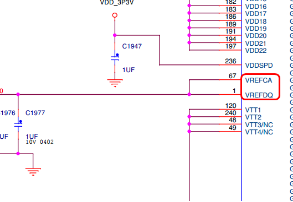

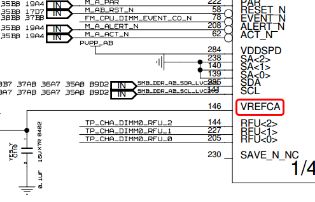

眾所周知,DDR信號一般通過比較輸入信號和另外一個參考信號(Vref)來決定信號為高或者低,然而在DDR4中,一個Vref卻不見了,先來看看下面兩種設計,可以看出來,在DDR4的設計中,VREFCA和DDR3相同,使用外置的分壓電阻或者電源控制芯片來產生,然而VREFDQ在設計中卻沒有了,改為由芯片內部產生,這樣既節省了設計費用,也增加了Routing空間。

圖9DDR3設計

圖10 DDR4設計

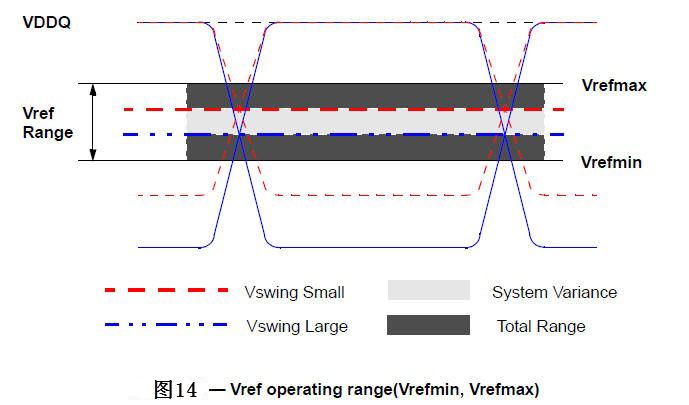

DDR3采用SSTL,Vref=VDDQ/2;DDR4采用PODL,Vref是不固定的,會隨VDDQ的AC變動而變動Vref=((2Rs+Rt)/(Rs+Rt))*VDDQ/2 [9]p.18/25/27。

圖11SSTL和PODL技術區別

因為Vref的不同,Vih/Vil都會有差異,可以通過調整ODT來看Vref的區別,用一個仿真的例子來說明。對于DDR3,調整ODT波形會上下同步浮動,而調整DDR4 OOT的時候,波形只有一邊移動。

圖12DDR3仿真結果

圖13DDR4仿真結果

DDR4增加了DBI(Data BusInversion)、CRC(Cyclic Redundancy Check)、CA parity等功能,讓DDR4記憶體在更快速更省電的同時亦能改善資料傳輸及儲存的可靠性。[2],[9]p.20,[14]p.6

2、DDR4Simulation Challenges

2.1、使用IBIS5.0 power aware nodel

鎂光的文件【23】說明提供IBIS 5.0 power aware model,供做DDR4 PI以及SS0模擬,這些模型內含【Composite Current】Data,可以讓模擬更準確。鎂光是業界做IBIS model做的非常好的典范,也感謝其在官網大方分享DDR4 IBISSPICE model。

注意不要抓到沒有【CompositeCurrent】Data的舊model,那就不是IBIS 5.0 power aware model

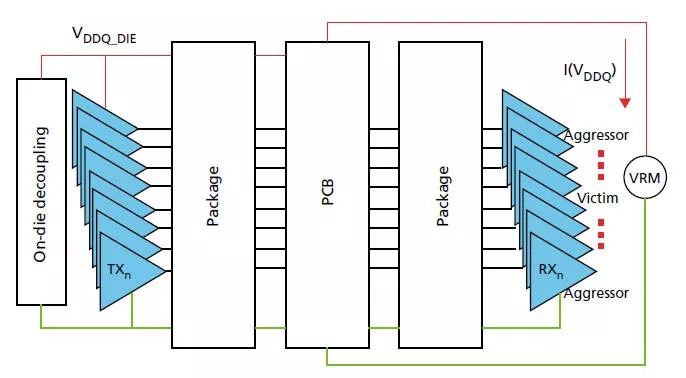

鎂光還提供on-die die-capmodel.ckt(VDDQ-VSSQ),供IBIS模擬時外掛,并且在文件中強調模擬必須考慮這些部分才能跟HSPICE model一樣準確。而這one-die de-cap從文件的示意圖來看【23】p.6,只掛在TX端。

圖15DDR4拓撲

2.2、使用Statistical-basedanalysis【13】【18】

DDR4要求BER=1e-16下的規格,通過使用IBIS power aware model與Statistical-basedanalysis,可以有效的評估DDR4設計優劣。

2.3、Random bit pattern with DBI coding【3】p.6

DBI是DDR4一個非常關鍵的省電技術,直接會影響暫態電流與眼圖的模擬結果,這需要整個byte(8 bits)一起考慮。目前的方法先把整組random bit pattern整理過,再喂給circuit simulation。

圖16DBI技術

注意:要模擬DDR4通道內,所有的DQ/DQS/Addr/Cmd同時動作時的SI與PI(SSO/SSN),最好的做法是用IBIS 5.0 power aware model與Transientanalysis。QuickEYE雖然可以看眼圖,并且得到與Transientanalysis極為相似的結果,但無法做SI+PI分析,原因是QuickEYE是單獨激發每個EYESource得到step response,不是同時激發,也就是無法考慮SSN效應。

2.4、Unit Interval(UI)單位時間間隔

UI是做眼圖分析十分重要的一個參數,在理解單位時間間隔的基礎后,方可以容易的定義與眼圖的時間軸上的失真相關的術語。例如:在描述規范標準和數據表中的抖動特性時,通常使用術語“UI”。

如圖所示,不論數據速率如何,“單位時間間隔”被定義為歸一化的數據位寬度。由于單位時間間隔基本上與比特數相同,1個數據位的寬度為1個單位時間間隔。水平時間軸可以以1秒或單位時間間隔為單位來表示。例如:我們需要仿真的對象為DDR4 3200Mbps,在3200Mbps的數據流中,1個單位時間間隔為1/3.2e9=312.5ps。

圖17 仿真單位時間間隔

3、DDR43200 Simulation

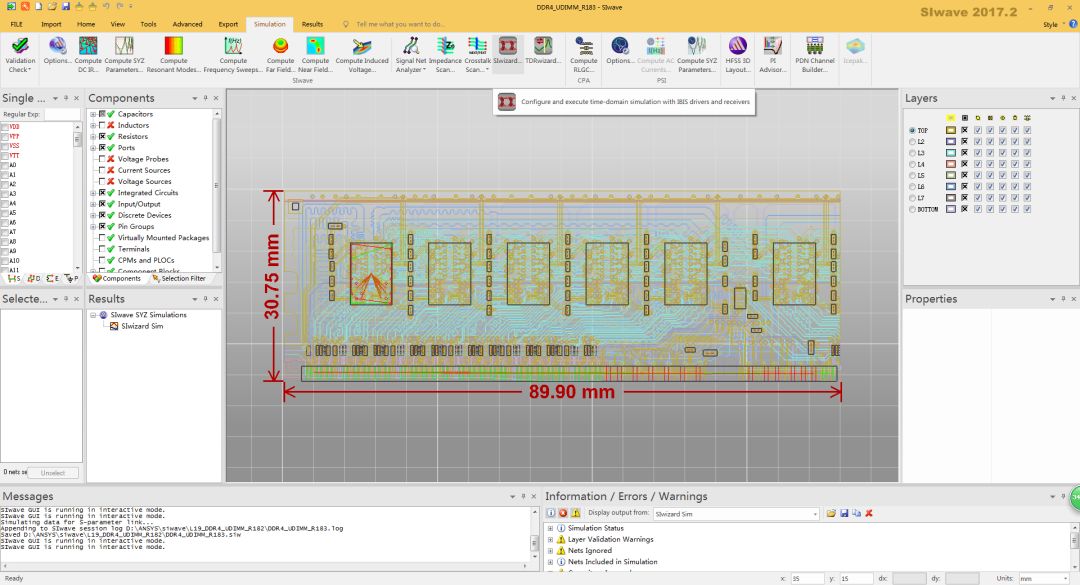

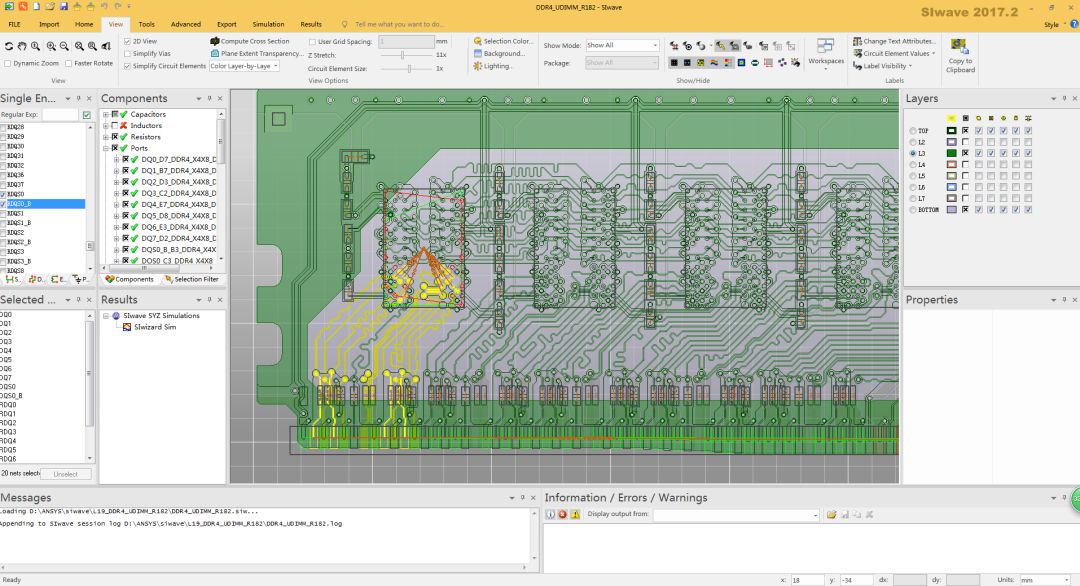

使用鎂光DDR4 MT40A512M16JY-075E(IBIS 5.0 power aware model),配合Siwave 2017.2內的Siwizard功能自動在Designer內產生電路,自動連接Siwave內的DDR4真是DIMMmodel,做DDR4 3200的模擬分析。

圖18PCB導入siwave

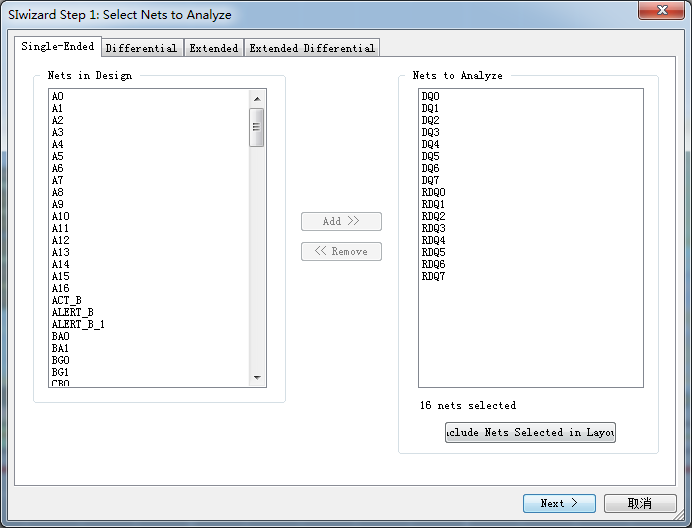

在導入DDR4的PCB文件后,按照Siwave Workflow Wizard完成PCB文件的設置,然后選擇Simulation菜單下的Siwizard,添加需要仿真的DQ/RDQ單端走線和DQS/RDQS差分走線,這幾組走線共同組成了內存U1的數據DQ/DQS信號線。

圖19 左側內存顆粒的DQ/DQS走線示意

圖20 Siwizard設置向導

將J1設置為Driver,U1設置為Receiver,IBIS component選擇我們需要仿真的MT40A512M16JY,IBIS Model選擇對應的DQ/DQS,使仿真電路工作在3200Mhz頻率下。

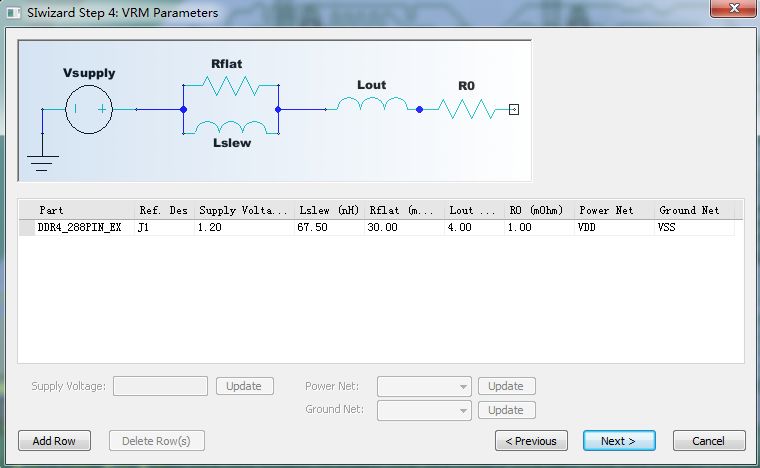

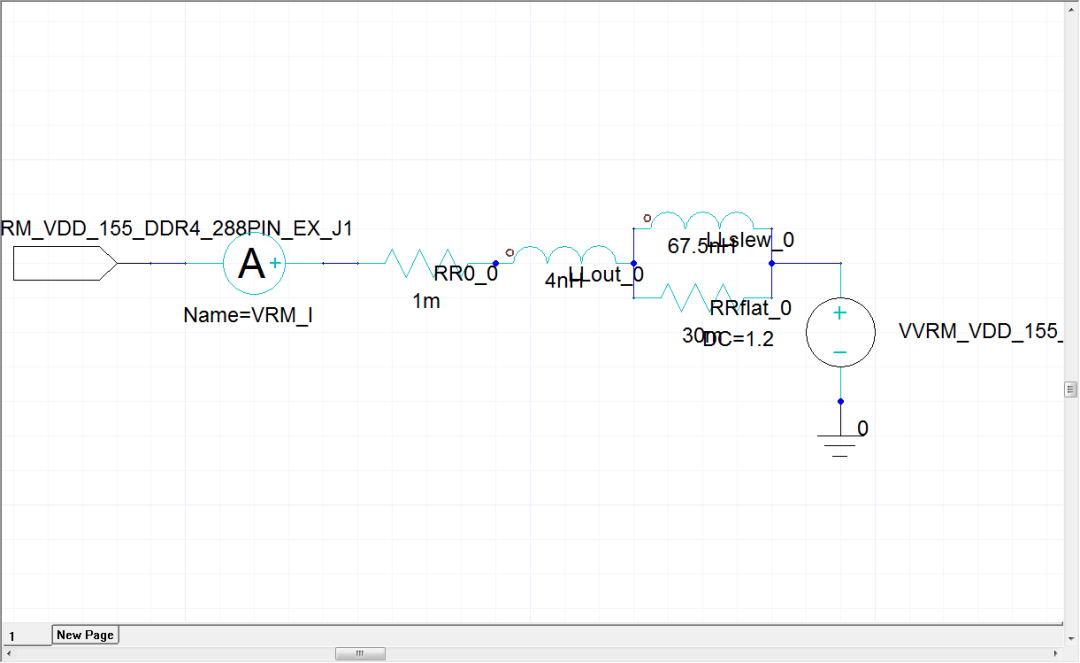

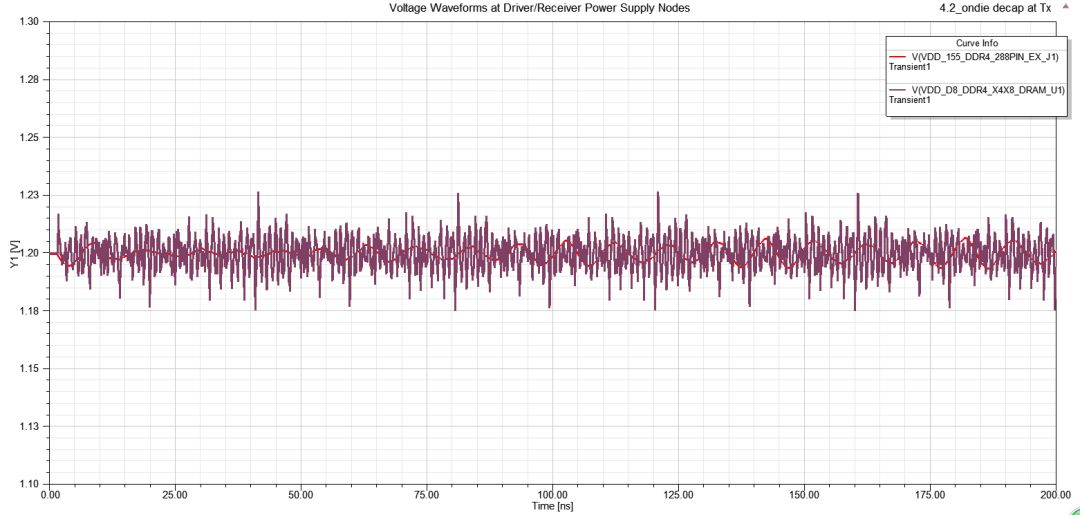

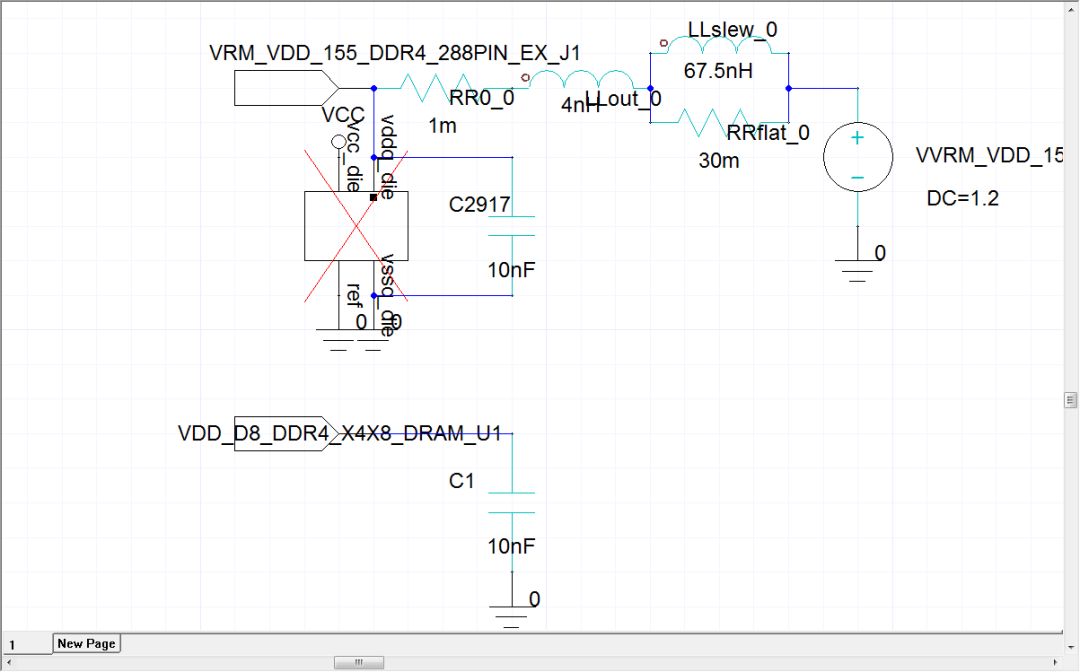

VRM參數中設置驅動電壓為1.2V,寄生電感67.5nH,并聯阻抗30mΩ,輸出電感4nH,輸出電阻1mΩ。

圖21 Siwizard設置向導

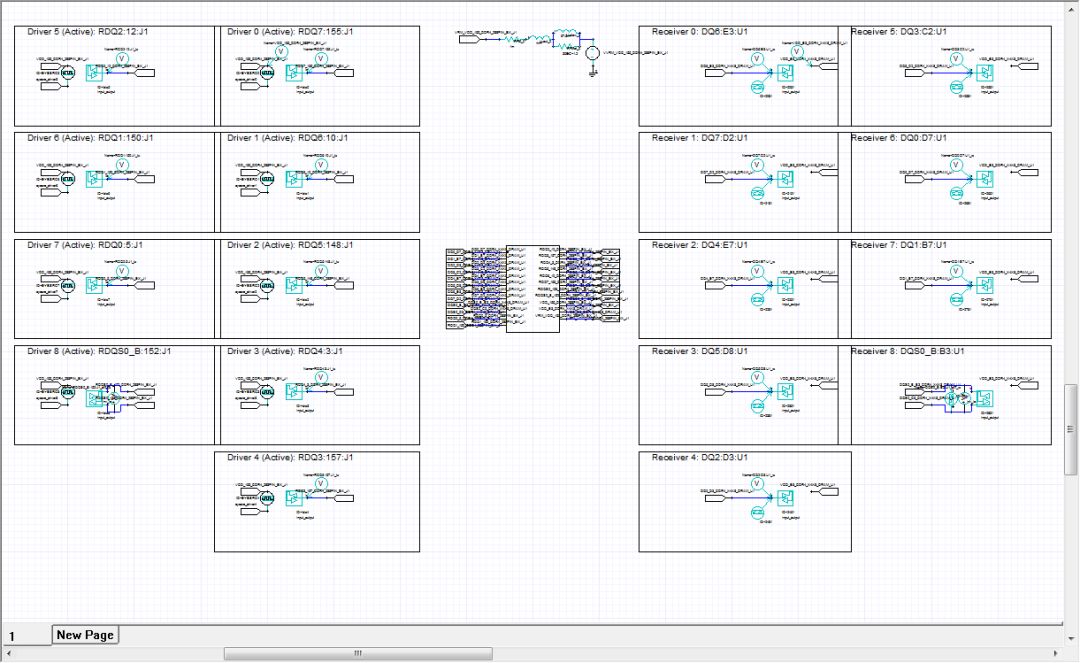

下圖所有的電路連接(DQsingle-end, DQS differential pair),以及上圖在Siwave中做pin group與下方的port,不管是signal nets for SI或P/G nets for PI,所有連接與設定工作都是自動完成。PCB與電路范例

圖22circuit中生成的電路拓撲

整個過程從Siwave窗口開始全部自動完成,因為我們需要查看VRM電流紋波情況,所以需要手動終止,在VRM網絡上手動添加Current probe,設置完成后再Circuit工程樹中,手動開始analyze。

圖23VRM上添加電流probe

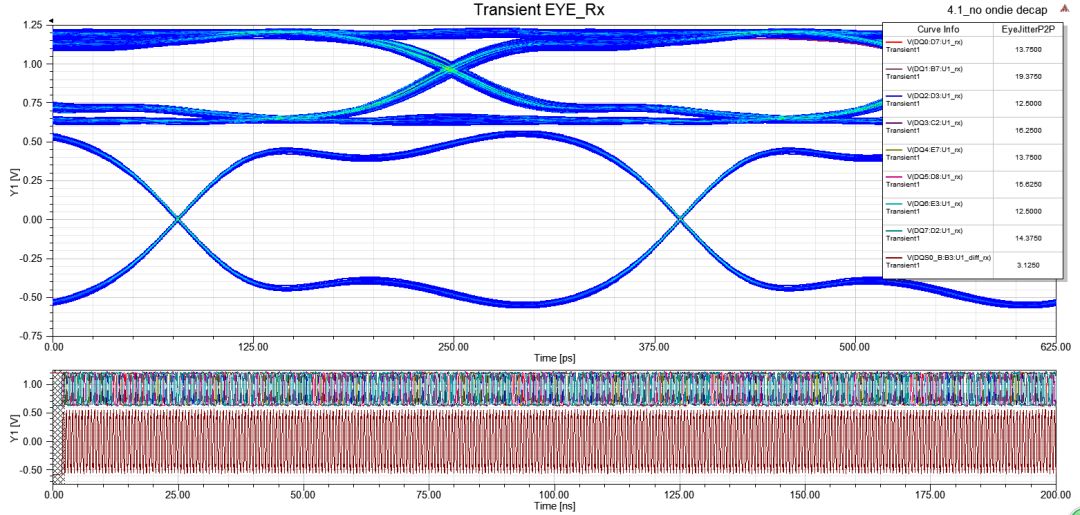

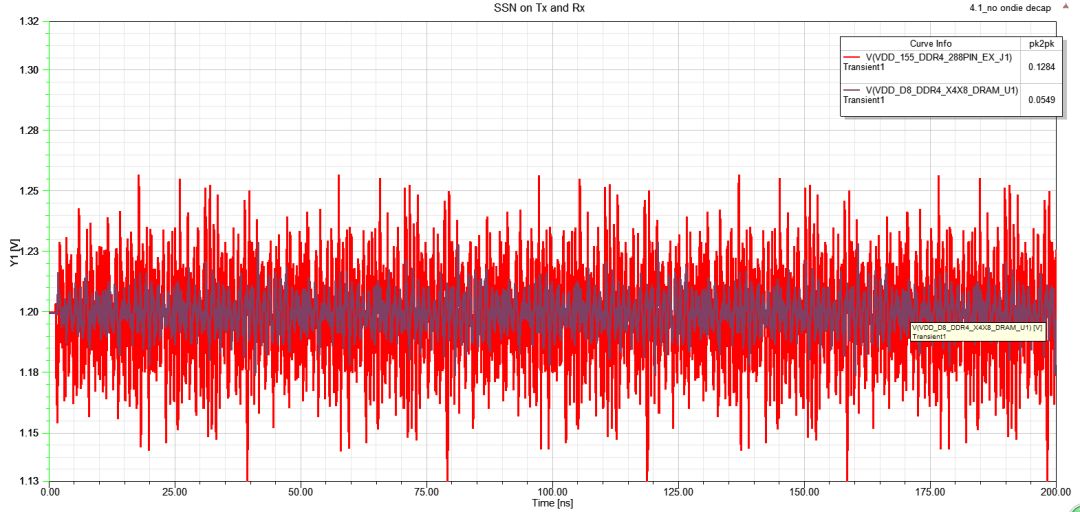

3.1、no on-die de-cap

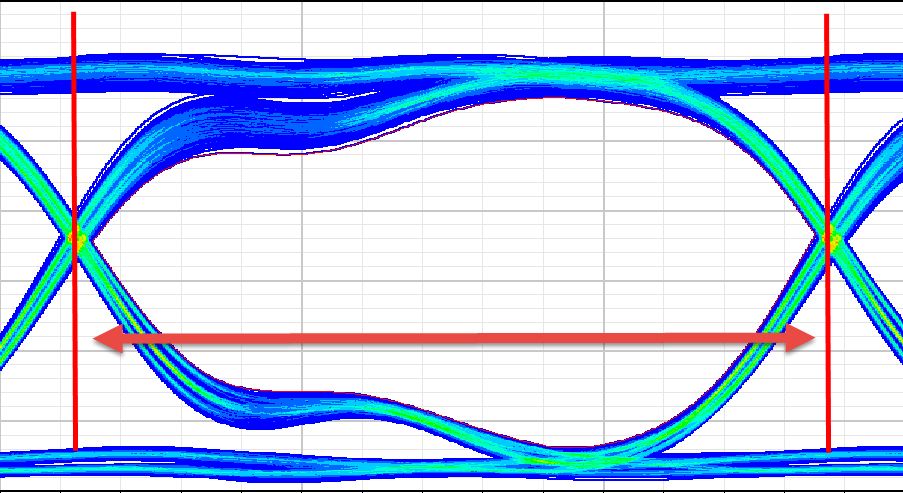

下圖是DDR4 3200MHz DQ【0:7】and DQS pair(allwith DOT48),可以清楚的看到有開啟ODT時,DQ眼圖中間交叉點位置上移,但訊號高準位維持在1.2V,DQS差分信號的眼圖交叉點則是維持在0V。DQS的jitter比DQ小是因為灌clock pattern,其它DQ則灌PRBS patter。

圖24 noon-die de-cap下的DQ/DQS眼圖和VRM電壓紋波(SSN)

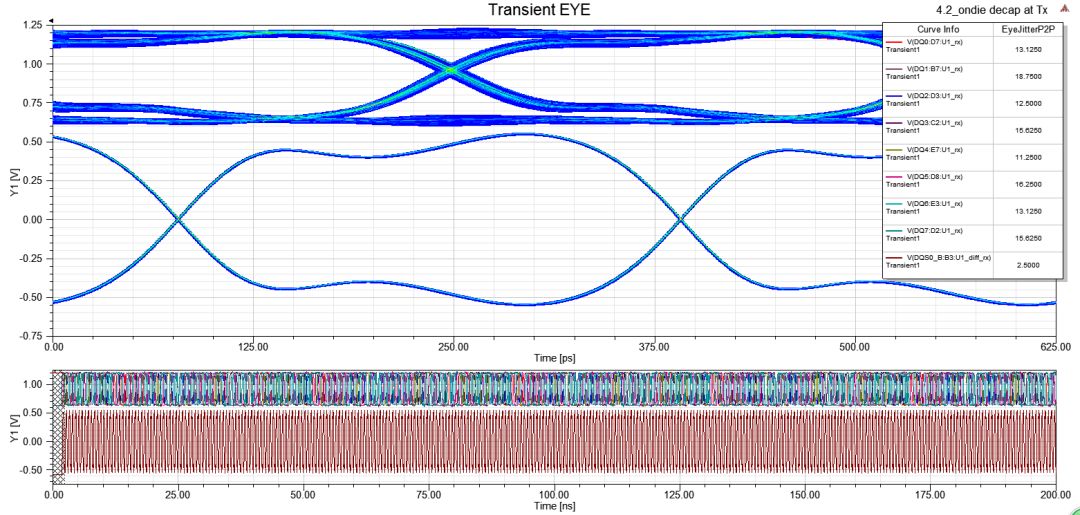

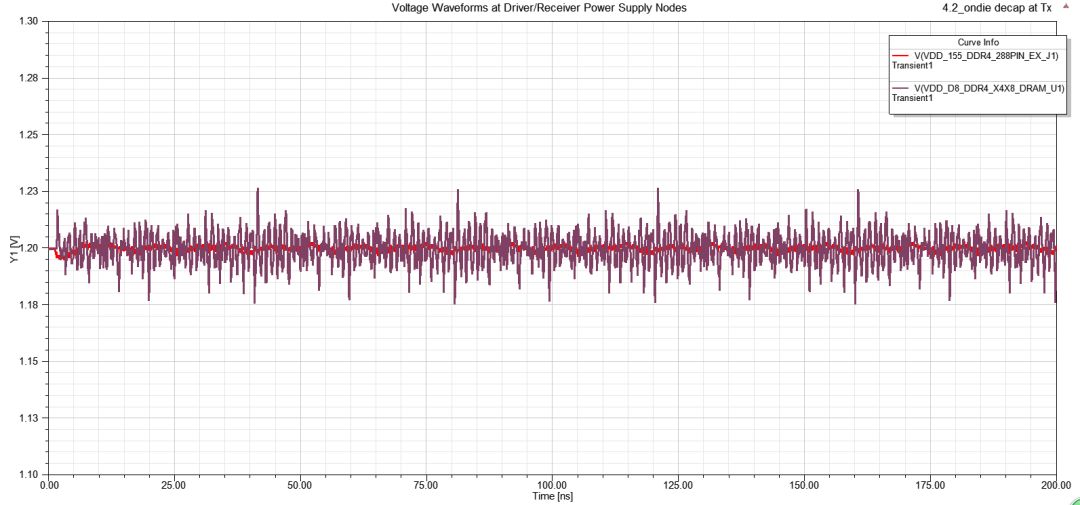

3.2、on-die de-cap at TX

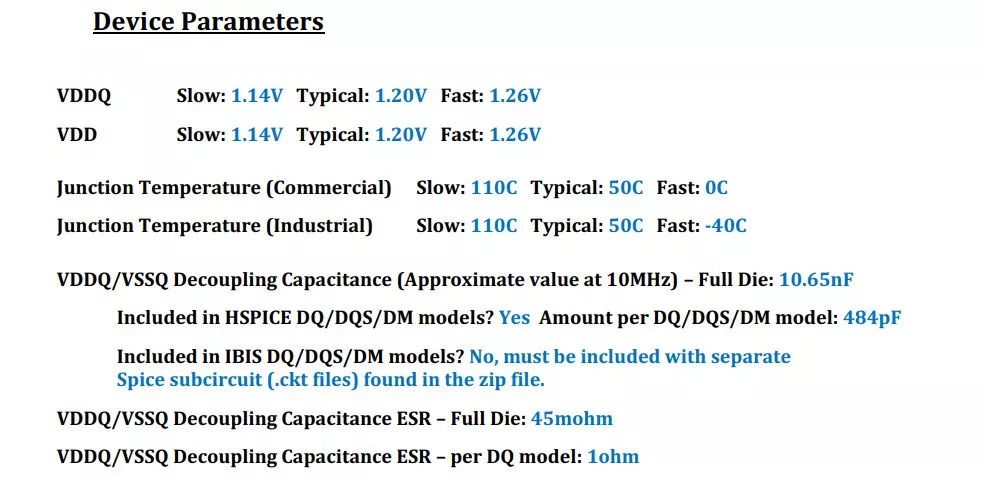

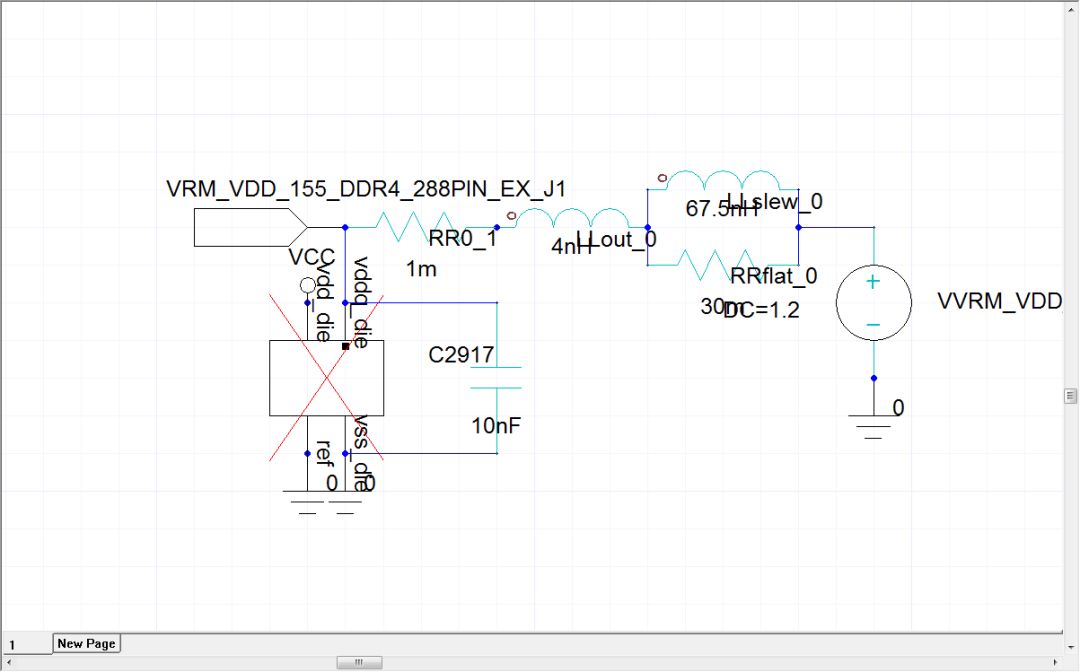

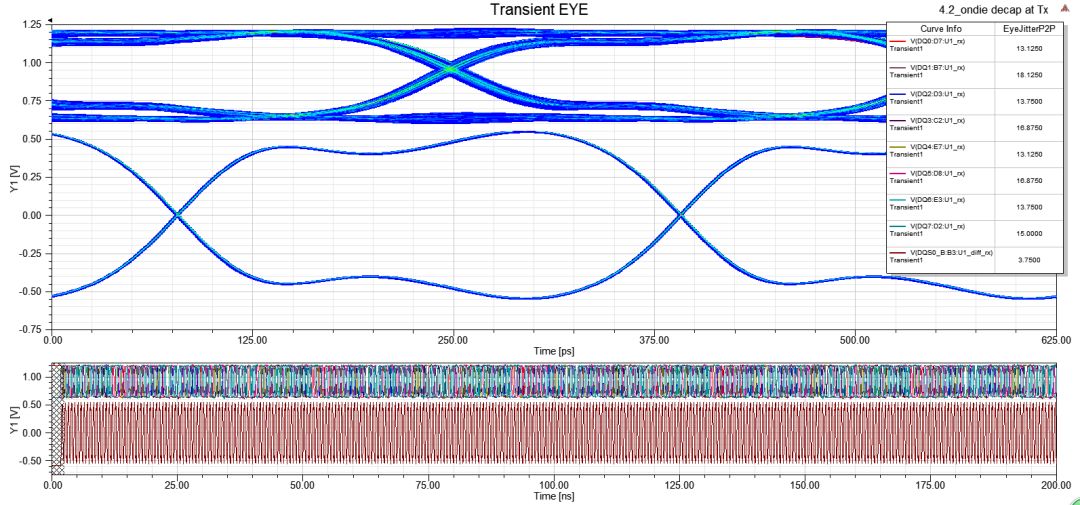

如果在Tx端VRM加on-die de-cap 10nF,會看到Tx端SS0 of P/G明顯變好,而這10nF是參考鎂光的IBIS/SPICE quality report的說明(484pF DO pin)。為了對比,這里先將on-die de-cap設置為開路,手動添加10nF替代導入的模型。

圖25 鎂光datasheet中關于VDDQ/VSSQ Decoupling Capacitance取值的描述

圖26 采用10nF取代on-die de-cap模型

圖27VRM接10nF電容后的DQ/DQS眼圖和電壓紋波

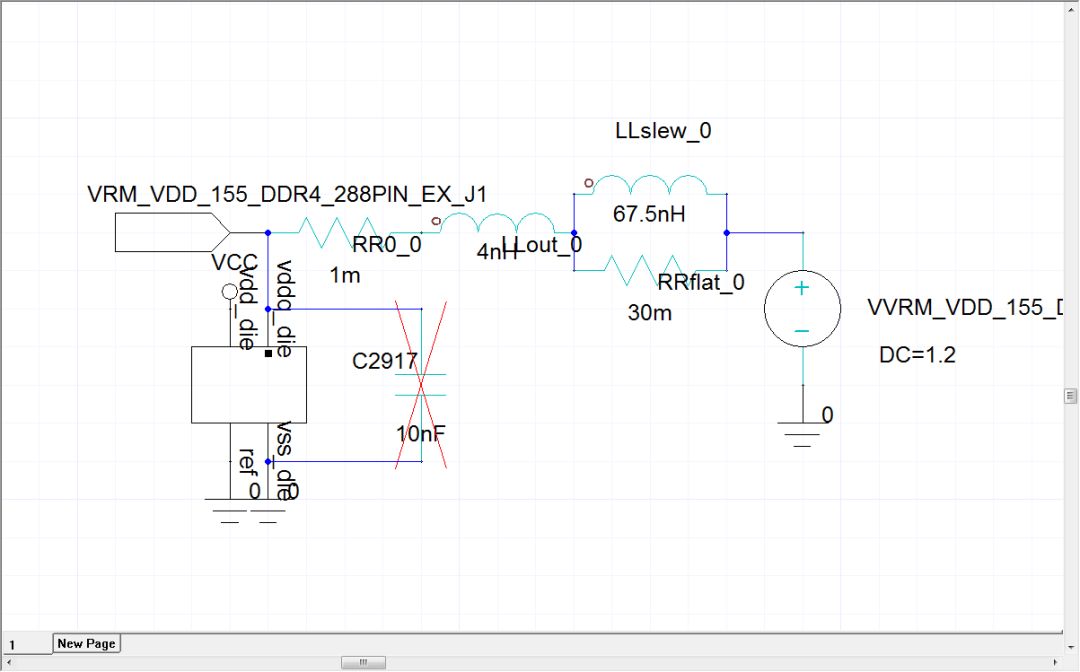

作為對比,取消添加的10nF電容,將on-die de-cap模型設置為工作模式。可以看到結果與手動采用10nF電容時相同。

原文作者在其帖子中提到,掛鎂光提供的de-capmodel時并沒有效果。個人猜測可能是其在導入或者仿真過程中出現錯誤造成的。

圖28 采用on-die de-cap取代10nF模型

圖29 VRM外接on-die de-cap下的DQ/DQS眼圖和電壓紋波

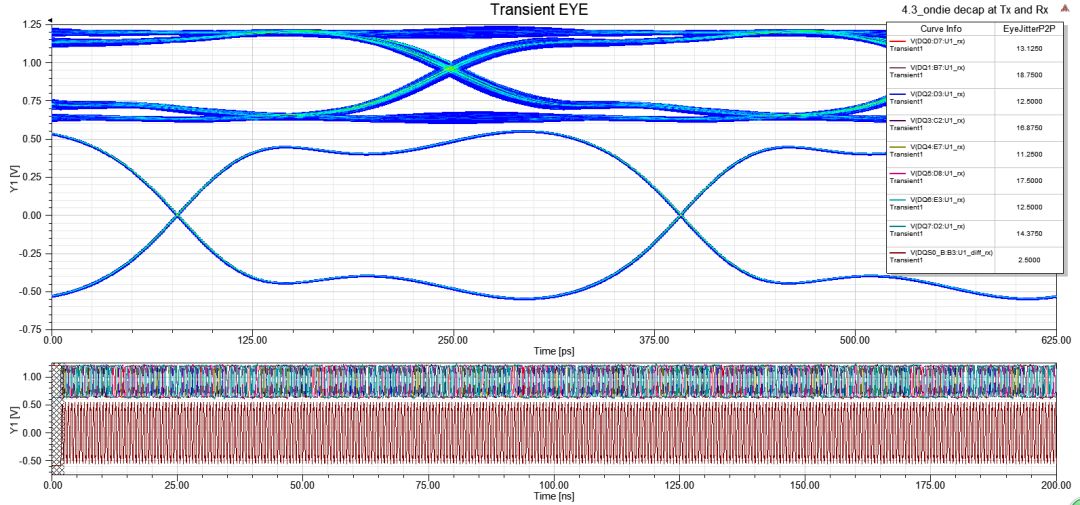

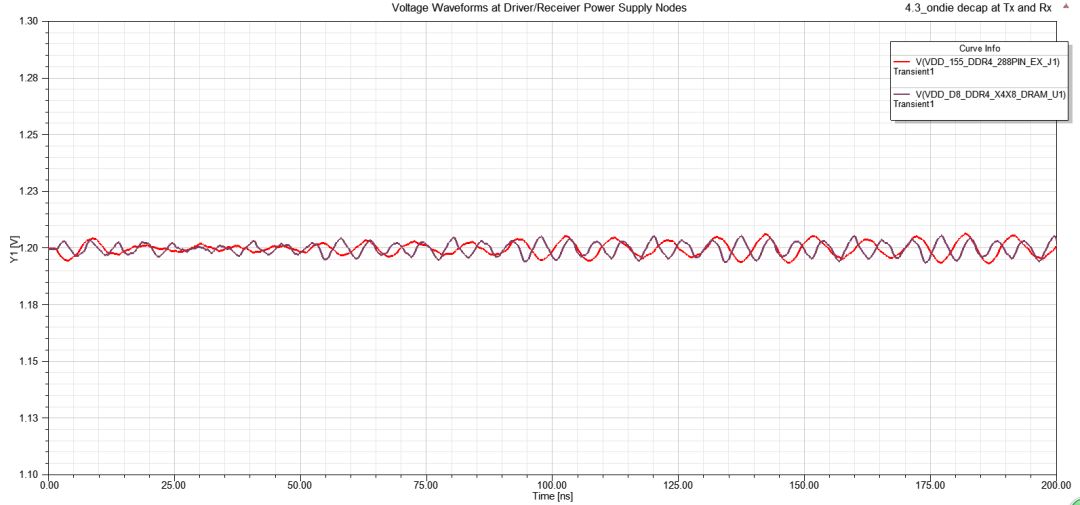

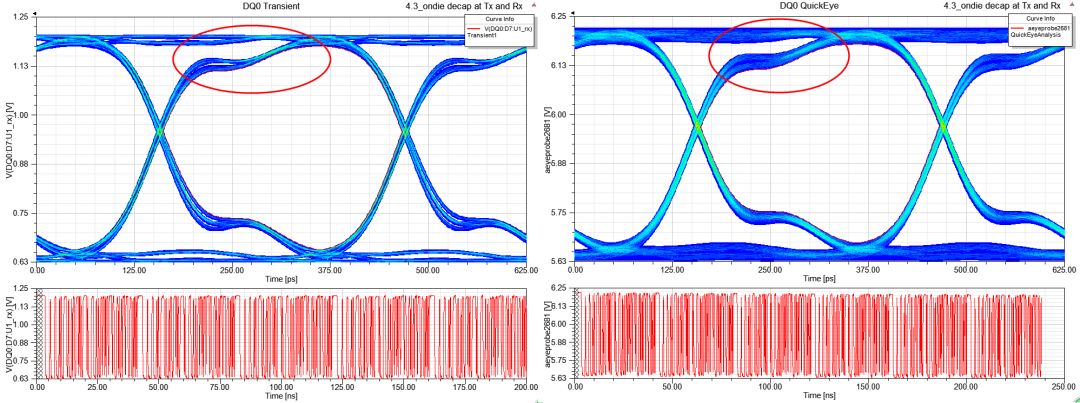

3.3、on-die de-cap at TX and Rx

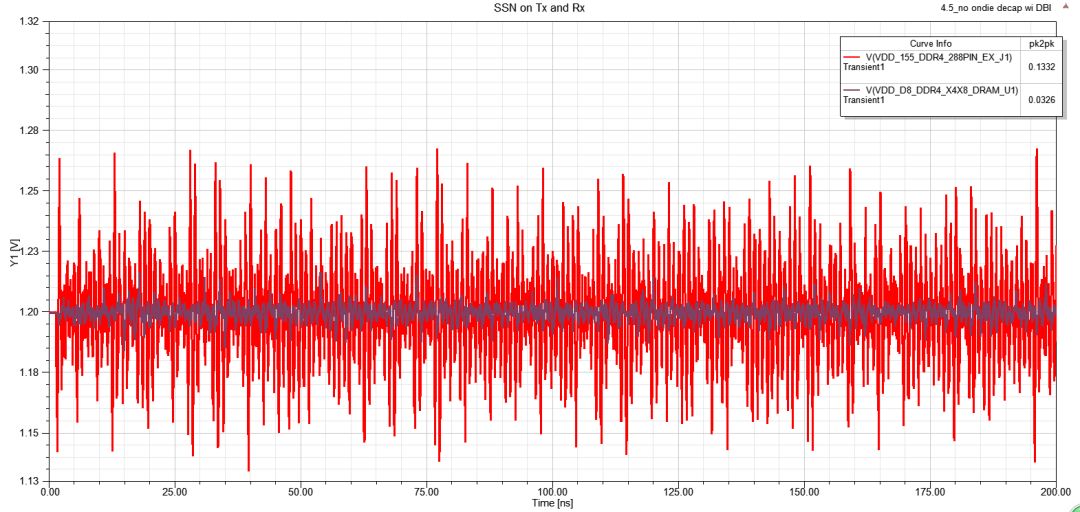

此例就算Tx與Rx端都掛on-die de-cap,P/G上的SSN確實有明顯改善,但眼圖的p-p jitter卻沒有太大差異,主因是此處的jitter是ISI與DDI引起,與bit pattern和crosstalk比較有關,PI的影響是其次。

圖30 Tx與Rx端都掛10nF電容

圖31 Tx與Rx端都掛10nF電容下的DQ/DQS眼圖和電壓紋波

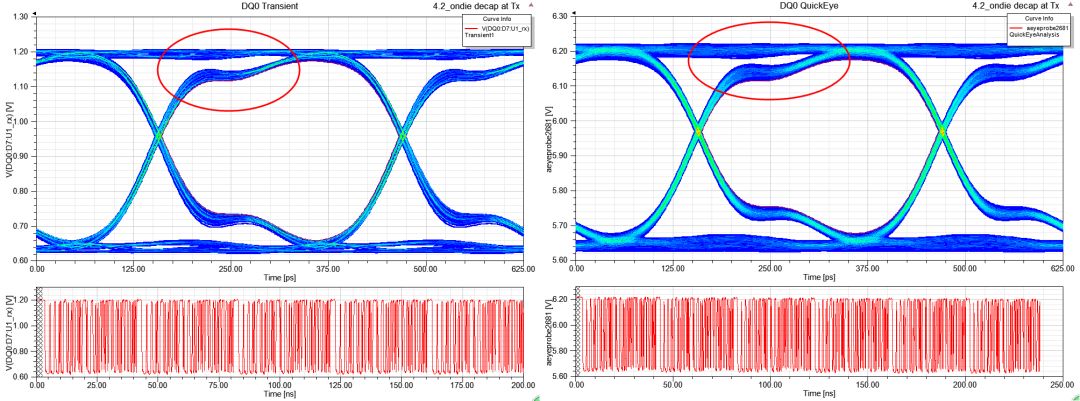

3.4、TransientEYE vs. QuickEYE

從下圖可以看出TransientEYE比起QuickEYE眼圖,在high level的軌跡略粗一些,這就是SSN貢獻的效應,QuickEYE是看不出來的。

注:QuickEYE結果來自eyeprobe

3.4.1、no on-die de-cap

圖32 TransientEYEvs. QuickEYE

3.4.2、on-die de-cap atTx and Rx

圖33 TransientEYEvs. QuickEYE

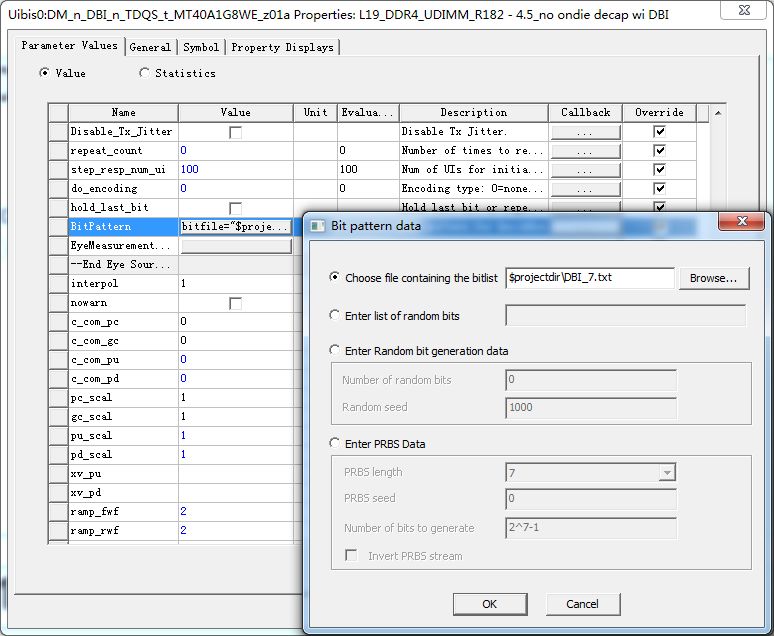

3.5、PRBS vs. DBI patterns

3.5.1、Compare SSN:Rx端的SSN明顯變小

前面介紹了DBI技術,DBI技術的核心在于讓DDR4的高電平盡可能多,當8組DQ信號中低電平占據多數時,DBI將會對所有信號進行翻轉。Circuit中無法自動識別DDR4中的信號邏輯,所以需要手動進行仿真設置,將Driver端的Eyesource刪除,將IBIS模型中的Bitpattern改寫為手動調用外部數據。下表為所有傳輸數據,可以看到DBI_0~DBI_7共8組DQ信號的高電平數量始終≥4,包含了所有可能的組合模式。

| DBI_0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| DBI_1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| DBI_2 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| DBI_3 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

| DBI_4 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |

| DBI_5 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 |

| DBI_6 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 |

| DBI_7 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

表4DBI信號bit數值

圖34 手動模式下調用表4數值

圖35DBI技術前后電壓紋波對比(后面為DBI開啟)

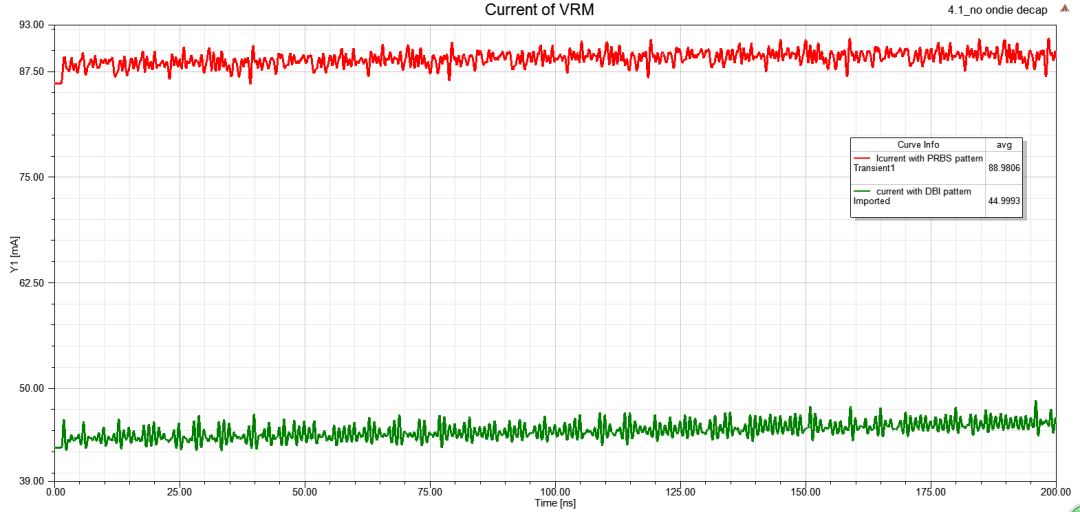

3.5.2、Compare currentconsumption:current reduction 50%,amazing!!

圖36DBI技術下VRM電流值對比

4、Compliance Test

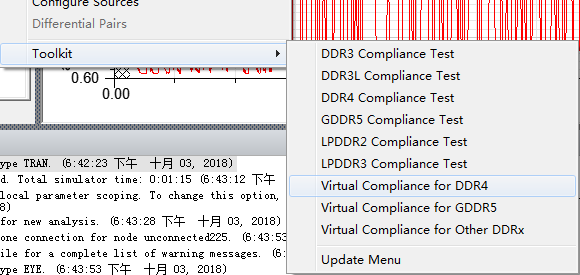

4.1、[Circuit] [Tool Kits] [Virtual Compliance for DDR4]

Virtual Compliance for DDR4是新的功能項目,DDR4Compliance Test是舊的,建議轉到新的toolkit使用。下面在Tx和Rx加電容的前提下進行VirtualCompliance for DDR4的仿真。

圖37 Virtual Compliancefor DDR4

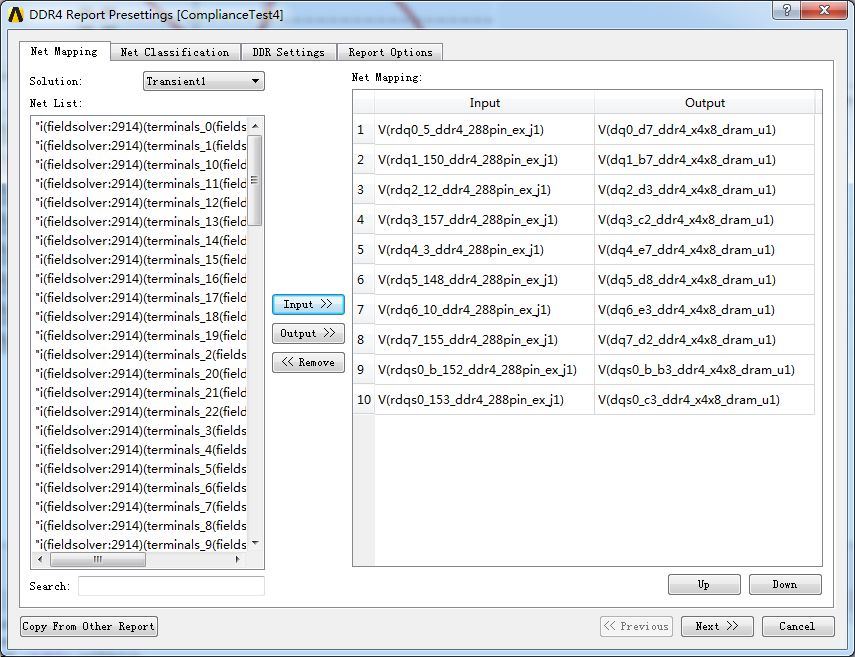

4.2、Presetting dialog forassigning net mapping

圖38 VirtualCompliance for DDR4設置向導

注意:Net的In-Out的對應連接要正確,軟件會計算self-delay(timing delay)。如果您不需要report self-delay,可以只指定output nets。

4.3、Net Classification for nettype, group and IO power

圖39 VirtualCompliance for DDR4設置向導

注意:For GDDR5, it supports to use samestrobe pair in different Byte-lane group.

IO power、Net Types與NetGroups都要設定,step5.5中的【Generate】才能跑下去。當在設置DQS差分信號時,一定要按照circuit原理圖中的N/P分配原則,否則后續將無法進行。

4.4、DDR settings

這里速率選擇3200MHz,紅線中參數為JESD79-4 內存標準中的規定。

圖40 VirtualCompliance for DDR4設置向導

注意:本文3.1顯示DQ與DQS差0.5UI,所以上圖【TimingOPtion】/【Data Timing】必須選擇【Write】mode,這樣4.7內【Eyediagram Timing】才可以正確的顯示pass/fail

4.5、Report Options

圖41 VirtualCompliance for DDR4設置向導

4.6、Self-Delay

圖42 Self-Delayresult

1. Press [Run] to get the reportedparameters

2. Double-click the reported parameters[Min Delay] of DQ0 to open [Waveform Viewer]

圖43Waveform Viewer

3. Measuring function

圖44 Measuringfunction

4.7、Switch to different tabs and press [Run][Run All tables] to getother reported parameters.

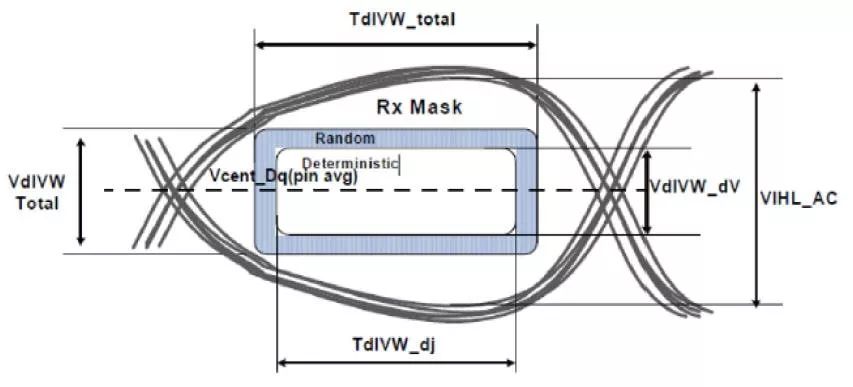

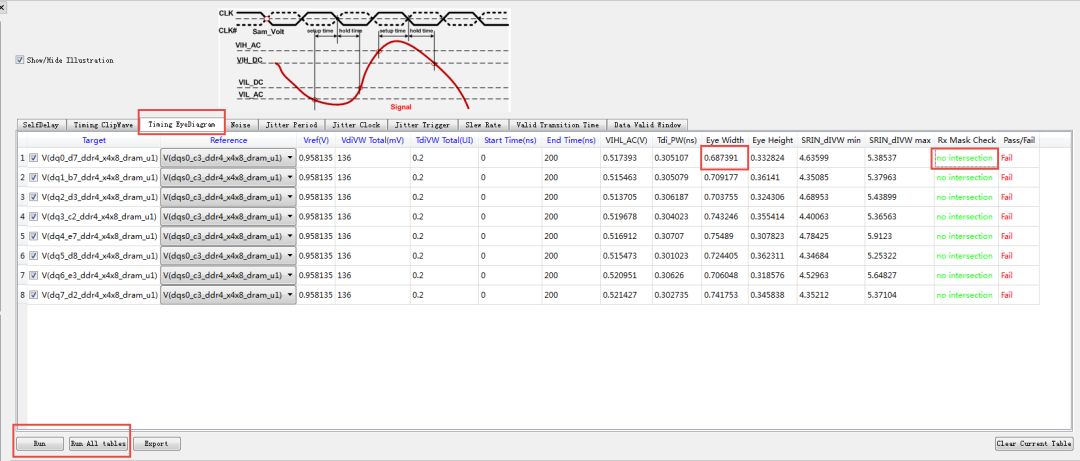

在【Timing EyeDiagram】頁面下,使用者通過輸入【VdiVW Total】與【TdiVW Total】來決定Eye Mask的高與寬,軟件會幫你算出眼圖的參數與是否有碰到Eye Mask(Rx Mask Check)。

目前只支持方形的Eye mask forchecking passfail, it is defined in JEDEC DDR4.

圖45 TimingEyeDiagram

For DDR4 compliance,這里算出的眼高(Eye High)與眼寬(Eye Width),是在BER=1e-16下得到的值

圖46 眼高和眼寬參數

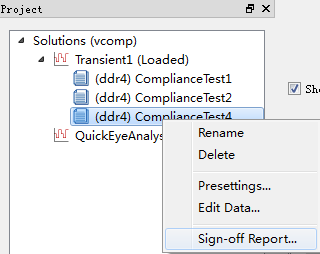

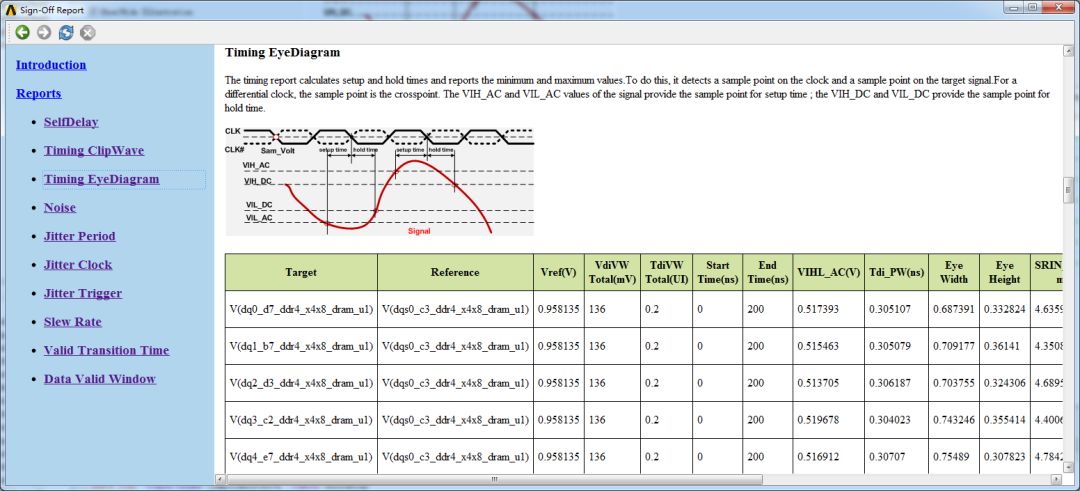

4.8、Sing-off report

ANSYS可以自動生成仿真報告,通過Sign-offReport選項可以獲得。

圖47 Sing-offreport

5、問題與討論Q&A

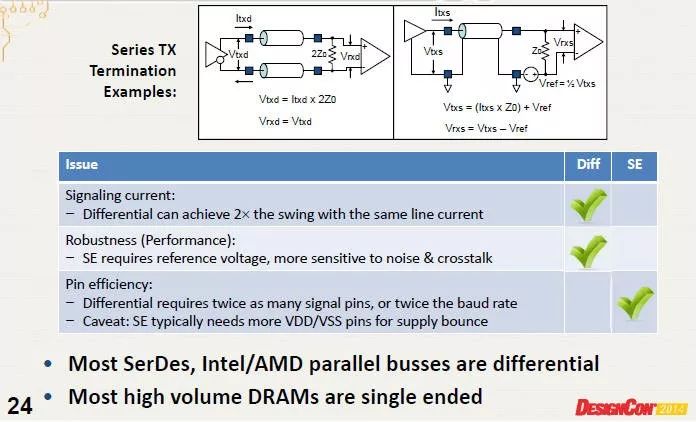

5.1、單端或差分高速信號設計,其優劣分別為何?

Ans:[9]p.24中對其中的差異進行了解釋,分別對信號的抖動,串擾噪聲等進行對比。

圖48single and differential difference

5.2、為何市面上目前看不到采用點對點傳輸架構的DDR4

Ans:我想所需的PCB繞線空間太多,可支持的總DIMM插槽較少,應該是目前較少人在DDR4使用點對點傳輸架構的主因吧!比方一顆有6個DDR4 channel的CPU,如果使用點對點架構的DDR接法,最多就是接6排DDR4插槽,但如果采用2spc架構,則最多可接12排DDR4插槽。

5.3、QuickEYE與VerifyEYE真的比Transient EYE快么?

Ans:這個答案很直覺的一位是“yes”,但實際上與模擬條件有關。

如果只跑一個net(e.g.DQ0),且跑 bit time,那肯定QuickEYE與VerifyEYE比TransientEYE快許多

bit time,那肯定QuickEYE與VerifyEYE比TransientEYE快許多

如果跑八個net(e.g.DQ0~7),且只跑PRBS13bit time,那TransientEYE比Quick EYE與Verify EYE快。關鍵在于Quick EYE與Verify EYE是by net trigger,模擬的net數越多,模擬時間乘倍數增加。

5.4、DDR4 Virtual compliance test是如何以transientanalysis結果得到BER=1e-16下的眼高與眼寬?

Ans:是透過transient analysis數據統計推估出來,并不是真的跑Verify EYE。所以transient analysis模擬時間長度會影響step 4.7的眼高與眼寬。

5.4.1、測試Transient EYE跑

圖49 三個不同數據量下的眼圖結果

為何alwaysMinEyeHeight>EyeHeight,MinEyeWidth>EyeWidth?

這是使用者最長問的問題,答案在help文檔里,EyeHeight與EyeWidth是以分布中心點考慮三倍標準差(3),是含有統計概念在里面的。

EyeHeight = [(EyeLevelOne - 3s1) - (EyeLevelZero + 3s0 )] where s1and s0 are the standard deviations of the vertical histograms used to determineEyeLevelZero and EyeLevelOne.

EyeWidth = [( t2 - 3s) - (t1 + 3s)] where s is the standarddeviation of the horizontal histograms used to determine eye-crossing points.

MinEyeWidth is the minimum horizontal opening at the eye-crossingamplitude, typically at the center of the eye. Unlike statistical eye width, ifdifferent traces exist for different unit intervals, then MinEyeWidthrepresents the minimum width of all the traces.

MinEyeHeight is the minimum vertical opening at the eye-measurementpoint, typically at the center of the eye. Unlike statistical eye height, ifdifferent traces exist for different unit intervals, then MinEyeHeightrepresents the minimum height of all the traces.

圖50 mineye width的描述

5.4.2、當暫態分析的時間太短,可能會得到BER=1e-16下交叉的眼圖參數(眼寬較小、眼高較低)。

這背后的物理意義是:暫態分析時間長度較少時(模擬的Bit pattern數目較少時),眼圖偏離中間分布較遠的少數幾次bit pattern在統計上的占比會升高,導致推估至BER=1e-16下的眼高與眼寬較差。

下圖分別演示不同的暫態分析時間40ns/160ns/640ns下,從DDR4 Virtual compliancetest得到BER=1e-16下的Eye Width。

暫態分析時間40ns,BER=1e16下的Rx端眼寬UI*0.703443=312.5ps*0.703443=219.8ps

圖5140ns下的Rx端眼寬

暫態分析時間160ns,BER=1e-16下的Rx端眼寬UI*0.724729=312.5ps*0.724729=226.48ps

圖52160ns下的Rx端眼寬

暫態分析時間640ns,BER=1e-16下的Rx端眼寬UI*0.756475=312.5ps*0.756475=236.40ps

圖53640ns下的Rx端眼寬

從以上測試數據可以看出,這種透過暫態分析結果,經統計推算出在BER=1e-16下EYE parameter的技術是非常有效的,然而其參數值會略受暫態分析時間長度的影響。跑bit(312.5ps*=640ns)時間長度,比跑bit(312.5ps*=160ns)時間長度的結果好。

-

SDRAM

+關注

關注

7文章

441瀏覽量

56023 -

DDR4

+關注

關注

12文章

328瀏覽量

41521 -

ANSYS

+關注

關注

10文章

240瀏覽量

36995

原文標題:20181011---采用ANSYS進行DDR4仿真

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

DDR4與DDR3的不同之處 DDR4設計與仿真案例

佛山回收DDR4 高價回收DDR4

佛山回收DDR4 高價回收DDR4

DDR4,什么是DDR4

ddr4和ddr3內存的區別,可以通用嗎

DDR4設計規則及DDR4的PCB布線指南

DDR4原理及硬件設計

評論