目前勵磁電源信號發生部分通常采用直接頻率合成技術,主要功能電路由壓控振蕩器(VCO)、倍頻器、分頻器、混頻器和濾波器等構成,整個系統采用開環控制,即輸入設定值→頻率合成→功率放大→輸出勵磁電流。這種結構給勵磁電源帶來以下不足:(1)由于采用外部壓控振蕩器,勵磁信號的頻率范圍受到限制,一般約為50 kHz。(2)系統使用開環控制,系統精度依賴于各組件的精度和穩定性,使得勵磁電流的幅度精度和穩定性較差,儀器抗干擾性不強。(3)采用直接頻率合成技術,系統中有大量模擬電路,導致系統體積大、重量大、耗電高、可靠性差。

隨著信息技術的發展,磁性材料廣泛運用于通信、電力、信息、交通等領域中。磁滯回線是磁性材料中重要的磁性參數之一,是鐵磁材料的本質特征。通常運用于與磁性材料有關的計算和研究中,對工業生產和科學研究具有重要的指導意義。

文中提出一種基于FPGA的DDS信號發生器。信號發生電路采用直接數字頻率合成技術,即DDS(Direct Digital Frequency Synth-esis)。它是以全數字技術,從相位概念出發,直接合成所需波形的一種新的頻率合成技術。是將先進的數字處理技術和方法引入信號合成領域,把一系列數字量形式的信號通過數/模轉換器轉換成模擬信號,在時域中進行頻率合成。直接數字頻率合成器的主要優點是:輸出信號頻率相對帶寬較寬;頻率分辨力好、轉換時間快;頻率變化時相位保持連續;集成度高,體積小,控制方便等。整個信號源系統采用數字閉環控制,通過對勵磁電流瞬時值經PID閉環控制,使得勵磁電流可瞬時跟蹤給定幅值,加快系統動態響應,提高非線性負載適應力,其較傳統的信號源能更好地滿足磁性測試設備的需求。

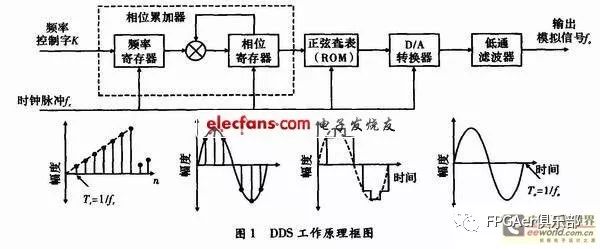

1 DDS的工作原理

DDS的工作原理如圖1所示。主要有以下基本部件:相位累加器;相位-幅度變換器,即正弦查表ROM;D/A轉換器和適當的濾波器等濾波器。相位累加器是DDS系統的核心是相位累加器,它由一個加法器和一個相位寄存器組成,相位累加器在參考時鐘的作用下,按頻率控制字為步長不斷累積,累加結果產生遞增的傳遞給正弦查表ROM。正弦查詢表中存儲了一個周期正弦波在各相位點對應數字幅度信息。由于相位累加器的輸出連接在波形存儲器(ROM)的地址線上,因此其輸出的改變就相當于進行查表。這樣就可把存儲在波形存儲器內的波形抽樣值經查找表查出,然后送至D/A轉換器,經D/A轉換器產生一系列以時鐘脈沖為抽樣速率的電壓階躍。濾波器則進一步平滑D/A轉換器輸出的近似正弦波的鋸齒階梯波,同時衰減不必要的雜散信號,使輸出為要求的光滑波形。

由于相位累加器字長的限制,相位累加器累加到一定值后,其輸出將會溢出,這樣波形存儲器的地址就會循環一次,即意味著輸出波形循環一周。故當頻率字取不同值,就可以改變相位累加器的溢出時間,從而在時鐘頻率不變的條件下改變輸出頻率。

設頻率控制字為K,系統參考時鐘為fc,相位累加器位數為N,輸出頻率為fo,則可以得到輸入與輸出的關系為

當K=1時,可以得到DDS的頻率分辨率

2 勵磁恒流源的硬件設計

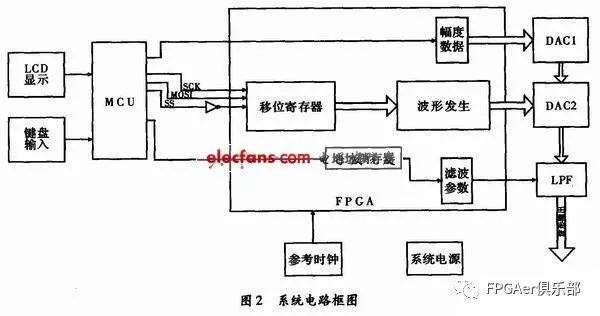

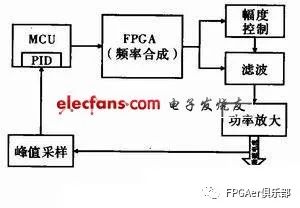

勵磁信號發生器電路系統主要由基于FPGA的DDS電路、MCU控制電路、DAC電路、低通濾波器(LPF)、人機接口、系統時鐘和系統電源構成。系統框圖,如圖2所示。

2.1 基于FPGA的DDS電路

2.1.1 相位累加器

對于利用FPGA設計DDS信號源,相位累加器是決定DDS電路性能的一個關鍵部分。相位累加器是由N位累加器和N位寄存器級聯構成,每來一個時鐘脈沖,相位寄存器采樣上個時鐘周期內相位累加器的值與頻率控制字K之和,并作為相位累加器在這一時鐘周期的輸出。由式(2)可知,相位累加器的位數N越大,得到的頻率分辨率越小,但在較高的工作頻率下,會產生較大的延時不能滿足速度的要求。在時序電路中,通常采用流水線技術來提高速度,代價是增加寄存器的數量,多占了FPGA的資料。綜合考慮,采用32位累加器,四級流水線結構。

2.1.2 相位-幅度變換器

相位-幅度變換器是由ROM構成,它把相位累加器的輸出的數字相位信息變換成正弦波值。在FPGA中,ROM一般是由EAB來實現,并且ROM表的尺寸與地址位數或數據位數成指數增加的關系,因此相位-幅度轉換器的設計是影響DDS性能的另一個關鍵,在滿足信號設計指標要求的前提下,主要在于減少資源開銷。考慮到本設計只需要輸出正弦信號,正弦波信號關于點(π,0)奇對稱,只需存儲1/2周期的波形數據,又根據在左半周期內,波形關于直線x=π/2成偶對稱,因此只需要存儲1/4周期的正弦函數值,就可以通過適當的變換得到整個正弦碼表,這樣可以節約3/4的資源。

關鍵字:DDS 勵磁恒流源

2. 2 低通濾波模塊

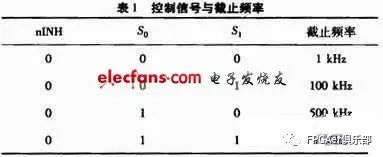

DDS有一個明顯的缺點,即輸出頻率越接近Nyquist帶寬的高端,采樣點數越少,其輸出的雜散干擾就越大。輸出波形具有大量的諧波分量和系統時鐘干擾。為得到所需頻段內的信號,需要在DDS輸出端加一濾波器來實現,而低通濾波器能較好地濾除雜波,平滑信號,所以低通濾波器的設計尤為重要,濾波特性的優劣對輸出信號的性能起重要的影響。

為取得較好的濾波效果,濾波器采用了由四選一模擬開關和精密運算放大器分段濾波的方式:采用巴特沃斯有源低通濾波器,該濾波器通帶內幅度很平坦,濾波電路為二階巴特沃斯低通濾波電路,濾波器頻段參數的選擇由FPGA輸出的控制信號nINH,S0,S1控制模擬開關的選通實現。

2.3 幅度控制

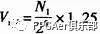

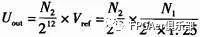

本設計幅度控制電路采用調節DAC參考電壓的數字化控制方法,采用兩個D/A級聯的方式,數模轉換器DAC2采用外部可變基準源,通過改變基準源的值來改變輸出的滿幅度電流值,該可變基準源通過DAC1產生。DAC1的基準電壓采用輸出電壓為1.25 V精密電壓基準芯片提供,設DAC1的幅度輸出字為N1,則DAC1的參考電壓為

設DAC2的數字輸入字為N2,則經電流/電壓轉換后的輸出電壓為

2.4 人機交互

為方便快捷地控制DDS的頻率字輸入和幅度控制,本設計采用單片機來實現對DDS信號發生器的控制。DDS的頻率字和幅度數據字位較多,而單片機輸出端口位數有限,所以單片機與FPGA之間的通信采用SPI(Serial Peripheral Interface,串行外設接口)方式,單片機將控制命令字傳送給FPGA。同時,為了輸入控制方便,添加了鍵盤和顯示系統。

3 數字閉環控制系統的實現

設計的勵磁恒流源主要為磁性測量儀器提供激勵電源,因而對其精度和穩定性要求高,采用電流控制型的控制策略進行閉環控制,結構框圖如圖3所示。勵磁電流幅度調整時,首先對勵磁電流進行多周期采樣,然后計算其有效值,并與輸入設定值相比較,若誤差ε在允許范圍之外,則根據誤差的實際情況,通過單片機內增量式PID算法得出了一個新的控制量,傳送給FPGA控制幅度調節經低通濾波器濾去高頻成分,再經功率放大,得到高精度的勵磁電流。

4 系統仿真與驗證分析

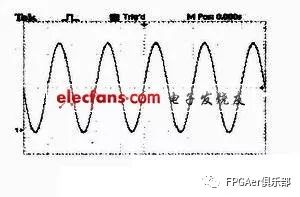

在Altera公司的QuartusⅡ環境下編譯完成,采用自上而下的設計方法,即先從系統總體要求出發將設計內容細化,最后完成系統硬件的整體設計。完成DDS設計后,通過編寫Testbench在Modelsim進行仿真。在QuartusⅡ中,設定輸出信號頻率為1 MHz,經過50 μs后改變為500 kHz進行仿真,其仿真結果如圖4所示。在Modelsim中生成的仿真數據經驗證完全正確,滿足設計需求。

在對勵磁信號源做硬件系統測試時,首先完成系統硬件連接,并加載程序,設定輸出信號頻率為1 MHz,示波器測得實際輸出波形如圖5所示。在Modelsim環境下仿真和在硬件平臺上測試,結果表明勵磁信號源可獲得較好的設置波形,可以應用于磁性材料的測試中。

5 結束語

運用Verilog硬件編程語言結合DDS技術,利用FPGA器件強大的硬件功能,提高了系統集成度,實現了輸出信號相對帶寬寬、穩定性好;其相位累加器在一定系統時鐘和累加器位寬條件,輸出信號分辨率越小,頻率控制字的傳輸時間以及器件響應時間都很短,使輸出信號頻率切換時間較短,可以達到ns級,且頻率變化時,相位保持連續,系統采用閉環控制,勵磁電流輸出精度高,調節速度快。對磁性材料測量儀所要求的勵磁信號源而言,本設計不但滿足所有技術指標,而且集成度高、體積小、顯著地降低了成本。

-

濾波器

+關注

關注

161文章

7846瀏覽量

178414 -

分頻器

+關注

關注

43文章

447瀏覽量

49997 -

VCO

+關注

關注

13文章

190瀏覽量

69232

原文標題:基于FPGA的DDS勵磁恒流源設計

文章出處:【微信號:FPGAer_Club,微信公眾號:FPGAer俱樂部】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

工業生產節能控制器的設計

缺陷檢測在工業生產中的應用

先進控制技術在工業生產中的應用Advanced Proces

現場總線技術及其在工業生產中的應用

區塊鏈技術對促進我國數字經濟發展具有重要意義

5G應用的重要意義概述

海南智能電網全方位推動海南能源革命具有電力創新示范的重要意義

企業申請USB VID具有哪些重要意義

流量計在工業生產中的應用有哪些

無線按鈕拉繩盒主要適用于哪些工業生產環境

磁滯回線對工業生產具有哪些重要意義?

磁滯回線對工業生產具有哪些重要意義?

評論