概述

無論一輛汽車它是21世紀(jì)20年代初的輔助駕駛汽車,即帶有用于信息娛樂系統(tǒng)、傳動系統(tǒng)和自主駕駛員輔助系統(tǒng)(ADAS)的智能子網(wǎng)的汽車,還是未來3級 (Level 3)及以上的自動駕駛汽車(在車流中駕駛時只需最少的人力輔助),網(wǎng)絡(luò)化交通系統(tǒng)對硬件加速的需求正在迅猛增長。幾年前,由Nvidia,Mobileye和其他以CPU為中心的供應(yīng)商推出的最受青睞的汽車智能模型都假設(shè)了一個集中式汽車網(wǎng)絡(luò),其中由帶有增強DSP功能的多核RISC CPU來管理一套專用的子網(wǎng)絡(luò)。現(xiàn)在,關(guān)注點正在迅速轉(zhuǎn)向分布式汽車智能化,其中包含帶有相關(guān)視覺系統(tǒng)的復(fù)雜相機,具有來自物聯(lián)網(wǎng)世界的傳感器中樞架構(gòu)的傳感器子網(wǎng)絡(luò)、以及用于車載信息娛樂系統(tǒng)(IVI)和ADAS的附加子網(wǎng)絡(luò)、以及傳動系統(tǒng)/動力系統(tǒng)子網(wǎng)絡(luò),共同協(xié)作來實現(xiàn)自動駕駛汽車功能。

雖然Achronix預(yù)計未來的傳統(tǒng)車輛和自動駕駛車輛最喜歡的架構(gòu)都將是分布式架構(gòu),但是任何一種網(wǎng)絡(luò)都需要比目前已經(jīng)實現(xiàn)的架構(gòu)更多的后備協(xié)處理能力。汽車網(wǎng)絡(luò)中預(yù)期的分布式計算架構(gòu)將是異構(gòu)的,需要從網(wǎng)絡(luò)控制到利用深度學(xué)習(xí)節(jié)點的并行對象識別的混合計算資源。結(jié)果,豪華輔助駕駛汽車中目前CPU的基數(shù)多達(dá)100個,而在自動駕駛汽車中可能會增加到幾百個CPU。傳感器中樞將需要后備圖像處理來實現(xiàn)扭曲和拼接效果;以太網(wǎng)需要IP進(jìn)行數(shù)據(jù)包過濾/監(jiān)控,以及與傳統(tǒng)CAN和FlexRay網(wǎng)絡(luò)的特殊橋接。在第一代汽車架構(gòu)中使用整數(shù)個CPU和GPU,將遷移到需要可編程加速的高度專業(yè)化計算節(jié)點。

為了優(yōu)化芯片面積和功率效率,在未來的汽車平臺上,相比固定功能的SoC或傳統(tǒng)的FPGA,將Speedcore?嵌入式FPGA(eFPGA)硅知識產(chǎn)權(quán)(IP)集成到SoC中以提供客戶可配置功能,是實現(xiàn)快速切換協(xié)處理的一個最佳選擇 。要了解更多關(guān)于處理過程的演變,請參見Achronix白皮書(WP008):SoC中的EFPGA加速 - 了解Speedcore IP設(shè)計流程。

Speedcore eFPGA IP在異構(gòu)汽車數(shù)據(jù)處理中的獨特作用

Speedcore eFPGA IP可以集成到ASIC或SoC中,以提供定制的可編程邏輯陣列。客戶指定他們的邏輯、內(nèi)存和DSP資源需求,然后Achronix配置Speedcore IP以滿足他們的特定需求。Speedcore查找表(LUT)、RAM模塊和DSP64模塊可以像積木一樣進(jìn)行組合,為任何給定應(yīng)用創(chuàng)建最佳的可編程邏輯陣列。Speedcore eFPGA IP在汽車網(wǎng)絡(luò)集成方面提供獨特的優(yōu)勢,無論是在現(xiàn)有設(shè)計中取代一個FPGA還是增強一個ASIC。

l更高的性能 – 一個eFPGA通過寬闊的并行接口直接連接(無I / O緩沖器)到ASIC,提供顯著更高的吞吐量,延遲僅為個位數(shù)的時鐘周期。 在需要對迅速變化的交通狀況進(jìn)行實時響應(yīng)時,延遲非常重要。

l更低的功耗:

l可編程I / O電路的功耗占獨立FPGA總功耗的一半。一個 eFPGA直接連接到SoC,完全消除了大型可編程I / O緩沖器,從而降低了功耗。

l一個eFPGA的面積可以根據(jù)最終應(yīng)用的要求精確定制,并且可以調(diào)整工藝技術(shù)以實現(xiàn)性能和功耗的平衡。

l更低的系統(tǒng)成本:

l一個eFPGA的片芯占用面積比等效的獨立FPGA小得多,這是因為可編程I / O緩沖器,未使用的DSP和存儲器模塊以及過度配置的LUT和寄存器都全部被移除。

l借助Speedcore定制模塊,可將定制功能作為附加模塊添加到eFPGA邏輯陣列中,并與傳統(tǒng)的LUT、RAM和DSP構(gòu)建模塊一起添加。這種高效的實施方式極大地降低了片芯尺寸面積,最大限度地降低了功耗,其總體結(jié)果就是,大大降低了系統(tǒng)成本。有關(guān)更多詳細(xì)信息,請參閱Achronix白皮書(WP009):使用Speedcore定制模塊來增強eFPGA功能。

l更高的系統(tǒng)可靠性和良率 - 將FPGA功能集成到ASIC中,可以提高系統(tǒng)級信號完整性,并消除了在PCB上安裝一個獨立FPGA相關(guān)聯(lián)的可靠性和良率損失。

以ADAS為中心的處理模型

由于多個視覺處理系統(tǒng)的融合被認(rèn)為是駕駛輔助和自動駕駛車輛的核心,所以先進(jìn)駕駛員輔助系統(tǒng)(ADAS)在未來的汽車架構(gòu)中保持了核心地位,即使被認(rèn)為是管理者中的管理者的多核視覺處理器,也已經(jīng)部分被取代了。涉及DSP和整數(shù)密集型任務(wù)兩者的圖像實時處理,最初被認(rèn)為是從靜態(tài)相機或視頻圖像中提取信息以確定對象類型、位置和速度的問題。隨著設(shè)計人員為自動駕駛車輛做準(zhǔn)備,ADAS處理器的角色已經(jīng)擴展到包括視覺、紅外、超聲波、激光雷達(dá)(LIDAR)和雷達(dá)圖像的融合。在傳統(tǒng)的SoC和協(xié)處理器套件中,圖像預(yù)處理與CPU分開執(zhí)行,并且必須通過一個或多個高速總線與CPU連接。即使ADAS架構(gòu)的總線延遲得到改善,當(dāng)協(xié)處理器在單獨的芯片中實現(xiàn)時,也會付出延遲的代價。因此,將eFPGA IP與統(tǒng)一ADAS架構(gòu)中的CPU相結(jié)合,以確保在快速變化的交通狀況中有視覺、紅外或雷達(dá)警報的快速響應(yīng),這是可以驗證的最有效的方式。

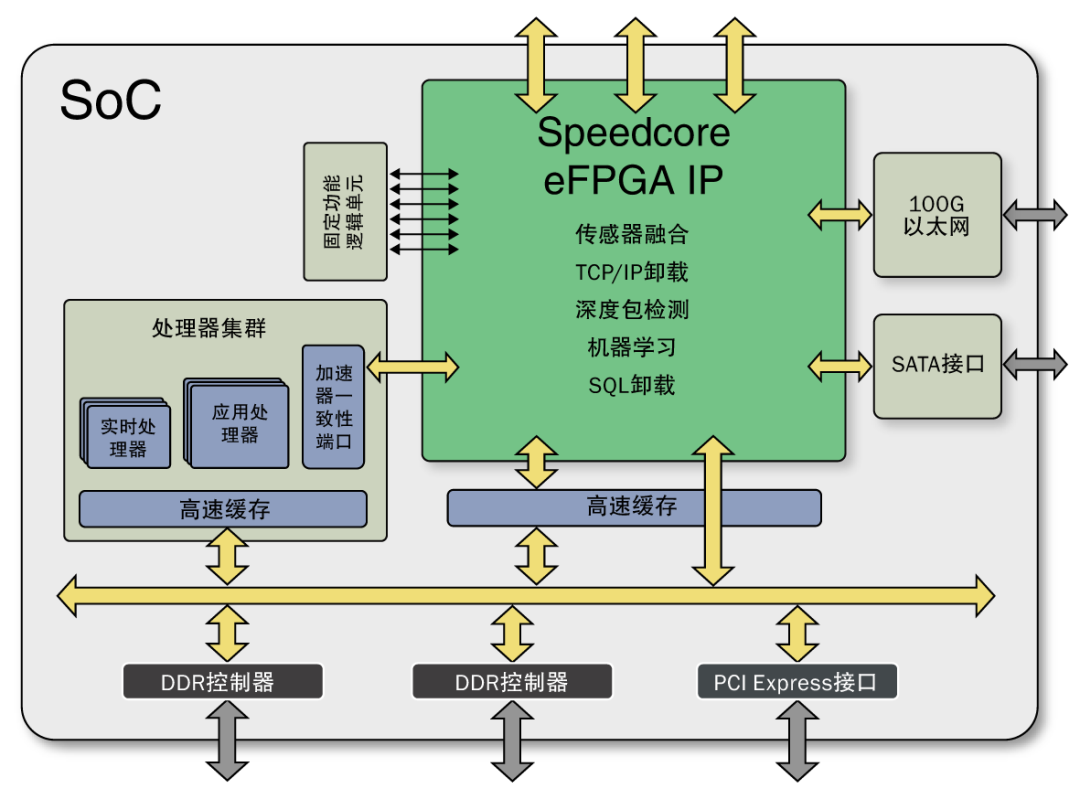

將多個傳感器源與一個ADAS內(nèi)核集成在一起,提供了Speedcore IP與一個CPU并行嵌入的一種理想應(yīng)用場景。 Speedcore IP支持客戶將一個定制的可編程邏輯陣列嵌入到具有專用計算資源的標(biāo)準(zhǔn)化ASIC平臺中(請參見下圖,并請參閱第4頁)。在實踐中,這種集成化可以將從圖像源匯總的數(shù)據(jù)寫入CPU的緩存,而不是寫入獨立的SDRAM。 減少CPU的中斷意味著對移動中汽車視野里的物體有更多的實時響應(yīng)。

視覺處理器(通常來自相機輸入的2D圖像,盡管已包括越來越多的3D圖像)可以依靠多年來在邊緣提取、格式轉(zhuǎn)換、色彩平衡和分辨率變化方面積累的圖形處理器研究。包括Ceva和Synopsys在內(nèi)的一些處理器IP供應(yīng)商,也在對象分類和識別中提升了卷積神經(jīng)網(wǎng)絡(luò)的價值。以Nvidia為代表的,在這兩個領(lǐng)域都有經(jīng)驗的CPU供應(yīng)商,已經(jīng)試圖在傳統(tǒng)的CPU / GPU任務(wù)與特定的神經(jīng)網(wǎng)絡(luò)模式識別引擎之間取得平衡。對于汽車中的神經(jīng)網(wǎng)絡(luò)子架構(gòu),正從需要高精度浮點DSP的早期成熟架構(gòu)遷移到能夠使用低精度DSP內(nèi)核的自我培訓(xùn)推理引擎,Speedcore DSP64模塊為新的深度學(xué)習(xí)架構(gòu)提供了大量的開銷。 對ADAS和視覺處理演變的一個共同認(rèn)識是,實時汽車的態(tài)勢感知永遠(yuǎn)不會有一個最佳的集中式ADAS處理器或SoC。總是會有意想不到的協(xié)同處理和加速任務(wù)被添加到ADAS中心內(nèi)核中。

任何ADAS處理器固有的兩項附加功能是傳感器融合/中樞集成和網(wǎng)絡(luò)轉(zhuǎn)換。前者涉及將來自各種傳感器的信息進(jìn)行組合和關(guān)聯(lián):包括CMOS圖像、紅外、激光雷達(dá)和新興的小型化雷達(dá)等傳感器。網(wǎng)絡(luò)轉(zhuǎn)換是指以太網(wǎng)的主干網(wǎng)絡(luò)與CSI-2、FlexRay、CAN甚至更早的網(wǎng)絡(luò)協(xié)議的接口。雖然未來的一個ADAS SoC確實可以集成一個傳感器中樞或一個以太網(wǎng)MAC,但總是會有一些新興的功能,由CPU外部的外圍邏輯極好地提供。由于傳感器被聚合并且網(wǎng)絡(luò)在輸入到CPU之前在芯片內(nèi)互連,所以通過減少暴露的接口來保持安全性是一個解決方案,同時通過片上集成來提高可靠性,對于許多這樣的任務(wù)而言將被證明是最佳的方案。

圖1:Speedcore陣列(左上)鏈接到CPU子系統(tǒng)及內(nèi)存集群

可編程能力在功能安全性中的作用

從駕駛輔助車輛到完全自動駕駛車輛的過渡已經(jīng)提高了安全性在新車中的地位。網(wǎng)絡(luò)對車輛的控制越多,越多的司機期望多級安全性以防止諸如引起了公眾高度關(guān)注的2016年特斯拉死亡事故這類事件。這種對于容錯安全性的驅(qū)動力促使業(yè)界頒布了針對自動駕駛汽車領(lǐng)域的ISO 26262標(biāo)準(zhǔn),它是作為電氣和電子系統(tǒng)IEC 61508通用功能安全性標(biāo)準(zhǔn)的衍生標(biāo)準(zhǔn)。

在EDA和SoC社群內(nèi)的早期工作已經(jīng)實現(xiàn)了ISO 26262方法體系的標(biāo)準(zhǔn)化,以確保IP中功能安全性。故障模式、效果和診斷分析(FMEDA)技術(shù)闡述了針對IP單元的功能和故障模式的標(biāo)準(zhǔn)規(guī)范,一個故障模式對產(chǎn)品功能的影響,自動診斷檢測故障的能力,設(shè)計強度以及運行情況分集,包括環(huán)境壓力。一個強健的系統(tǒng)應(yīng)該最大限度地提高IP單元的診斷覆蓋范圍,并通過適當(dāng)處理安全的、檢測到的和未檢測到的故障來提供高度的功能安全性。

嵌入式FPGA由于其極度可編程化的特性,還可以增強車輛在作為系統(tǒng)時的安全性。 除了主控車輛的“航行”功能之外,SoC中的eFPGA還可以承載大量的硬件診斷功能,其運行速度比基于軟件的診斷快幾個數(shù)量級,大大增加了任何車載內(nèi)置的自測故障覆蓋率(BIST)。 此外,它們以可編程方式幫助汽車制造商更新已部署的系統(tǒng),從而有助于ISO 26262安全性生命周期。 以特斯拉車禍為例,如果事故的根本原因是硬件中托管的對象檢測算法中有錯誤(由于性能原因),只要開發(fā)了修復(fù)程序,就可以將其推送到整個車隊。可以繞過漫長而昂貴的硬件開發(fā)和重新部署過程。

分布式控制意味著分布式智能

由于攝像頭的安裝位置以及對局部傳感器中樞的需求,汽車設(shè)計人員總是規(guī)劃在車體內(nèi)采用了大量的分布式智能。盡管如此,諸如Nvidia Tegra等多核多線程處理器的早期支持者都認(rèn)為,要把大部分智能都集中在儀表板中或者附近,盡管是為了高度并行的CPU工作于對象識別。現(xiàn)在,先進(jìn)的ADAS在輔助駕駛汽車和三級自主駕駛汽車的完全自主性之間的模糊界限已經(jīng)引起人們的注意,回到分布式智能,其中CPU、GPU和神經(jīng)網(wǎng)絡(luò)處理器在車體內(nèi)提供了多個管理和控制點。這種轉(zhuǎn)變意味著可編程架構(gòu)的更多機會存在于全面覆蓋的SoC設(shè)計之外。

現(xiàn)在,ADAS處理器市場每年增長超過25%。這種增長是由于從自動緊急制動、換道輔助和自適應(yīng)巡航控制等功能開始,ADAS功能已從豪華車輛轉(zhuǎn)移到中型和入門級車輛 - 這些功能將在下個十年中期之前被普遍使用。與此同時,三級自動駕駛汽車將于2018年在諸如寶馬17等豪華平臺上推出,而全自動五級汽車可能在2022年之前可供商業(yè)銷售。隨著自主駕駛平臺從三級發(fā)展到四級和五級,傳感器中樞、攝像頭和激光雷達(dá)/雷達(dá)設(shè)備將遍布整個車輛,并且每個都需要本地控制。

這種控制模式在業(yè)界產(chǎn)業(yè)整合中已經(jīng)清晰可見,如高通公司對恩智浦發(fā)起的收購、以及英特爾對Mobileye的收購,處理器領(lǐng)域?qū)⒂赡切┲铝τ趯㈤_發(fā)生態(tài)系統(tǒng)引導(dǎo)至特定專業(yè)領(lǐng)域的大型供應(yīng)商占據(jù)主導(dǎo)地位 — 英特爾采用服務(wù)器加機器學(xué)習(xí)模式,英偉達(dá)采用GPU /機器學(xué)習(xí)模式,高通采用以蜂窩移動通信為中心的模式,增加了恩智浦Cognivue和i.MX處理器。例如 Ceva、Cadence / Tensilica、Synopsys / ARC和VeriSilicon等IP開發(fā)人員將嘗試通過其在特殊處理器內(nèi)核方面的專業(yè)技術(shù)來顛覆封閉模式。與此同時,如Broadcom、Valens和Marvell等網(wǎng)絡(luò)專家將尋求圍繞以太網(wǎng)主干網(wǎng)絡(luò)來定義汽車架構(gòu)。

這樣的市場格局與企業(yè)網(wǎng)絡(luò)演變成數(shù)據(jù)中心的時代有些相似。以處理器為中心的半導(dǎo)體供應(yīng)商試圖定義一個完整的系統(tǒng)架構(gòu),但設(shè)計領(lǐng)域則展示了多樣化的狂野西部(Wild-West)風(fēng)格,其中用不同的邏輯套件來為一家組件供應(yīng)商(以及OEM或汽車制造商)提供樣品從而創(chuàng)建特有的優(yōu)勢。在這樣的環(huán)境中,配置為IP的可編程邏輯(如Achronix的Speedcore eFPGA)將扮演重要角色,不僅在近期輔助駕駛和自動駕駛汽車開發(fā)方面是這樣,而且在這兩種類型的車輛多年來的分布式處理器開發(fā)發(fā)面亦是如此。

Speedcore eFPGA IP提供了其他優(yōu)勢,例如通過寫入CPU緩存而不是片外內(nèi)存來最大限度地減少CPU中斷。 CAN設(shè)計中所需的BIST電路通常占總ASIC電路的10%至15%,由于支持BIST的電路可以在eFPGA內(nèi)可編程,所以在許多情況下這些電路可以被省去。 另外,eFPGA可以提供片上探測功能來進(jìn)行診斷。對于現(xiàn)有的基于ASIC的、無需更換FPGA的系統(tǒng)設(shè)計,Speedcore IP所具有的靈活性將支持對新算法進(jìn)行編程,從而延長了現(xiàn)場已部署的ASIC的使用壽命。在5G蜂窩網(wǎng)絡(luò)現(xiàn)有設(shè)計中使用Speedcore IP也將使該架構(gòu)成為未來V2X通信接口的理想型選擇。

在未來的全自動和先進(jìn)輔助駕駛車輛中,存在幾十個甚至數(shù)百個分布式CPU。 用于將汽車子網(wǎng)連接在一起的外設(shè)處理功能可由ASIC、SoC或傳統(tǒng)FPGA提供服務(wù)。 但是,Speedcore eFPGA IP的引入提供了傳統(tǒng)FPGA所不具備的,在延遲、安全性、帶寬和可靠性等方面的優(yōu)勢。

-

adas

+關(guān)注

關(guān)注

310文章

2226瀏覽量

209630 -

Achronix

+關(guān)注

關(guān)注

1文章

76瀏覽量

22673 -

efpga

+關(guān)注

關(guān)注

1文章

33瀏覽量

15791

發(fā)布評論請先 登錄

相關(guān)推薦

?Achronix定制單元塊大幅提升Speedcore eFPGA性能

盤點10項汽車智能化技術(shù)

智能化汽車的極致在哪里

Speedcore eFPGA在汽車智能化中有哪些應(yīng)用?

下一代汽車專用集成電路(ASIC)的嵌入式現(xiàn)場可編程邏輯門陣列(eFPGA)

Achronix宣布用于SoC加速的Speedcore嵌入式FPGA IP產(chǎn)品開始供貨

全新Speedcore標(biāo)準(zhǔn)比FPGA更高效,大幅縮減芯片面積及功耗

Achronix宣布為其eFPGA IP解決方案推出定制單元塊

解密:Achronix 7nm eFPGA的設(shè)計方法

Achronix半導(dǎo)體全面對接Speedcore eFPGA技術(shù)

Achronix宣布其Speedcore eFPGA IP核出貨量超千萬個

在SoC中添加eFPGA可實現(xiàn)更靈活的設(shè)計

Achronix Speedcore eFPGA IP性能介紹

基于Speedcore eFPGA IP構(gòu)建Chiplet

Achronix Speedcore eFPGA的特性和功能

評論