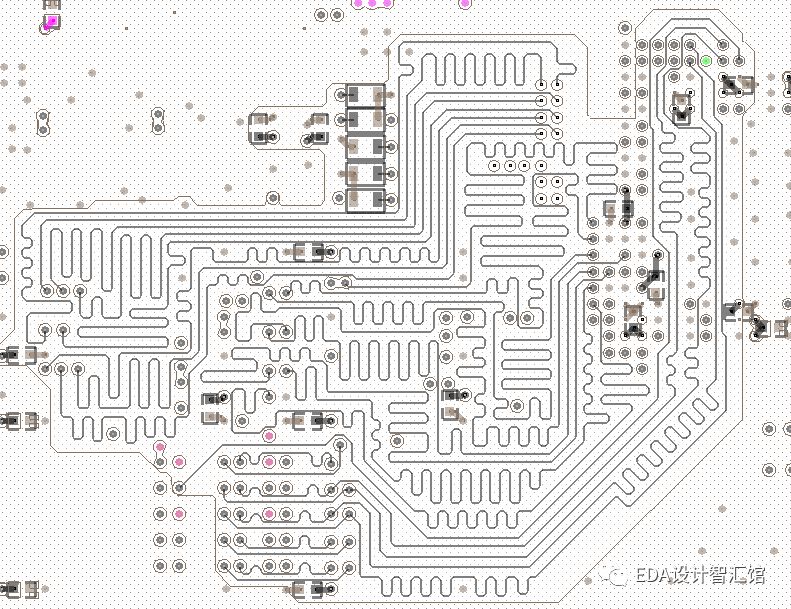

關于傳輸線的阻抗控制,很多老司機其實都已經玩的比較溜了。下面來欣賞一下。

他們的阻抗設計:

他們實測的阻抗:

高速板玩的就是阻抗,誰的阻抗玩的好,誰的高速板就玩的溜。什么傳輸線的阻抗,射頻阻抗,過孔的阻抗,阻容器件的阻抗,高速連接器的阻抗......來,接著看。

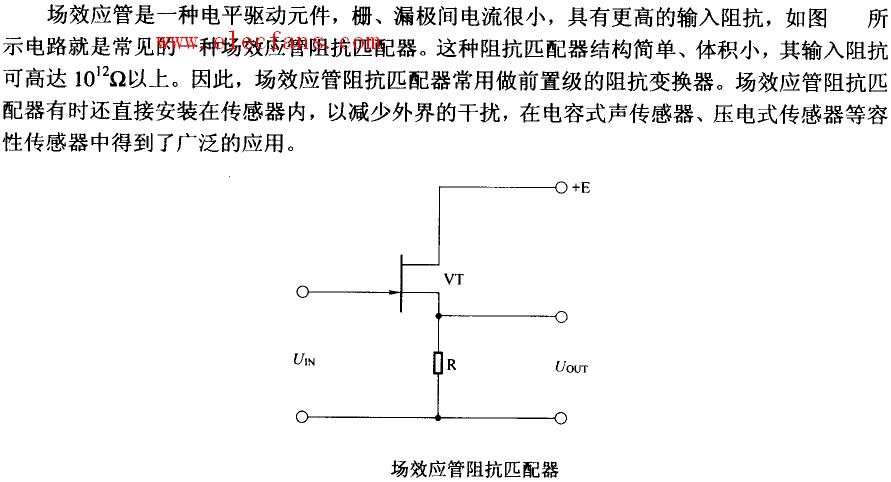

傳輸線的阻抗控制

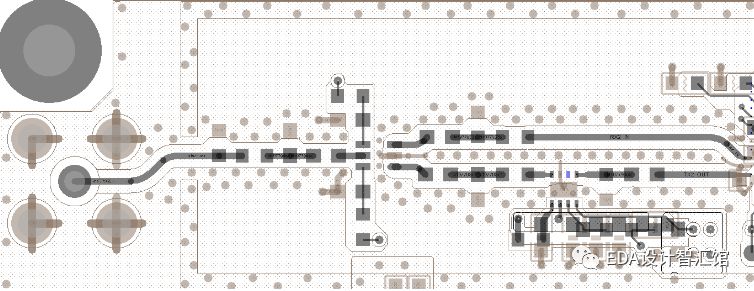

射頻信號的阻抗控制

過孔的阻抗控制

阻容器件的阻抗控制

高速連接器的阻抗控制

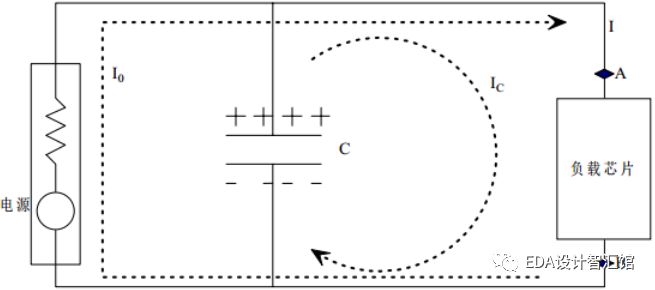

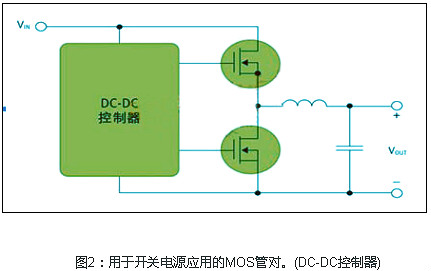

那電源的阻抗你有沒有聽說過?電源要不要控制阻抗?答案是肯定的。下圖是一個簡易的電源系統。

從AB兩點向左看過去,穩壓電源以及電容退耦系統一起,可以看成一個復合的電源系統。這個電源系統的特點是:不論AB兩點間負載瞬態電流如何變化,都能保證AB兩點間的電壓保持穩定,即AB兩點間電壓變化很小。

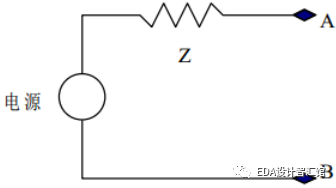

我們可以用一個等效電源模型表示上面這個復合的電源系統。

對于這個電路可寫出如下等式:

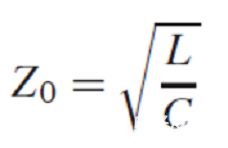

我們對這個電源系統的最終設計目標是,不論AB兩點間負載瞬態電流如何變化,都要保持AB兩點間電壓變化范圍很小,這個要求等效于電源系統的阻抗Z要足夠低。阻抗Z值該如何確定?這就涉及到電源的著名的目標阻抗。

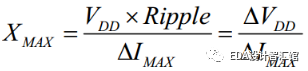

電源系統分配網絡的設計要求在需要去耦的頻帶范圍內能夠滿足目標阻抗,以便輸出穩定的電壓。在IC端放置去相電容連接在電源和地平面之間來降低PDN的阻抗。根據系統需求設計PDN的目標阻抗,其表達式為:

其中:為要進行去耦的電源電壓等級,常見的有5V、3.3V、1.8V、1.26V、1.2V等。Ripple為允許的電壓波動,典型值為5%。

?I為負載芯片的最大瞬態電流變化量。該定義可解釋為:能滿足負載最大瞬態電流供應,且電壓變化不超過最大容許波動范圍的情況下,電源系統自身阻抗的最大值。超過這一阻抗值,電源波動將超過容許范圍。

舉例:DDR4的電壓為1.2V,帶4片DDR4總的最大電流為2A。那允許的電壓波動=1.2V*0.05=0.06V,負載最大瞬態電流供應為2A,DDR4電源系統所允許的最大阻抗值應該為0.06/2A=30mohm。

對目標阻抗有兩點需要說明:1目標阻抗是電源系統的瞬態阻抗,是對快速變化的電流表現出來的一種阻抗特性。2目標阻抗和一定寬度的頻段有關。在感興趣的整個頻率范圍內,電源阻抗都不能超過這個值。阻抗是電阻、電感和電容共同作用的結果,因此必然與頻率有關。相同條件下的電源系統,頻率越大,阻抗越大。

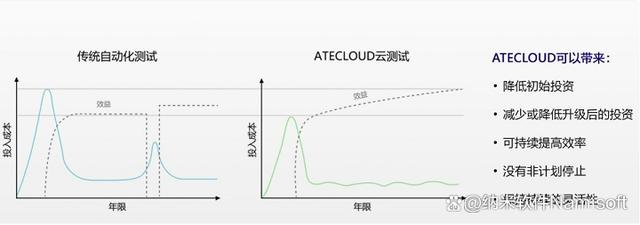

最終的電源系統的阻抗在不在目標阻抗之內,只有通過仿真確定。

上圖很明顯可以看到,在頻率大于10MHz時,電源阻抗已經超過了目標阻抗,這個時候需要對應電源系統進行優化:

1.優化電源平面

2.優化電容位置

3.優化電容的安裝方式

4.優化電容種類,型號和數目

5.優化層疊結構

-

電源

+關注

關注

184文章

17706瀏覽量

249992 -

阻抗

+關注

關注

17文章

957瀏覽量

45924

原文標題:走線的阻抗控制的那么好,你的電源阻抗管控的如何?

文章出處:【微信號:PCBTech,微信公眾號:EDA設計智匯館】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何管控你的電源阻抗

如何管控你的電源阻抗

評論