- Load:0 second

- Duration:0 second

- Size:0x0

- Volume:0%

- Fps:60fps

- Sudio decoded:0 Byte

- Video decoded:0 Byte

Khronos Group2013年11月19日宣布了OpenCL通用計算標準的2.0版本特性,其中對共享虛擬內存的支持是一大亮點(此前NVIDIA發布了CUDA 6規范也同樣支持共享虛擬內存,但目前僅限Kepler和Maxwell架構的N卡。此外,AMD的GCN架構顯卡同樣支持。AMD的Kaveri APU支持HSA異構計算和hUMA統一物理尋址,較虛擬共享更加先進。)在這個簡短的視頻中,您將學習如何在OpenCL 2.0中實現Sierpinski Carpet Kernel。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

intel

+關注

關注

19文章

3494瀏覽量

188131 -

內存

+關注

關注

8文章

3115瀏覽量

75062 -

架構

+關注

關注

1文章

528瀏覽量

25892

發布評論請先 登錄

相關推薦

熱點推薦

linux kernel通過修改鏈接腳本lds文件,如何在esp32的linker.lf文件中實現?

linux kernel通過修改鏈接腳本lds文件實現,請問如何在esp32的linker.lf文件中實現?

linux

發表于 06-26 06:19

Altera OpenCL

各位大牛晚上好,是這樣的,小弟目前在做一個Altera OpenCL的工作,具體是將OpenCL的kernel通過Altera提供的工具轉換成aocx和Quartus工程,然后下載到FPGA板子上

發表于 03-11 20:32

請問如何在Zynq Z-7020上使用opencl?

SDSoc網頁顯示2016.3 IDE可以在synq芯片上使用opencl,在這里,但我無法得到它?在哪里下載?是否有在synq芯片上使用opencl的andy demo?如果我不能得到支持opencl的SDSoc IDE,我如

發表于 05-15 06:08

hi3861如何在移植的main.c中初始化kernel和系統

指針地址調用entry函數,但asm文件指向重啟函數。需求:請簡要說明如何在移植的main.c中初始化kernel和系統

發表于 11-19 12:03

【飛凌T507開發板試用體驗】opencl試用

的用戶手冊可知,芯片中的集成Mali G31 GPU支持OpenCL2.0,所以想使用這款GPU做異構并行加速計算。在飛凌提供的用戶手冊中沒有找到任何有關OpenCL的內容,故在網上或者論文查找一些

發表于 02-24 19:06

改進型Sierpinski分形微帶天線仿真

將HFSS高頻仿真軟件對不同張角下的二階Sierpinski分形天線進行仿真,得到不同情況下的回波損耗參數和方向圖。Sierpinski分形天線具有多頻段的特性,由其自相似分形結構決定。

發表于 10-17 16:44

?58次下載

如何在matlab中實現Virtual Reality 技術

如何在matlab中實現Virtual Reality 技術,資料的代碼很全,步驟很清晰,很實用,歡迎大家下載交流。

發表于 06-03 16:57

?0次下載

OpenCL應用程序的主機代碼和內核元素

用于異構計算的OpenCL標準為實現OpenCL標準的所有計算設備定義了基本編程模型。

該視頻介紹了OpenCL應用程序的主機代碼和內核元素。

這些映射......

如何使用OpenCL輕松實現FPGA應用編程

實現這一編程思想的轉變,是因為 FPGA 借助 OpenCL 實現了編程,程序員只需要通過 C/C++ 添加適當的 pragma 就能實現 FPGA 編程。為了讓您用

發表于 07-16 17:58

?6894次閱讀

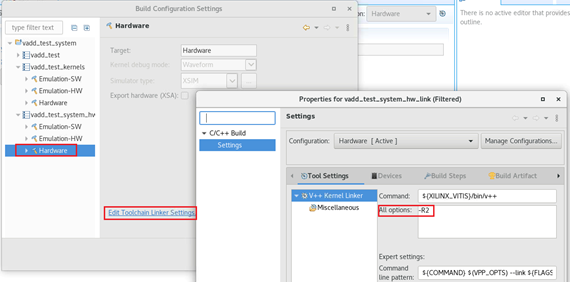

如何在Vitis中設定Kernel的頻率

在Kernel Estimate報告中,可以看到,Target Clock已經按要求設置成200Mhz. 說明 Vitis_HLS是按照200Mhz的要求來綜合Kernel的代碼的.

如何在Vitis加速設計中為Kernel創建面積約束

Alveo系列開發板上的平臺其實是一個DFX設計的靜態部分,在Vitis 統一軟件平臺中使用Alveo系列開發板設計加速Kernel, 最終這些Kernel的邏輯會在分布在DFX設計的動態區域。

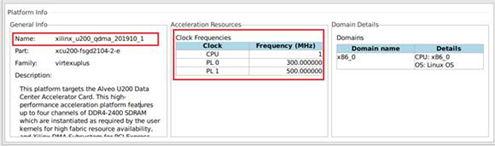

如何在Vitis中設定Kernel的頻率

在Vitis 統一軟件平臺中使用Alveo系列開發板設計加速Kernel時,系統會自動為Kernel的時鐘設置默認頻率。以 xilinx_u200_qdma_201910_1 平臺為例,在Vitis中選擇平臺時可以看到默認的時鐘頻率是300Mhz和500Mhz。

發表于 08-02 10:30

?933次閱讀

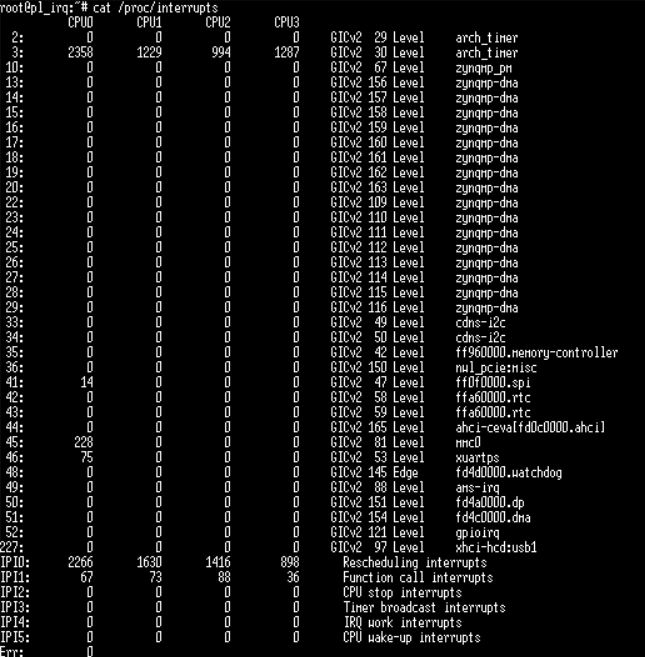

如何在IP的kernel module里設置并使用IP interrupt

有時我們需要為官方 IP 或者自己創建的 IP 生成 kernel module,然后在 linux kernel space 里使用 kernel module 來控制這個 IP。如果要使用 IP 中斷,我們需要在

發表于 08-02 11:35

?792次閱讀

基于 CPU 的 OpenCL 實現案例解析

英特爾正式開源其專有的基于 CPU 的 OpenCL 運行時,首批開源代碼共 718,996 行。現在這個巨大的合并請求正在等待進入 Intel 的 LLVM 存儲庫下游。

發表于 02-19 09:20

?1360次閱讀

評論