1. FPGA學習經歷

階段一:當我們剛開始學習FPGA時,一定會問到一個問題:學習Verilog還是VHDL?

階段二:等我們學習FPGA到一定程度時參加面試時,面試者也會同樣問你一個問題:你以前用Verilog還是VHDL開發?

階段三:你已經習慣某種語言,也發現語言不是學習FPGA時需要區分的問題,它僅僅是硬件描述語言而已。可是,當你發現一份和你使用語言不同的代碼作為參考時,你又開始想:我以后的工作是不是要二種語言都會,這樣工作才會得心應手?

階段四:已經很少人用硬件描述語言了,都用C語言等高級語言開發了?

.....................

當然階段四純屬個人的對未來的推測,但是,近年來,FPGA也高速發展,明顯有當年匯編語言開發到C高級語言開發的趨勢,我們是不是應該不局限于只學習FPGA,而要學習下嵌入式知識,特別是Xilin最新推出的ZYNQ就是最好的切入點,集ARM和FPGA開發與一體。但是,做FPGA的人很難入門嵌入式ARM/Linux,而做ARM/Linux的也很難入門FPGA,對于集ARM和FPGA開發一體的ZYNQ,更是入門難,很多公司都要多個人開發ZYNQ,但未來的趨勢肯定是FPGA2嵌入式,這也是本人開公眾號的目的。

言歸正傳,本節內容要說的是,對于我們做FPGA開發人員來說,如何快速在Verilog和VHDL之間互轉,加快開發產品的進度,而不是因為只懂某一種語言而局限了自己的開發。

2. Verilog和VHDL之間如何互轉

個人目前總結的有2種方法推薦給大家:

2.1 使用EDA軟件自帶的語言模板

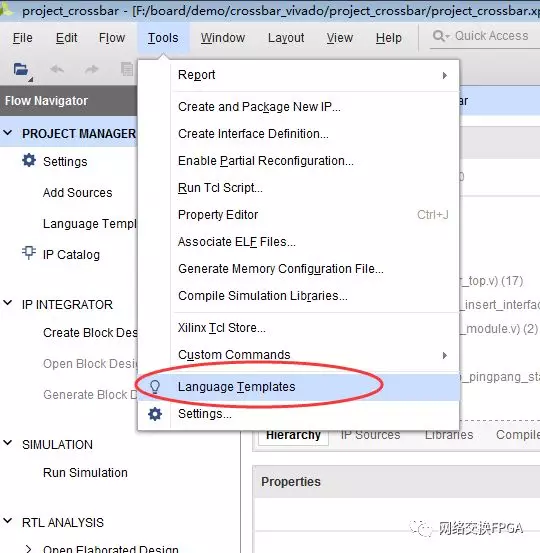

在這里,以Vivado為例,打開它里面的語言模板后,可以對比查看Verilog和VHDL之間的差異,如下圖:

也可以搜索關鍵字,查看對應的語言模板,如下圖,查看always和process時對應的語言模板:

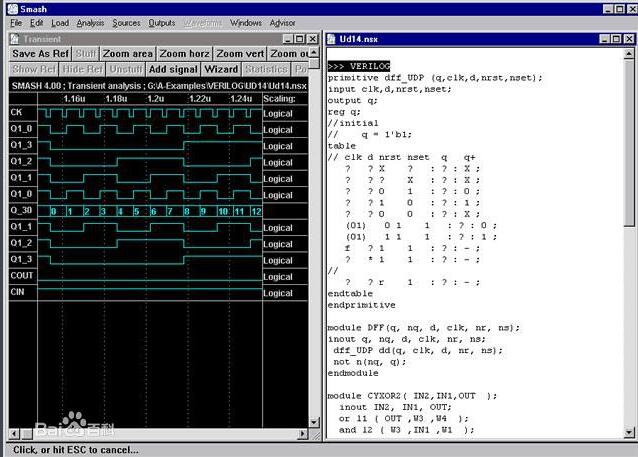

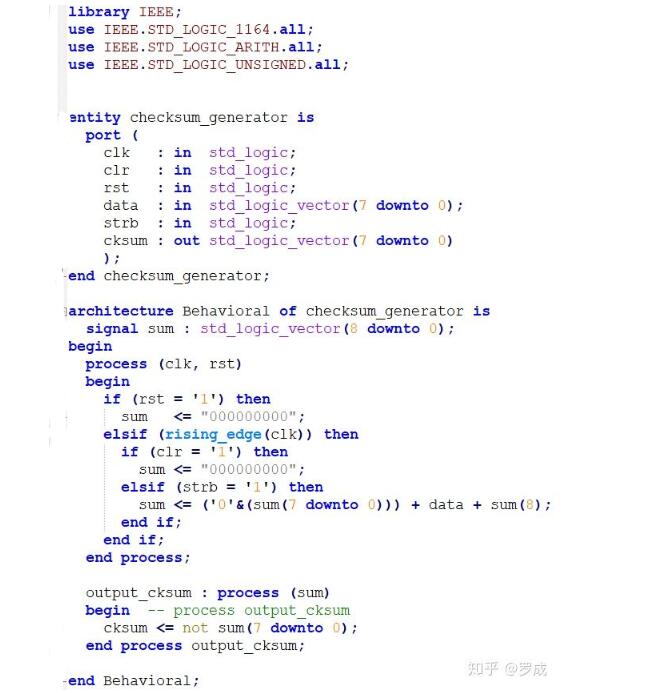

2.2 使用XHDL軟件完成Verilog與VHDL之間的轉換

另外,我們可以使用XHDL軟件來完成互相轉換。雖然它有一定的局限性,但還是足夠我們用。需要注意的是:語言代碼之間轉換時,要求代碼無語法錯誤,注釋為英文,不能為中文,否則就會互轉失敗。

XHDL軟件界面

XHDL測試文件(Verilog)

XHDL軟件運行完成后

XHDL生成的目標文件(VHDL)

上面大致說明了XHDL的功能,但它也有一些限制,大家可以到網上下載后詳細適用,如果找不到源文件,可以私信我傳一份給你。

3. 總結

XHDL畢竟只是一個工具,能幫我們的有限,無法幫我們把所有的代碼一鍵互轉,還是需要我們增強自己的基本理論,記住FPGA編程中和嵌入式語言開發不同的思維方式:即一切皆硬件的思維方式。

-

Verilog

+關注

關注

30文章

1367瀏覽量

112521 -

C語言

+關注

關注

180文章

7633瀏覽量

142459 -

vhdl

+關注

關注

30文章

820瀏覽量

130176

原文標題:Verilog與VHDL之間互轉工具(XHDL)推薦

文章出處:【微信號:FPGAer_Club,微信公眾號:FPGAer俱樂部】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何快速在Verilog和VHDL之間互轉

write_vhdl與write_verilog有什么差異?

VHDL和Verilog 黃金參考手冊

VHDL和Verilog HDL語言對比

Verilog HDL與VHDL及FPGA的比較分析

VHDL,Verilog,System verilog比較

vhdl和verilog的區別_vhdl和verilog哪個好?

vhdl轉換為verilog_VHDL和Verilog誰更勝一籌

探討VHDL和Verilog模塊互相調用的問題

Verilog到VHDL轉換的經驗與技巧總結

評論