1.前言

IP核這個東西相信很多人都不陌生吧,不管是哪個FPGA廠家,都會有自己的一些現成IP核供用戶使用,從而節省設計的開發時間。在一個設計中,個人覺得將模塊變成一個個直觀的圖形界面更有助于理清思路,增強整個設計的邏輯性。以前用過Microsemi的開發平臺,覺得挺人性化的,你寫完代碼后,直接把.v文件拉到畫布中,文件便會以圖形模塊的形式顯示出來,然后拖動鼠標便可以把兩個模塊的對應引腳連接起來,十分方便直觀。

2.Vivado中的IP核封裝

在Vivado平臺中,我一直想尋找看看有沒有這種形式,最終發現并沒有~~。不過Vivado也提供了類似的方式,你首先要把.v文件封裝成IP,然后才能放到畫布中調用,雖然過程有點繁瑣,不過有總比沒有好呀~~

IP核的封裝其實也不會很難,前提是你得把.v文件先準備好,如果連代碼都沒有還扯啥犢子喲。

在打開Vivado工程后,單擊“Tools ---- Creat and Package IP”。嗯,就是這廝了,然后一路Next。

接著出現如下界面,按著選項選擇自己的需求即可,點擊“Next”,正式進入主題。

一般的話選擇第一項即可,如果你的IP核需要走AXI總線,則選擇第三項就行了。

普通IP封裝

進入普通IP封裝界面,如下圖所示,如果你要封裝的IP里包含有IP核,就要選擇第二項,沒有的話默認第一項就行了。然后“Next”,"Finish"就這么簡單的完成了第一階段啦。

接下來你會看到一個新的工程出現,沒錯,這就是IP核的封裝工程了!

我們只要關注右邊的選項就行了。第一項是基本信息,用戶可以給IP命名,進行描述等。

第二項是器件添加,只有選擇了相應的器件,你的IP核才能在那個器件里被使用。單擊器件,右鍵——Add——Add Family Explicitiy,于是便可以選擇要適用的器件系列了。

其他選項也沒啥好改的,直接默認就行了,最后可以看一下IP核的GUI界面,提前欣賞它的風采。

最后一項,點擊最下面的“Package IP”,這樣一個IP的封裝就完成了,就是這么任性這么簡單。

AXI總線IP封裝

有時候將代碼封裝成AXI總線的IP核是非常有用的,當你使用軟核跟你的模塊進行通信時,封裝成AXI總線的IP核,是必須要的。

選擇封裝成AXI總線后,會出現下面的界面,讓你選擇要封裝成哪一種AXI總線,以及有多少個寄存器等等設置。

選擇好你想要的設置后,點擊“Next”后會出現IP封裝界面,注意,此時要選擇第二項“Edit IP”,然后“Finish”。

之后照樣會生成出一個新的工程,和普通IP封裝不同的是,這里會多出一個.v文件,這是AXI總線協議的文件,它已經幫你把頂層做好,你需要把自己的工程加入進去即可。

文件代碼基本就是AXI的時序協議,然后你只需要把你數據端口跟它的數據端口相連接就行了。

如上圖所示,藍色框是它的數據端口,AXI總線會把數據寫入對應的寄存器中,也可以把這些寄存器的數據讀走。紅色框就是給用戶添加代碼的,你可以把自己的模塊放進來,然后數據端口跟藍色框的數據端口相連接即可,這樣通信就建立了。

最后保存,綜合一下,和前面普通IP封裝一樣的處理方式,把IP核生成即可。

3.IP核的調用

IP核封裝完就可以調用出來使用了,東西做出來不就是為了可以裝逼嘛哈哈~~

找到剛才生成IP核的路徑下那個文件夾,里面大概就是下圖這幾項東西了,一項都不要去亂刪啊,很有用的這些。

接著把這個文件夾放到你的工程文件夾里(也可以不用,看個人愛好)。接著打開“IP Catalog”,在空白處右鍵,選擇“Add Repository”,然后選擇剛才說的IP文件夾,確定后,IP就被添加進去了。如下圖所示,iic的IP已經出現在“IP Catalog”里,下次可以直接在這里把這個IP和調出來用,想在哪用就在哪用!

4.總結

很多時候在項目的后期一些成熟的模塊封裝成IP幫助會很大,起碼在界面上你能看到一個個的模塊連在一起思路會非常清晰。同時封裝成IP的模塊也可以給其他人或者其他項目使用,減少開發周期。所以總的來說,將模塊封裝成IP還是很有用處滴。

-

封裝

+關注

關注

126文章

7874瀏覽量

142897 -

IP核

+關注

關注

4文章

327瀏覽量

49485 -

Vivado

+關注

關注

19文章

812瀏覽量

66474

原文標題:Vivado平臺IP核的封裝方式

文章出處:【微信號:FPGAer_Club,微信公眾號:FPGAer俱樂部】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

vivado帶ip核的工程封裝

玩轉Zynq連載21——Vivado中IP核的移植

Xilinx Vivado的使用詳細介紹(3):使用IP核

了解Vivado中IP核的原理與應用

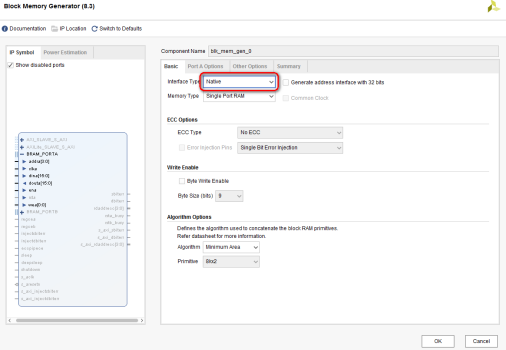

FPGA實現基于Vivado的BRAM IP核的使用

Vivado中xilinx_BRAM IP核使用

Vivado中的IP核封裝

Vivado中的IP核封裝

評論