001.畫出CMOS反相器的電路原理圖。

襯底的連接問題。PMOS襯底接電源,NMOS襯底接地

002.反相器的速度與哪些因素有關?什么是轉換時間(transitiontime)和傳播延遲(propagation delay)?

反相器的速度與哪些因素有關。

(1)電容(負載電容、自載電容、連線電容)較小,漏端擴散區的面積應盡可能小。輸入電容要考慮: (1)Cgs 隨柵壓而變化(2)密勒效應(3)自舉效應

(2)加大晶體管的尺寸(驅動能力),使晶體管的等效導通電阻(輸出電阻)較小。但這同時加大自載電容和負載電容(下一級晶體管的輸入電容)。

(3)提高電源電壓,提高電源電壓可以降低延時,即用功耗換取性能但超過一定程度后改善有限。電壓過高會引起可靠性問題(氧化層擊穿、熱電子等)。

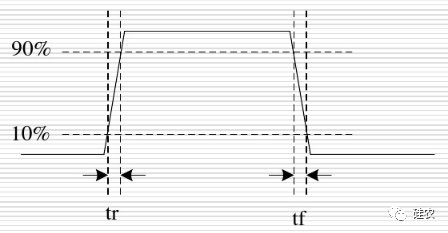

Transition Time(轉換時間):上升時間:從10%Vdd上升到90%Vdd的時間,下降時間L從90%Vdd下降到10%dd的時間。上升時間和下降時間統稱為Transition Time,也有定義為20%到80%。

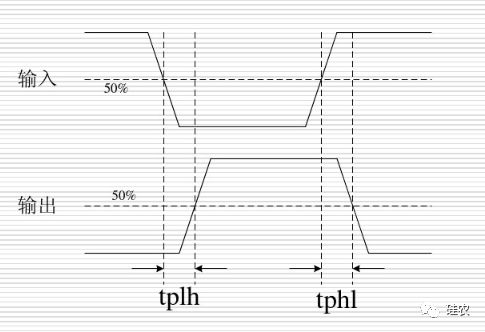

Propagation Delay(傳播延時):在輸入信號變化到50%Vdd到輸出信號變化到50%Vdd之間的時間。

擴展問題:結合fpga的時序報告,介紹一下這些參數在工程實際中有啥用處呢?

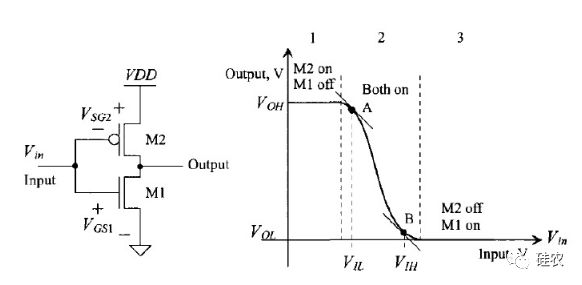

003.解釋一下Vih,Vil,Vol,Voh,Vt。

Vih:輸入電壓由高到低變化時,輸出電壓開始上升且傳輸特性曲線斜率為-1的點,即圖中B點對應的輸入電壓。(仍能維持輸出為邏輯“1”的最大輸出電壓)

Vil:輸入電壓由低到高變化時,輸出電壓開始下降且傳輸特性曲線斜率為-1的點,即圖中A點對應的輸入電壓。(仍能維持輸出為邏輯“0”的最小輸出電壓)

Voh:定義為最小合格高電平。(維持輸出為邏輯“1”的最大輸出電壓)

Vol:定義為最大合格低電平。(維持輸出為邏輯“0”的最大輸出電壓)

CMOS集成電路內部規定Vol = 0v,Voh = Vdd。

Vt:MOS管的閾值電壓

擴展問題:如果輸入電平是(Vil+Vih)/2,會有什么問題?

輸入電壓(Vil+Vih)/2接近于0.5Vdd,CMOS反相器的閾值電壓也接近于0.5Vdd,這樣輸出不確定會是高電平還是低電平,輸出呈亞穩態!

004.什么是原碼,反碼,補碼,符號-數值碼。以4bit為例,給出各自表示的數值范圍。

原碼:符號位+真值,最高位表示符號位,以4bit為例。

[+3]原 = 0011

[-3]原 = 1011

表示范圍:-7到+7

原碼中0000和1000都表示0。

反碼:正數的反碼是它本身,負數的反碼將原碼除符號位外逐位取反。以4bit為例。

[+3]原 = [0011]原 =[0011]反

[-3]原 = [1011]原 = [1100]反

表示范圍:-7到+7

反碼中0000和1111都表示0。

補碼:正數的補碼是它本身,負數的補碼將原碼除符號位外逐位取反再加1。以4bit為例。

[+3]原 = [0011]原 =[0011]反 = [0011]補

[-3]原 = [1011]原 =[1100]反 = [1101]補

表示范圍:-8到+7

補碼中0的表示只有一種形式,即0000,1000表示-8。

以上是有符號數,對于無符號數來說都是來表示整數,其原碼、反碼、補碼都是其本身。

更詳細解釋可參考維基百科。

https://zh.wikipedia.org/wiki/%E6%9C%89%E7%AC%A6%E8%99%9F%E6%95%B8%E8%99%95%E7%90%86

005.十進制轉換為二進制編碼:

127

-127

127.375

-127.375

十進制數轉化為R進制數:整數部分,除R取余法,除到商為0為止。小數部分,乘R取整法,乘到積為0為止。

127 = 0111_1111

-127 = 1111_1111

127.375 =0111_1111.011

-127.375 =1111_1111.011

006.畫出CMOS三態緩沖器的電路原理圖,解釋一下高阻態。

很多東西去搜索還是應該直接用英文,用Google或者Bing國際版,百度真是慘不忍睹。

PMOS襯底接Vdd,CMOS襯底解Gnd,以下為簡化,未畫襯底。

圖1,三態非門,當~EN為1時,最上面的PMOS和最下面的NMOS管截止,所以輸出為高阻態,反之輸出為~A,同理可推理出圖2,EN高電平有效輸出。

圖3,三態緩沖門,當~EN為高電平時,最上面的PMOS管截止,輸出為高阻態,反之,輸出為A。圖4一樣。

圖5,CMOS傳輸門,雙向傳輸,當C=0,~C=Vdd,兩個MOS管都截止,輸入和輸出之間呈現高阻態,當C=Vdd,~C=0,如果0 <= Vi <= Vdd – Vt(NMOS),NMOS管導通,如果|Vt(PMOS)|<= Vi <= Vdd,PMOS管導通,所以Vi在0到Vdd之間,總有一個MOS管導通,實現傳輸門。

圖6,三態非門,在反相器后面加一個傳輸門,當~EN為低電平,傳輸門導通,輸出Y = ~A,反之傳輸門截止,輸出高阻態。如果想要EN高電平有效,交換傳輸門上下端子的反相器即可。

高阻態:電路的一種輸出狀態,既不是高電平也不是低電平,如果高阻態再輸入下一級電路的話,對下級電路無任何影響,可以理解為斷路,不被任何東西所驅動,也不驅動任何東西

007.什么是Open-Drain Output?

Open-Drain Output漏極開路輸出,稱為OD門,兩個OD門并聯可以實現線與功能,輸出端外接的上拉電阻提高驅動能力

008.只用2輸入mux,實現與,或,非,異或。2輸入mux定義為o = s ? a :b;

與:out = (a == 1'b0)? 1'b0: ((b == 1'b0)? 1'b0: 1'b1);

改進版:out = (a == 1'b1)? b: 1'b0;

或:out = (a == 1'b1)? 1'b1: ((b == 1'b1)? 1'b1: 1'b0);

改進版:out = (a == 1'b0)? b: 1'b1;

非:out = (a == 1'b1)? 1'b0: 1'b1;

異或:out = (a == 1'b1)? ((b == 1'b1)? 1'b0: 1'b1) : ((b == 1'b0)? 1'b0: 1'b1);

009.相同面積的cmos與非門和或非門哪個更快?

數集學的不夠深刻,需要慢慢體會。

電子遷移率是空穴的2.5倍(在硅基CMOS工藝中),運算就是用這些大大小小的MOS管驅動后一級的負載電容,翻轉速度和負載大小一級前級驅動能力相關。為了上升延遲和下降延遲相同,PMOS需要做成NMOS兩倍多大小。

載流子的遷移率,對PMOS而言,載流子是空穴;對NMOS而言,載流子是電子。

PMOS采用空穴導電,NMOS采用電子導電,由于PMOS的載流子的遷移率比NMOS的遷移率小,所以,同樣尺寸條件下,PMOS的充電時間要大于NMOS的充電時間長,在互補CMOS電路中,與非門是PMOS管并聯,NMOS管串聯,而或非門正好相反,所以,同樣尺寸條件下,與非門的速度快,所以,在互補CMOS電路中,優先選擇與非門。

-

CMOS

+關注

關注

58文章

5710瀏覽量

235420 -

反相器

+關注

關注

6文章

311瀏覽量

43292 -

Verilog

+關注

關注

28文章

1351瀏覽量

110077

原文標題:Verilog 99題之001-009

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Verilog 99題:畫出CMOS三態緩沖器的電路原理圖

Verilog 99題:畫出CMOS三態緩沖器的電路原理圖

評論