1 概述

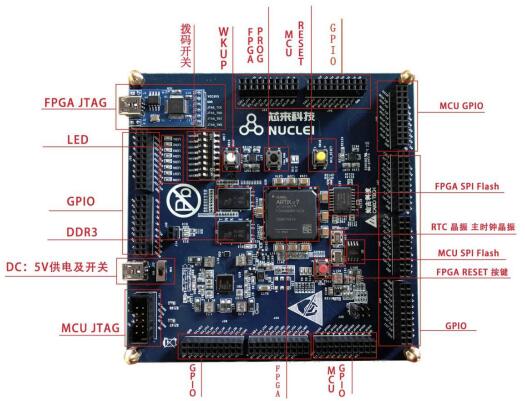

為了便于初學者能夠快速地學習RISC-V CPU設計和RISC-V嵌入式開發,蜂鳥E203開源MCU原型SoC(在本文中將其簡稱為“MCU SoC”或者“SoC”)定制了基于Xilinx FPGA的專用開發板(在本文中將其簡稱為“FPGA開發板”)和專用JTAG調試器(在本文中將其簡稱為“JTAG調試器”)。

完整的FPGA開發板原型(包括FPGA開發板和調試器)如圖1-1所示。

圖1-1 蜂鳥FPGA開發板和JTAG調試器,后文將分別予以詳述。

2 蜂鳥FPGA開發板概述

2.1 FPGA開發板總體說明

為了便于蜂鳥FPGA開發板的使用,FPGA開發板具備如下特點:

一板兩用,該開發板不僅可以用于一塊FPGA開發板作為電路設計使用,同時由于其預燒了蜂鳥E203開源SoC(包括E203內核),因此其可以直接作為一塊MCU SoC原型開發板進行嵌入式軟件開發。即:

(1)對于不懂FPGA軟件開發的用戶完全無需做任何的操作,該開發板會預先燒寫開源的蜂鳥E203 Core和配套SoC,上電后即可當做一塊MCU嵌入式開發板來用。

(2) 對于了解FPGA使用的硬件用戶而言,也可以將其當做普通的FPGA 開發板來燒寫普通的Verilog電路以進行FPGA開發。

由于其預先燒寫的蜂鳥E203 Core和配套SoC源代碼完全開源,可以對其任意進行修改或二次開發。

并且由于開源的蜂鳥E203 MCU SoC的 “FPGA燒寫文件(mcs格式)”會上傳到:

https://github.com/SI-RISCV/e200_opensource/tree/master/fpga/nucleikit/prebuilt_mcs 目錄下,用戶可以隨時重新燒寫此FPGA板將其恢復成為預裝的MCU嵌入式開發板。

2.2 FPGA開發板的購買途徑

FPGA開發板的淘寶購買網頁鏈接:

https://item.taobao.com/item.htm?id=580813056318

¥HoCVbR7Z0I3¥

(復制該鏈接,打開手機淘寶即可查看)

2.3 FPGA開發板的硬件指標

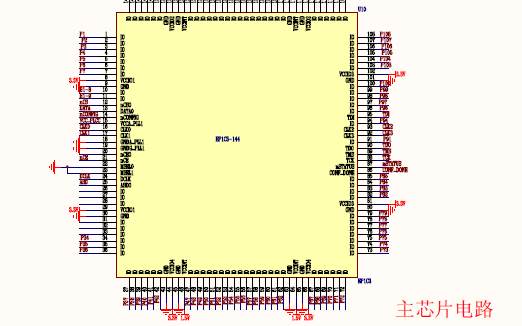

蜂鳥E203專用FPGA開發板是一款入門級Xilinx FPGA開發板,如圖2-1所示。

圖2-1 蜂鳥FPGA開發板總體圖該FPGA開發板的硬件特性如下:

使用的FPGA型號為Xilinx XC7A100T。

板載雙晶振設計:100MHz主時鐘和32.768K RTC時鐘。

配備單獨直流5V供電,并設有電源開關,如圖2-1中的“DC:5V供電及開關”標注。

配備獨立的FPGA_RESET按鍵,用戶可用此按鍵作為FPGA的復位按鍵。

配備多達126個引出的FPGA GPIO,用于用戶自定義使用。

配備板載的Xilinx Platform Cable USB JTAG下載器,用于對FPGA進行比特流的燒寫,如圖2-1中的“FPGA JTAG”標注。

配備兩顆MT41K128M16JT-125K DDR III 顆粒。

配備獨立的128M-bit FPGA SPI Flash,此Flash用于存儲mcs格式的比特流文件:

(1)熟悉Vivado和Xilinx FPGA使用的用戶應該了解,bitstream文件燒錄到FPGA中去之后FPGA不能掉電,因為一旦掉電之后FPGA燒錄的內容即丟失,需要重新使用Vivado的Hardware Manager進行燒錄方能使用。為了方便用戶使用,Xilinx的FPGA開發板可以將需要燒錄的內容寫入開發板上的Flash中(以mcs格式),然后在每次FPGA上電之后通過硬件電路自動將需要燒錄的內容從外部的Flash中讀出并燒錄到FPGA之中(該過程非常的快,不影響用戶使用)。由于Flash是非易失性的內存,具有掉電后仍可保存的特性,因此意味著將需要燒錄的內容寫入 Flash后,每次掉電后無需使用Hardware Manager人工重新燒錄(而是硬件電路快速自動完成),即等效于,FPGA上電即可使用。

(2)除了上電自動對FPGA重新進行燒錄外,用戶還可以通過強行按FPGA開發板上的“FPGA_PROG”按鍵觸發硬件電路使用此Flash中的內容對FPGA重新進行燒錄。FPGA開發板上的“FPGA_PROG”按鍵位置請參見圖2-1中標注所示。

為了便于此開發板直接作為MCU原型嵌入式開發板使用,將蜂鳥E203開源SoC的頂層引腳直接連到開發板上,并配有明顯的絲印標注。請參見第2.5節了解詳細介紹。

為了便于此開發板作為常規FPGA開發板使用,配備分離的撥碼開關和LED燈,請參見第2.6節了解詳細介紹。

2.4 FPGA開發板的電路原理圖

該開發板的電路原理圖保存于:

https://github.com/SI-RISCV/e200_opensource/tree/master/boards目錄下,請用戶自行查閱。

(查看方式:1.下滑頁面到文章最末,點擊“閱讀原文”查看e200_opensource項目總鏈接;2.在公眾號后臺回復“鏈接”,即可訪問)

2.5 FPGA開發板的MCU部分

為了便于此開發板直接作為MCU原型嵌入式開發板使用,將“蜂鳥E203開源SoC”(簡稱SoC)的頂層引腳直接連到開發板上,并配有明顯的絲印標注,詳細描述如圖2-2中所示,其要點如下:

FPGA預先燒寫成為“蜂鳥E203開源MCU SoC”(簡稱SoC)

為了實現MCU的功能,在FPGA開發板上專門配備了一個Nor Flash用于存儲MCU的軟件程序。

MCU SoC的兩個輸入時鐘輸入分別按照如下方式產生:

(1)低速的實時時鐘直接由FPGA開發板上的32.768KHz時鐘源輸入(2)高速時鐘由FPGA開發板上的100MHz時鐘經過FPGA內部PLL降頻而得(16MHz)。

將SoC的相關輸入輸出管腳明確的做到FPGA開發板上,并且用印刷字體明確的表明端口號。

有關此SoC的輸入輸出管腳列表的詳細信息,

請參見https://github.com/SI-RISCV/e200_opensource/blob/master/doc目錄下的文檔《蜂鳥E203開源SoC簡介》。

注意:所有的管腳都只是映射到FPGA內部的普通端口(雙向IO)上,然后通過FPGA Project通過設置端口映射把FPGA端口映射到這些外部預定義的開發板引腳。有關FPGA Project的詳細信息請參見:https://github.com/SIRISCV/e200_opensource/blob/master/doc 目錄下的文檔《蜂鳥E203快速上手介紹》。

更多詳細描述如圖2-2中所示。

圖2-2 蜂鳥FPGA開發板的MCU定制部分

2.6 FPGA開發板的常規功能部分

為了便于此開發板作為常規FPGA開發板使用,配備分離的撥碼開關和LED燈,如圖2-3中所示。

注意:此組撥碼開關和LED并沒有被連接到FPGA的管腳上,用戶可以自由的進行跳線使其控制開發板上的其他信號。如圖2-3中所示,用戶可以通過用杜邦線跳線將“撥碼開關”與MCU SoC的GPIO接口連接,相當于通過撥碼開關來產生GPIO的輸入,從而可以編程構建形象化的簡單Demo。

圖2-3 蜂鳥FPGA開發板的撥碼開關和LED燈以及跳線示例

2.7 燒寫蜂鳥E203項目至FPGA開發板

有關如何燒寫蜂鳥E203項目(包括SoC和處理器內核)至此FPGA開發板的具體操作步驟,請參見https://github.com/SI-RISCV/e200_opensource/blob/master/doc目錄下的文檔《蜂鳥E203快速上手介紹》。

2.8 使用FPGA開發板進行軟件開發與調試

有關如何使用FPGA開發板進行軟件開發與調試的具體操作步驟,請參見https://github.com/SI-RISCV/e200_opensource/blob/master/doc目錄下的文檔《蜂鳥E203快速上手介紹》。

(查看方式:1.下滑頁面到文章最末,點擊“閱讀原文”查看e200_opensource項目總鏈接;2.在公眾號后臺回復“鏈接”,即可訪問)

3 蜂鳥JTAG調試器

3.1 JTAG調試器總體說明

圖3-1 蜂鳥E203專用的JTAG調試器

為了便于初學者能夠快速地學習RISC-V嵌入式開發,“蜂鳥MCU SoC”定制了專用的JTAG調試器,該調試器具有如下特性:

調試器的一端為普通U盤接口,便于直接將其插入主機PC的USB接口,另一端為標準的4線JTAG接口和2線UART接口。

調試器具備USB轉JTAG功能,通過標準的4線JTAG接口與蜂鳥E203 FPGA開發板連接。由于蜂鳥E203 內核支持標準的JTAG接口,通過此接口可以程序下載或進行交互式調試。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

602997 -

JTAG

+關注

關注

6文章

399瀏覽量

71673

原文標題:蜂鳥FPGA開發板和JTAG調試器介紹

文章出處:【微信號:real_farmer,微信公眾號:硅農亞歷山大】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【MYMINIEYE Runber蜂鳥開發版免費試用連載】國產FPGA試用評測之MYMINIEYE Runber蜂鳥開發板

FPGA JTAG的配置模式詳細說明

蜂鳥FPGA開發板及JTAG下載器詳細說明

蜂鳥FPGA開發板及JTAG下載器詳細說明

評論