本視頻將指您介紹如何使用Vivado設計套件中的交互式“IO Pin Planning”和“Device Exploration”功能。具體來說,IO規劃包括:在設計中創建,配置,分配和管理IO端口以及時鐘邏輯 對象。該視頻教程描述了在設計流程的不同階段如何執行IO規劃的步驟。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

IO

+關注

關注

0文章

448瀏覽量

39132 -

賽靈思

+關注

關注

32文章

1794瀏覽量

131246 -

邏輯

+關注

關注

2文章

833瀏覽量

29464

發布評論請先 登錄

相關推薦

Vivado中DDRX控制器(mig)ip核配置中關于命令序號選擇和地址映射說明

本篇主要討論Vivado中DDRX控制器(mig)ip核配置中關于命令序號選擇和地址映射說明(一) 利用Xilinx 7系列FPGA開發時,經常需要驅動外部存儲器--DDRX。Xilinx提供了

Xilinx_Vivado_SDK的安裝教程

I Agree,然后點擊 Next: 選擇 Vivado HL System Edition(一般選擇這個設計套件比較完整,它比 Vivado HL Design Edition 多了一個 System Generator f

使用Vivado通過AXI Quad SPI實現XIP功能

本博客提供了基于2023.2 Vivado的參考工程,展示如何使用Microblaze 地執行(XIP)程序,并提供一個簡單的bootloader。

激光雷達在城市規劃中的應用

Detection and Ranging,簡稱LiDAR)技術作為一種先進的遙感技術,為城市規劃提供了一種全新的數據獲取方式。 1. 高精度地形測繪 激光雷達技術能夠提供高精度的地形數據,這對于城市規劃至關重要。傳統的地形測繪方法耗時且成本高昂,而激光雷達可以

本地IO與遠程IO:揭秘工業自動化中的兩大關鍵角色

在工業自動化領域,IO(Input/Output,輸入/輸出)模塊扮演著至關重要的角色。它們作為連接控制系統與現場設備的橋梁,負責數據的采集與指令的執行。然而,隨著技術的不斷進步,IO

遠程IO與分布式IO的區別

在工業自動化和控制系統設計中,遠程IO(Input/Output)和分布式IO是兩個重要的概念。它們各自具有獨特的特點和優勢,適用于不同的應用場景。本文將詳細探討遠程

在不重新安裝Vivado的情況下,是否能夠安裝線纜驅動器?

如果 Xilinx USB/Digilent 線纜驅動器在安裝 Vivado 設計套件時還沒有安裝,或者 Xilinx USB/Digilent 線纜驅動器被禁用,在不全面重新安裝

Vivado編譯常見錯誤與關鍵警告梳理與解析

Xilinx Vivado開發環境編譯HDL時,對時鐘信號設置了編譯規則,如果時鐘由于硬件設計原因分配到了普通IO上,而非_SRCC或者_MRCC專用時鐘管腳上時,編譯器就會提示錯誤。

使用IO-Link技術能帶來哪些優勢?細數IO-Link八大優勢

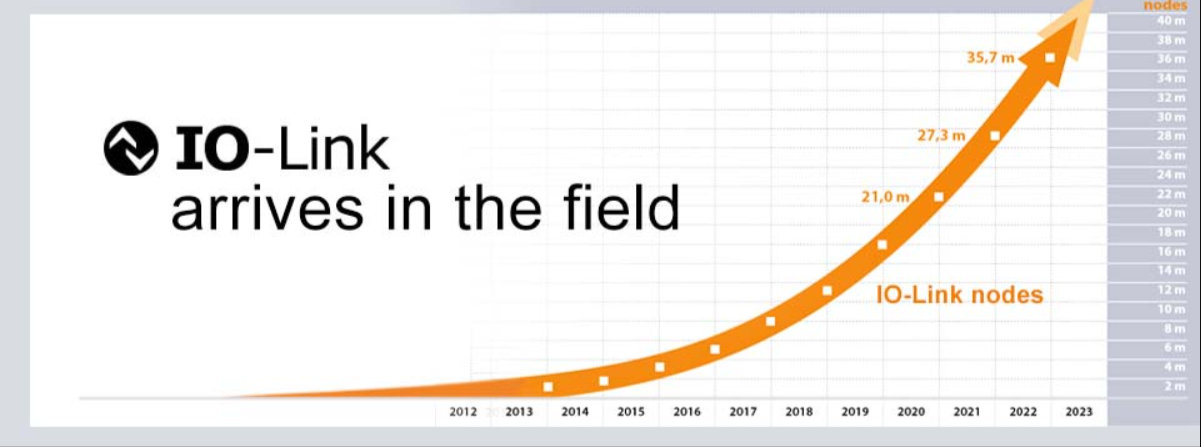

IO-Link是國際標準化的跨供應商IO技術,能夠實現從控制系統到傳感器/執行器級別的雙向通信。

verilog中for循環是串行執行還是并行執行

在Verilog中,for循環是并行執行的。Verilog是一種硬件描述語言,用于描述和設計數字電路和系統。在硬件系統中,各個電路模塊是同時

EtherCAT IO的接線方法和流程是怎樣的?

(例如傳感器和執行器)的接線和配置過程。 一、EtherCAT IO的基本概念 在詳細討論具體的接線方法和流程之前,我們首先需要了解EtherCAT IO的基本概念。 1.

如何禁止vivado自動生成 bufg

在Vivado中禁止自動生成BUFG(Buffered Clock Gate)可以通過以下步驟實現。 首先,讓我們簡要了解一下什么是BUFG。BUFG是一個時鐘緩沖器,用于緩沖輸入時鐘信號,使其更穩

在Vivado設計套件中如何執行IO的規劃

在Vivado設計套件中如何執行IO的規劃

評論