FPGA編程語言為何叫硬件描述語言?硬件即FPGA硬件,硬件描述語言,也就自然地告訴我們可以通過語言來描述FPGA內部硬件。如:用y=a&b來描述一個2輸入的與門,用PLL來描述類似外部時鐘管理芯片。因此,要想學好FPGA,你得用硬件的思維方式來編寫代碼,注重FPGA的系統結構設計,好的系統結構設計會帶來質的飛躍,這就告訴我們RTL Coding其實是硬件結構設計,而非基于處理器架構的C語言程序開發,好的RTL Coding就是好的硬件結構。2.FPGA設計是做串并操作的時序設計?FPGA內部硬件之間的通信為多對多節點通信,不僅存在無先后順序的并行邏輯,而且還存在先后順序的串行邏輯,這和CPU基于指令的順序執行邏輯完全不同,我們需要嚴格控制設計中各個信號之間的時間關系,以滿足最終的時間上的需求,即時序要求。

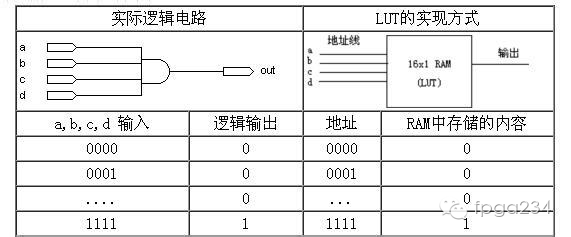

因此,FPGA設計就是針對既有串行操作,又有并行操作的時序設計,即FPGA串并操作的時序設計。3.FPGA串并操作,該如何理解?a.執行完A后再執行B;b.A和B之間并行執行,且沒有關聯;c.A和B之間并行執行,且開始時有先后順序,即串行邏輯;d.FPGA的復雜系統包含上述多種靈活組合,設計時需多多琢磨思考,合理設計。4.FPGA內部最基本硬件結構LUT,你理解嗎?LUT的原理很簡單,就是把各種可能的結果存起來標個號,每次根據輸入的號來輸出結果。如:一位加法器有4種可能輸入對應3種結果,就只需要做一張表格,把所有的輸入和輸出一一對應即可。

圖1 LUT實現方式

理解了LUT原理,我們可以用相同的思想來實現DDS、簡單乘法、簡單三角函數等,有時可以大大省資源,因為畢竟FPGA最終都是有多個LUT級聯+Reg+其它 來實現各種復雜的硬件電路。

5.FPGA設計關鍵在于結構的設計,你同意嗎?a.首先,清楚FPGA的內部結構,基本結構為LUT;

b.然后,按照功能、時鐘域、串并操作、數據流和控制流來綜合考慮系統的結構;

c.最后,根據面積、速度和功耗來不斷優化系統結構,設計出最合理的系統結構。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603009 -

硬件

+關注

關注

11文章

3312瀏覽量

66200 -

時序

+關注

關注

5文章

387瀏覽量

37318

原文標題:FPGA的幾點總結,你同意嗎?

文章出處:【微信號:FPGAer_Club,微信公眾號:FPGAer俱樂部】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA的幾點總結,你同意嗎?

對于PCB設計重要線信號處理,應該注意哪幾點?

為什么大量的人會覺得FPGA難學?精選資料推薦

增量型拉線位移傳感器的幾點注意事

ACTEL-FPGA獨特的幾點優勢

FPGA的幾點重要總結

FPGA的幾點重要總結

評論