PCB設計中提高電磁兼容性能的電路措施有哪些?

答:(1) 可用在PCB走線上串接一個電阻的辦法,降低控制信號線上下沿跳變速率 。

(2) 盡量為繼電器等提供某種形式的阻尼(高頻電容、反向二極管等)。

(3) 對進入印制板的信號要加濾波,從高噪聲區到低噪聲區的信號也要加濾波,同時用串終端電阻的辦法,減小信號反射。

(4) MCU無用端,要通過相應的匹配電阻接電源。或接地或定義成輸出端,集成電路上該接電源、地的端都要接,不要懸空。

(5) 閑置不用的門電路輸入端,不要懸空,而是通過相應的匹配電阻接電源或接地。閑置不用的運放正輸入端接地,負輸入端接輸出端。

(6) 為每個集成電路設一個高頻去耦電容 每個電解電容邊上都要加一個小的高頻旁路電容。

(7) 用大容量的鉭電容或聚酯電容而不用電解電容作電路板上的充放電儲能電容。使用管狀電容時,外殼要接地 。

2.AD18安裝好后每次打開軟件都會彈出這句話,請問是怎么一回事?Could not start Vault Explorer. Please,make sure that VaultExplorer extension is installed properly

答:可能是本地程序沒有河蟹干凈,建議重裝,先把根目錄的原AD文件全部刪除干凈,再次安裝破解時,先把殺毒軟件關掉。

3.最近在使用ad 09的時候出現Preferences選項無法打開?

答:可能是軟件BUG了。也可以試試快捷鍵TP ,也能進入此設置頁面。

4.怎么把AD16的F1鍵進入網頁的操作給取消?

答:在pcb工具欄的空白處有鍵選擇最后一項:

進入快捷鍵修改欄,進行修改。

5.PCB設計中消除串擾的方法有哪幾種?

答:1、兩種串擾的大小均隨負載阻抗的增大而增大,所以應對由串擾引起的干擾敏感的信號線進行適當的端接。

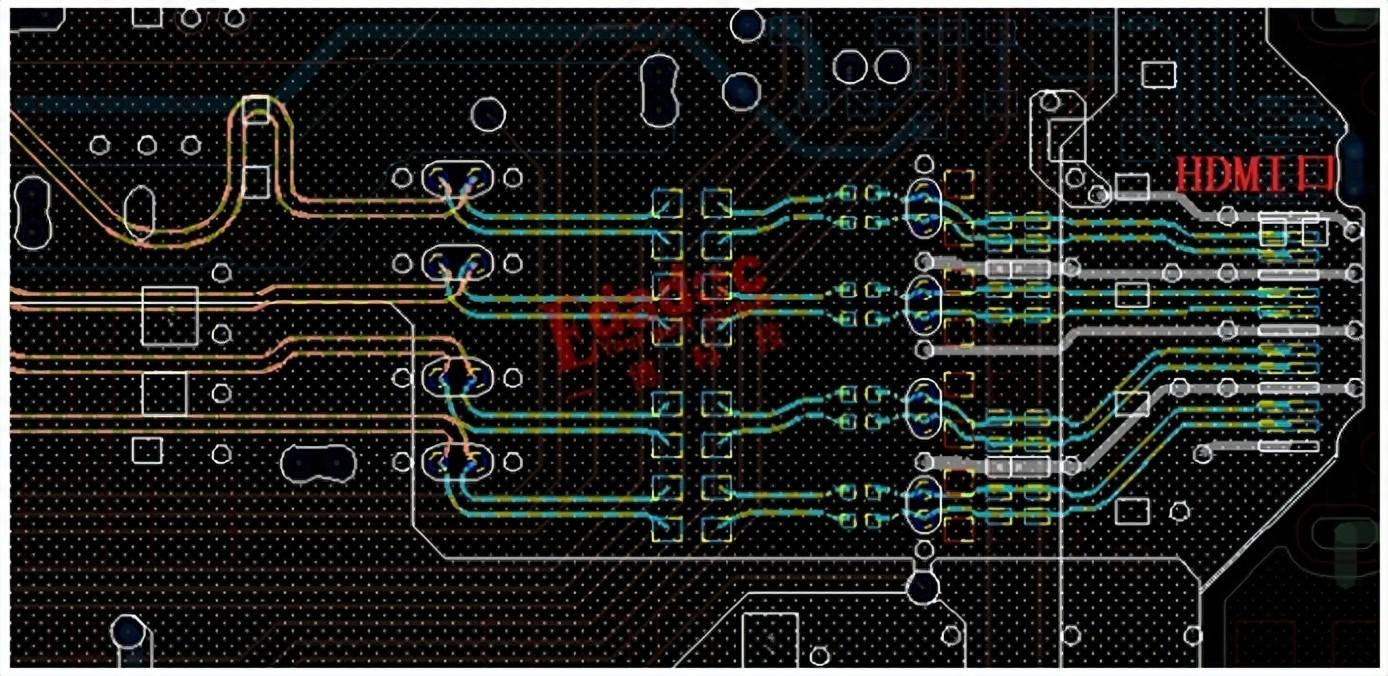

2、盡可能地增大信號線間的距離,可以有效地減少容性串擾。進行接地層管理,在布線之間進行間隔(例如對有源信號線和地線進行隔離,尤其在狀態發生跳變的信號線和地之間更要進行間隔)和降低引線電感。

3、在相鄰的信號線間插入一根地線也可以有效減小容性串擾,這根地線需要每1/4波長就接入地層。

4、對于感性串擾,應盡量減小環路面積,如果允許的話,消除這個環路。

5、避免信號共用環路。

6、關注信號完整性:設計者要在焊接過程中實現端接來解決信號完整性。采用這種辦法的設計者可專注屏蔽用銅箔的微帶長度,以便獲得信號完整性的良好性能。對于在通信結構中采用密集連接器的系統,設計者可用一塊PCB作端接。

6.我在等長繞線怎么是方形的?怎么換成有折角形狀?

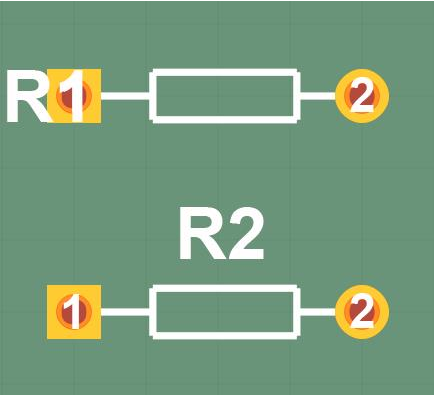

這個是設置不到位引起的 可以在等長的時候按 字母鍵盤上面的數字鍵“1”“2”來調整這個弧度,其中1為減小弧度 2位增大弧度如下圖所示:

7.AD19只要我一打開pcb就一直彈錯誤,軟件崩潰。

答:19很吃電腦配置,如果正常破解成功,出現這種情況,一般是配置跟不上,建議換個低版本。

8.新人入門,跟著老師學習AD17 89C51開發板實操,設置啥的都是跟著老師一步步弄得,但是敷銅完成后不是紅色的,這是怎么回事?怎么解決呢?求大神指導

答:快捷鍵進TGM入進入銅皮管理器可以很清晰的看到你銅皮的情況。之后可以根據情況加以修改。

9.如何導入導出AD規則?

答:按快捷鍵 DR進入規則管理器然后再左側單機右鍵選擇Export-rule 全選所有的規則 就可以導出了。

10.PCB布局時需要排除哪些低級錯誤 ?

答:● 印制板尺寸是否與加工圖紙尺寸相符?能否符合PCB制造工藝要求?有無定位標記?

● 元件在二維、三維空間上有無沖突?

● 元件布局是否疏密有序,排列整齊?是否全部布完?

● 需經常更換的元件能否方便的更換?插件板插入設備是否方便?

● 熱敏元件與發熱元件之間是否有適當的距離?

● 調整可調元件是否方便?

● 在需要散熱的地方,裝了散熱器沒有?空氣流是否通暢?

● 信號流程是否順暢且互連最短?

● 插頭、插座等與機械設計是否矛盾?

● 線路的干擾問題是否有所考慮?

-

集成電路

+關注

關注

5389文章

11573瀏覽量

362259 -

電阻

+關注

關注

86文章

5525瀏覽量

172266 -

pcb

+關注

關注

4322文章

23124瀏覽量

398510

原文標題:【技術問答】PCB布局有哪些低級錯誤?PCB設計中怎么消除串擾?

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

關于PCB設計中的低級錯誤檢查步驟心得(針對于AD15)

AD15軟件中對PCB低級錯誤檢查的步驟

儀表放大器PCB布局三大常見錯誤_儀表放大器PCB布局的正確方法

PLC編程時最容易犯的低級錯誤匯總

PCB布局約束及其對組裝的影響

DFM-BOM智能分析,不再出現低級錯誤

有可能毀掉您設計的PCB布局樣式錯誤

PCB布局有哪些低級錯誤?

PCB布局有哪些低級錯誤?

評論