LLC的優勢之一就是能夠在比較寬的負載范圍內實現原邊MOSFET的零電壓開通(ZVS),MOSFET的開通損耗理論上就降為零了。要保證LLC原邊MOSFET的ZVS,需要滿足以下三個基本條件:

1)上下開關管50%占空比,1800對稱的驅動電壓波形;

2)感性諧振腔并有足夠的感性電流;

3)要有足夠的死區時間維持ZVS。

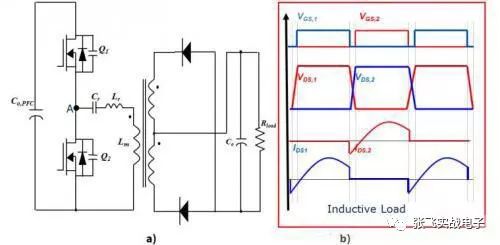

圖a)是典型的LLC串聯諧振電路。圖b)是感性負載下MOSFET的工作波形。由于感性負載下,電流相位上會超前電壓,因此保證了MOSFET運行的ZVS。要保證MOSFET運行在感性區,諧振電感上的諧振電流必須足夠大,以確保MOSFET源漏間等效的寄生電容上存儲的電荷可以在死區時間內被完全釋放干凈。

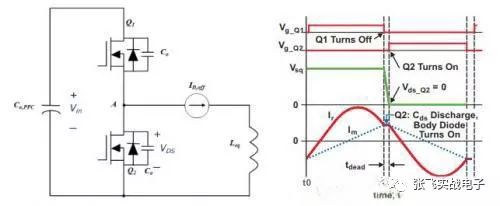

當原邊的MOSFET都處于關斷狀態時,串聯諧振電路中的諧振電流會對開關管MOSFET的等效輸出電容進行充放電。MOSFET都關斷時的等效電路如下圖所示:

通過對上圖的分析,可以得出需要滿足ZVS的兩個必要條件,如下:

公式看上去雖然簡單,然而一個關于MOSFET等效輸出電容Ceq的實際情況,就是MOSFET的等效寄生電容是源漏極電壓Vds的函數,之前的文章對于MOSFET的等效寄生電容進行過詳細的理論和實際介紹。,也就是說,等效電容值的大小會隨著Vds的變化而變化。如下圖所示,以Infineon的IPP60R190P6為例:

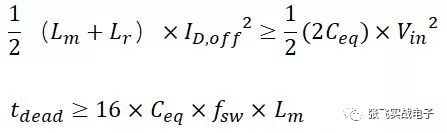

LLC串聯諧振電路MOSFET的Vds放電過程分為四個階段,如下圖所示, (I) 380V-300V; (II) 300V-200V; (III) 200V-100V; (IV)100V-0V。

從圖中可以看出,(I)和(IV)兩部分占據了Vds放電時間的將近2/3,此時諧振腔的電感電流基本不變。這兩部分之所以占據了Vds放電的大部分時間,主要原因在于當Vds下降到接近于0的時候,MOFET源漏間的寄生電容Coss會指數的增加。因此要完全釋放掉這一部分的電荷,需要更長的LLC諧振周期和釋放時間。

因此選擇合適的MOSFET(足夠小的等效寄生電容),對于ZVS的實現至關重要,尤其是當Vds接近于0的時候,等效輸出電容要足夠小,這樣還可以進一步降低死區時間并提高LLC的工作效率。

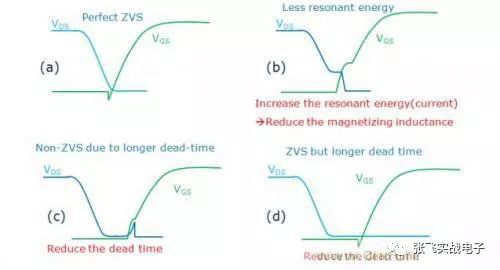

下圖進一步說明如何選擇合適的ZVS方案。

圖(a):理想的ZVS波形;

圖(b):Vds還沒下降到0,Vgs已經出現。此種情況下,LLC串聯諧振就會發生硬開關。應對之策需要減少變壓器的勵磁電流,或者適當增加死區時間(如果IC選定,死區時間一般就固定了);

圖(c):實現了ZVS,但是諧振腔的電流不足以維持MOSFET體內二極管的持續導通。

圖(d)死區時間過于長了,會降低整個LLC的工作效率。

總之,MOSFET的等效輸出電容對于LLC原邊MOSFET ZVS的實現是至關重要的。如果MOSFET已經選定,諧振腔需要仔細計算、調試和設定,并選取合適的死區時間,來覆蓋所有負載的應用范圍。實際應用中對于穩態運行的硬開關都可以通過設計進行修正從而達到穩定運行的設計目的。然而開機過程中的硬開關(軟啟高頻到低頻過程中),尤其是開機過程中的頭幾個開關周期,對于有些設計和方案,硬開關是避免不了的。

-

MOSFET

+關注

關注

147文章

7156瀏覽量

213148 -

諧振電路

+關注

關注

11文章

165瀏覽量

26964 -

LLC

+關注

關注

36文章

567瀏覽量

76745 -

張飛電子

+關注

關注

54文章

175瀏覽量

12588

原文標題:MOSFET電容對LLC串聯諧振電路的作用

文章出處:【微信號:fcsde-sh,微信公眾號:fcsde-sh】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

淺析基于碳化硅MOSFET的諧振LLC和移相電路在新能源汽車的應用

如何排除LLC諧振轉換器中出現的MOSFET故障?

LLC電路中的MOSFET

MOSFET電容在LLC串聯諧振電路中的作用

淺析MOSFET電容在LLC串聯諧振電路中的應用

淺析MOSFET電容在LLC串聯諧振電路中的應用

評論