在使用Vivado Logic Analyzer調試時,常會遇到這樣的情形:當前階段需要觀測信號xa_reg,下一階段需要觀測xb_reg,兩個階段原始設計并沒有改變,只是需要將xa_reg替換為xb_reg。此時,一種方法是回到綜合后的設計,通過Setup Debug重新設置待觀測信號,這樣固然可行,但需要對設計重新布局布線,耗時,效率低。另一種方法是采用ECO(Engineering Change Order)的模式,直接在布線后的網表中實現替換操作。相比于前一種方法,這種方法省時高效。

1

第1步:打開布線后的dcp,并將Vivado布局(layout)切換為ECO模式,如圖1所示。

圖1

一旦切換到ECO模式,Vivado就會顯示出ECO Navigator和Scratch Pad,如圖2所示。

圖2

2

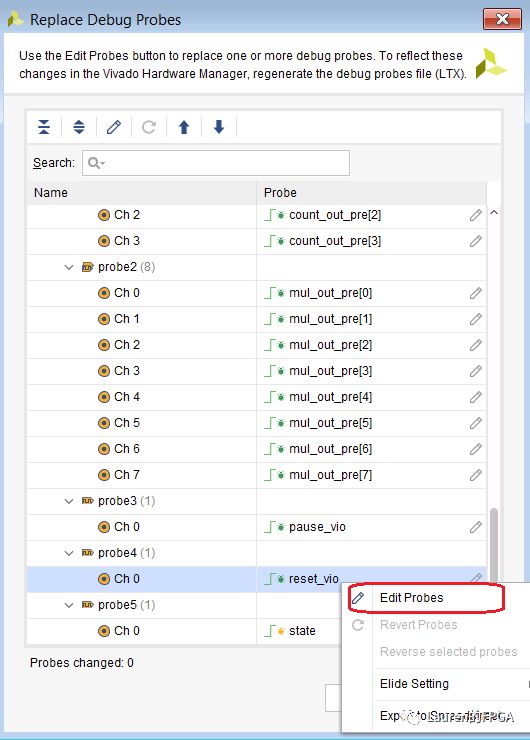

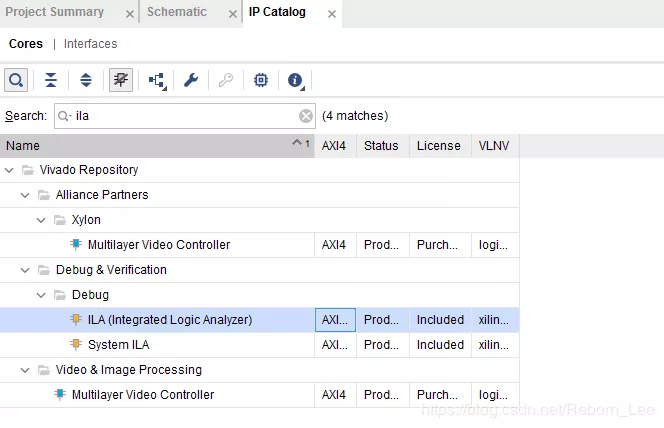

第2步:選中圖2中的Replace Debug Probes,執行替換操作。此時會顯示出當前ILA多連接的待測信號,如圖3所示。

圖3

3

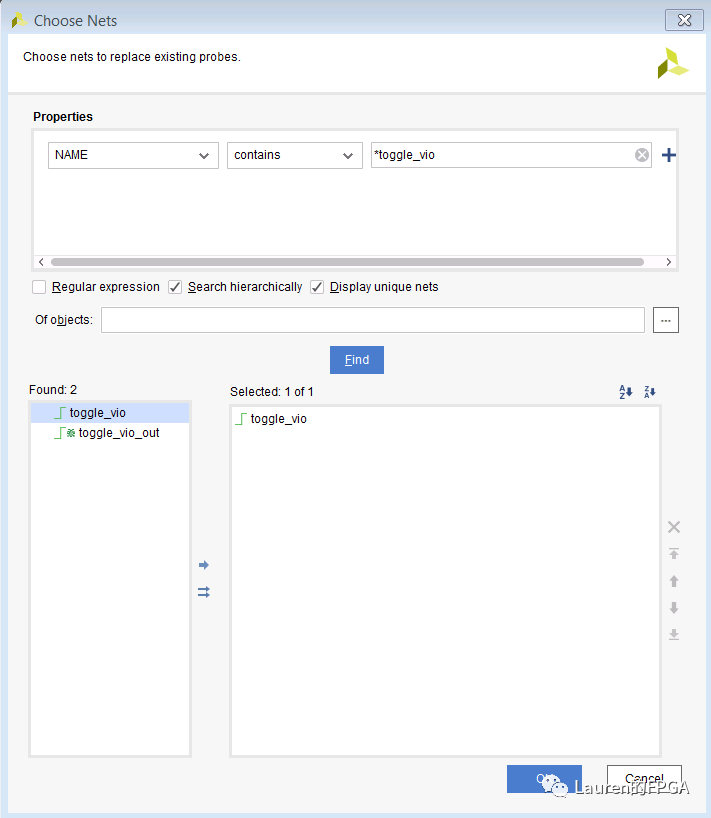

第3步:選擇要替換的信號,如圖3中的reset_vio,右鍵選擇Edit Probes,彈出Choose Nets窗口,如圖4所示。在該窗口下,可找到用于替換reset_vio的新的信號toggle_vio。

圖4

4

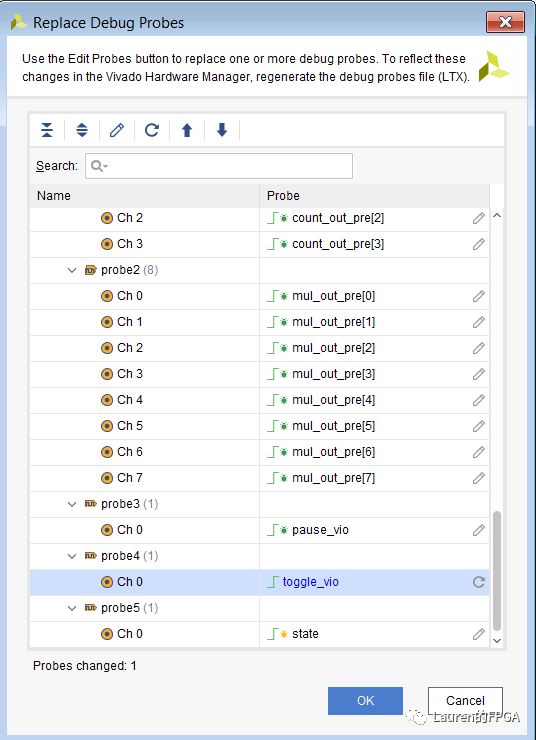

第4步:替換完成,可觀察到reset_vio被toggle_vio替換。如圖5所示。

圖5

5

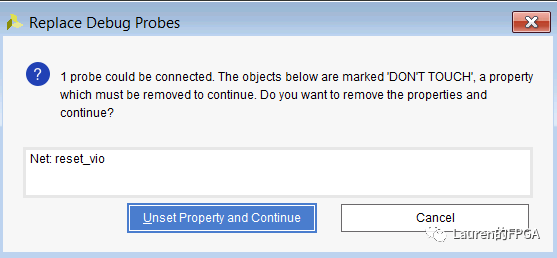

第5步:如果待測信號被施加了DONT_TOUCH屬性,會彈出如圖6所示的界面,選擇Unset Property and Continue。

圖6

6

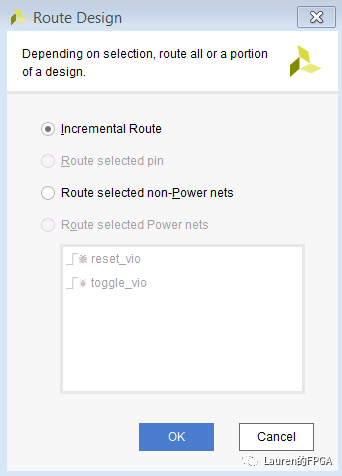

第7步:在ECO Navigator中選擇Route Degisn,會顯示如圖7所示界面,選擇Incremental Route。因為替換過程并沒有改變布局,所以只需增量布線即可。

圖7

7

第7步:布線之后通過report_route_status可查看布線狀態,如圖8所示。

圖8

8

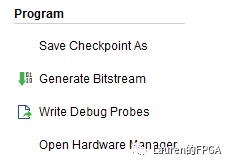

第8步:在ECO Navigator下的Program,選擇Save Checkpoint As可生成更新后的dcp,選擇Generate Bitstream可生成新的bit文件,選擇Write Debug Probes可生成新的.ltx文件。注意替換待測信號之后,一定要重新生成.ltx文件。

圖9

結論采用ECO方式替換待測信號是省時高效的,因為直接在原有布線網表的基礎上進行操作,不必重新布局,只需增量布線,這也可進一步保證布線結果的一致性。

-

信號

+關注

關注

11文章

2790瀏覽量

76730 -

Setup

+關注

關注

0文章

30瀏覽量

11987

原文標題:替換Debug Probes其實很簡單

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

HarmonyOS NEXT應用元服務開發控件位置調整場景與重新設置新焦點位置的場景

關于重新設置PANID

請問stm32在程序中重新配置RTC應如何實現?

一種基于滑模觀測器的電流偏差解耦控制方法

以編程方式重新設置Arduino

用成型濾波器組提高測距精度的一種方法

Chrome瀏覽器隱私設置重新設計后有什么不同

關于Vivado中三種操作Debug的方式

STM32 Debug無法添加斷點的解決方法

一種方法是回到綜合后的設計,通過Setup Debug重新設置待觀測信號

一種方法是回到綜合后的設計,通過Setup Debug重新設置待觀測信號

評論