本文將從小數鎖相環的需求,Delta-Sigma 小數鎖相環的邏輯以及Delta-Sigma的特性三方面展開。

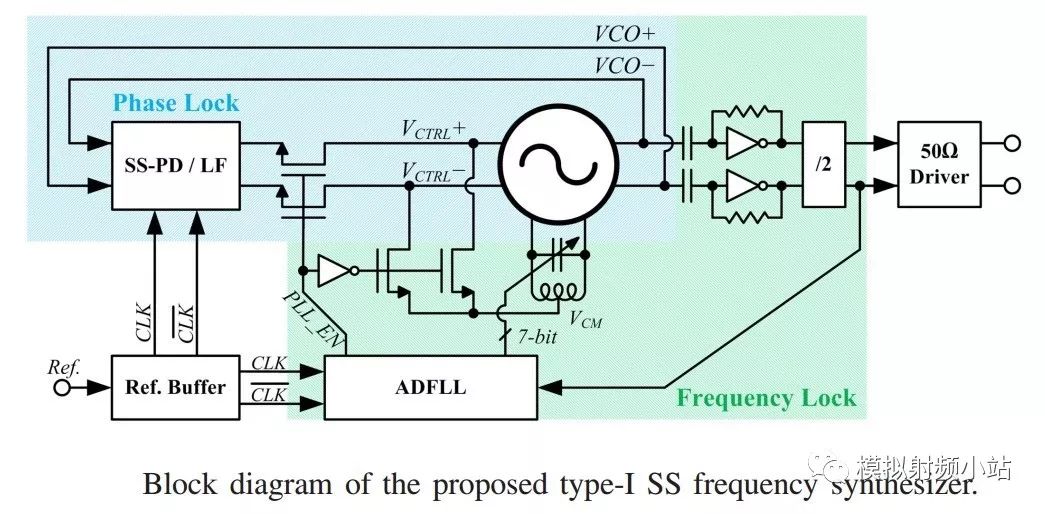

小數鎖相環相對于整數鎖相環來說可以極大地提高鑒頻鑒相器的頻率。這主要是由于系統而非器件水平的限制,因為小數分頻的引入使得在較高頻率鑒頻鑒相器情況下也可以獲得很小的輸出信號頻率步進。提高了鑒頻鑒相器的頻率帶來的好處是巨大的。主要體現的可以獲得更大的帶寬以縮短環路鎖定時間和減小輸出信號相位噪聲上。如果認真思考過鎖相環系統傳輸函數就知道反饋分頻系數的減小可以全方位地減小參考,VCO和電路噪聲對輸出信號相躁的貢獻(可以參見PLL系列之二當中的系統函數)。正是基于這個系統函數的特點,才想出了以混頻器代替反饋分頻器和現在學術界很熱門的sub-sampling(欠采樣)(近年來多篇sub-samplingPLL 發表在IC界最高水平的JSSC上)等方式來優化輸出的相躁。下圖是SS-PLL的一個例子:

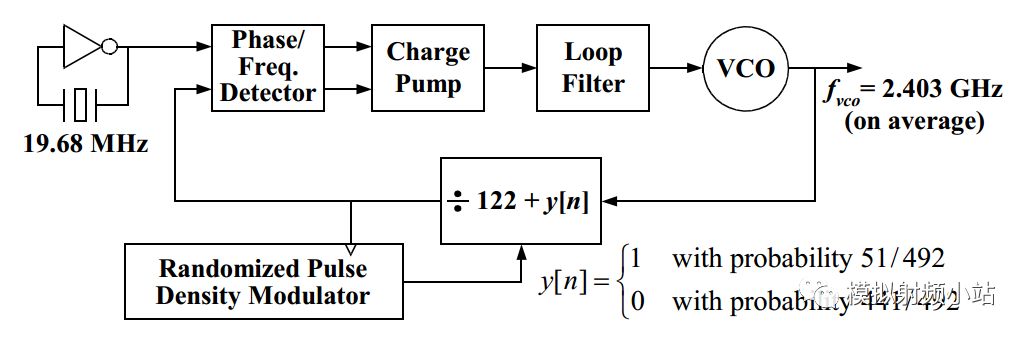

小數鎖相環當中很重要的是小數分頻器的實現,小數分頻器有多重實現方式,近幾年工業界或學術界研究比較多的是Phase-interpolator。后面有機會將另篇做介紹。在此還是介紹下傳統的N/N+1雙系數法,Delta-Sigma調制器也主要是跟這種方式結合在一起。舉一個簡單的例子,比方說我想獲得10.1的頻率,那么我一個采用9次10分頻和1次11分頻再通過平均來實現10.1的分頻,怎么實現平均以及為什么可以通過平均的方式來實現?還是要回到PLL傳輸函數上來,正是由于環路對分頻器來說是低通的特性使得這種方案跟PLL很好地結合。但事情并沒有就此結束,如果我每次都是采用固定的先9次10分頻再一個11分頻的方式,會導致兩個問題。一方面是在時間軸內不夠平均,另一方面是存在周期性。以10次為輪回的循環,這將使得輸出信號產生固定頻率的雜散(Spur)。為了抑制這個spur就必須將整個環路帶寬設置的很低。這將使得鎖定時間加長同時失去了根據系統不同部位噪聲水平來調節環路帶寬優化相躁的自由度,這些都不是我們期望的。為了解決這個問題我們引入隨機序列調制器,也就是說讓10和11分頻出現的時間點不規則。如下圖所示的系統框圖:

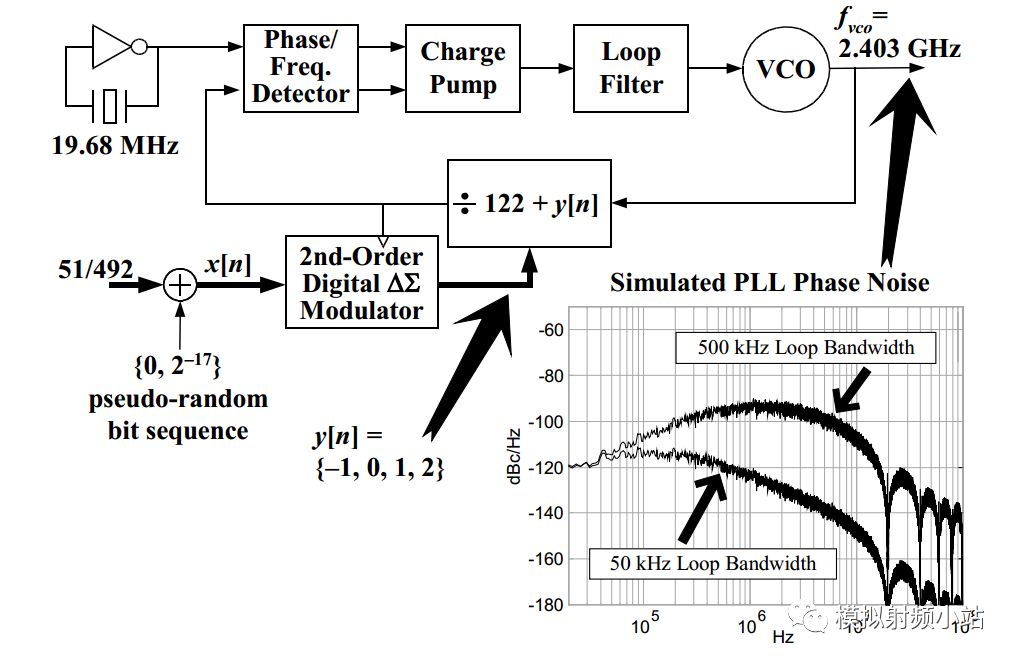

這解決了固定spur的問題,但在帶內依然引入了白噪聲使得輸出相躁惡化。為了減小白噪聲,又引入了Delta-Sigma調制器。基于Delta-sigma調制器的鎖相環系統框圖如下:

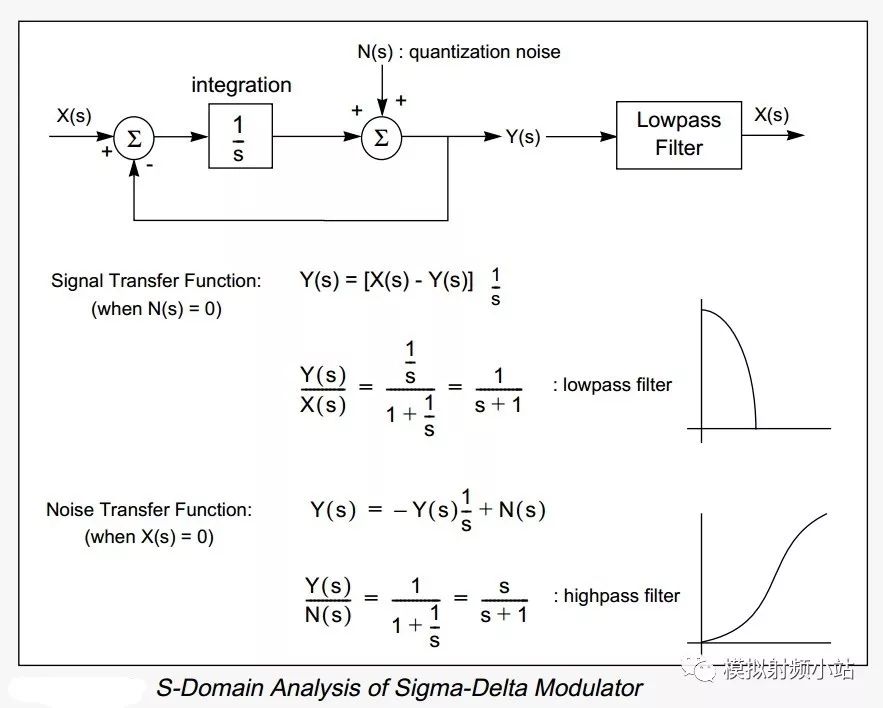

Delta-Sigma調制器的特點就是在于其對信號本身和噪聲有不同的特性,將噪聲推到帶寬。Delta-Sigma的S域系統和頻響特性如下圖:

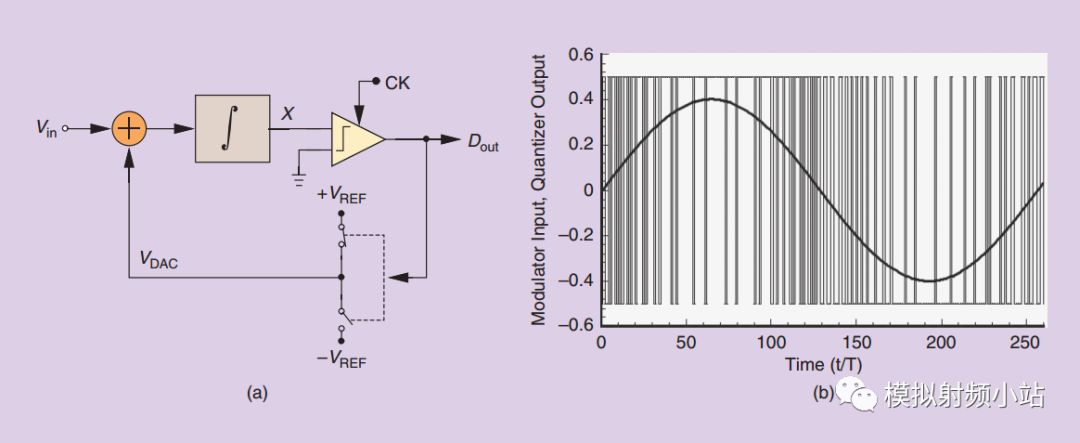

從上圖可以看到整個系統對輸入信號表現為低通,對噪聲表現為高通,也就是壓制了低頻段噪聲。同時上圖的機智在于并沒有給出量化器的精度表達了量化誤差。這也就鮮明地給出了1bit和多bit量化器系統的區別僅在于多bit量化器可以減小噪聲的絕對值。下圖為最簡單的一階一比特量化Delta-Sigma的結構圖和輸入輸出信號時域圖:

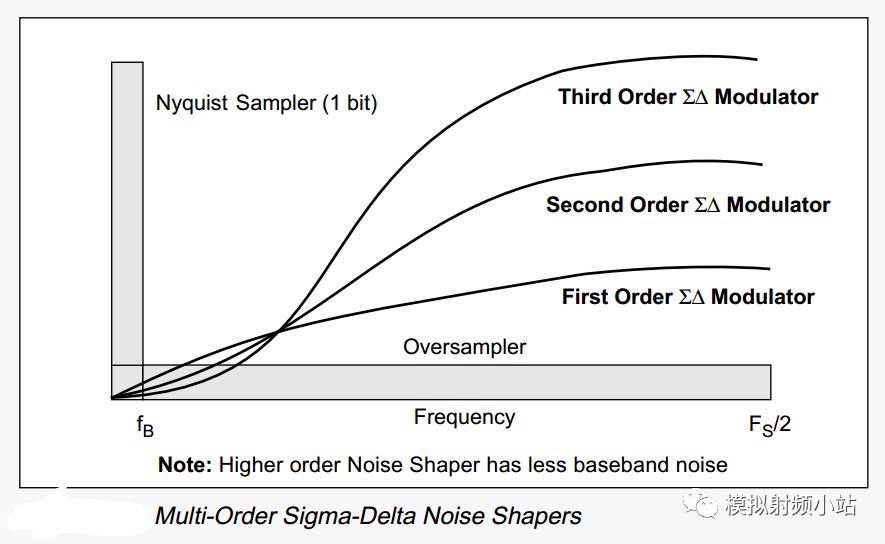

同時我們也可以通過采用更高階的Delta-Sigma調制器或獲得對低頻段噪聲更強的壓制。高階調制器有多重方式,最簡單的方式是采用多個一階調制器進行級聯。不同階數調制器對噪聲的頻響特性下圖。

至此我么就討論完了Delta-Sigma 小數鎖相環。但值得注意的是這次所討論的小數分頻是用在反饋路徑的分頻,也就是說是閉環內的分頻器。這是Delta-Sigma噪聲整形技術的局限。推出可以使用在VCO之后輸出級的開環小數分頻技術將對工業界具有重要意義。好消息是siliconlabs 公司在這方面已經有了很成熟的產品。其時鐘芯片的輸出級分頻也可以支持任意小數分頻,也就意味著同一個VCO可以支持多個時鐘域信號的輸出,極大地提升了時鐘芯片的靈活性。同時能夠獲得在12K~20MHz積分范圍內jitter小于100fs。

-

鎖相環

+關注

關注

35文章

597瀏覽量

88524

原文標題:Delta-Sigma小數鎖相環解說

文章出處:【微信號:gh_025d37bb233e,微信公眾號:模擬射頻小站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

RZ MPU Delta-sigma的工作原理 Delta-Sigma的應用簡介

鎖相環的原理,特性與分析

基于0.35μm工藝的Delta-Sigma ADC實現

求教delta-sigma調制的FPGA實現原理啊。

請問delta-sigma調制的FPGA實現原理是什么?

什么是Delta-Sigma轉換器?ADS1232特點及應用是什么?

delta-sigma調制過后的高頻噪聲是怎么去掉的?

AMC1203 (Isolated Delta-Sigma

Delta-Sigma轉換器的原理和應用

Accounting for delay from multiple sources in delta-sigma ADCs

評論