開關電源設計中,我們常常使用到一個電阻串聯一個電容構成的RC電路, RC電路性能會直接影響到產品性能和穩定性。本文將為大家介紹一種既能降低開關管損耗,且可降低變壓器的漏感和尖峰電壓的RC電路。

高頻開關電源在開關管關斷時,電壓和電流的重疊引起的損耗是開關電源損耗的主要部分,同時,由于電路中存在寄生電感和寄生電容,在功率開關管關斷時,電路中也會出現過電壓并且產生振蕩。如果尖峰電壓過高,就會損壞開關管。同時,振蕩的存在也會使輸出紋波增大。為了降低關斷損耗和尖峰電壓,需要在開關管兩端并聯RC緩沖電路以改善電路的性能。

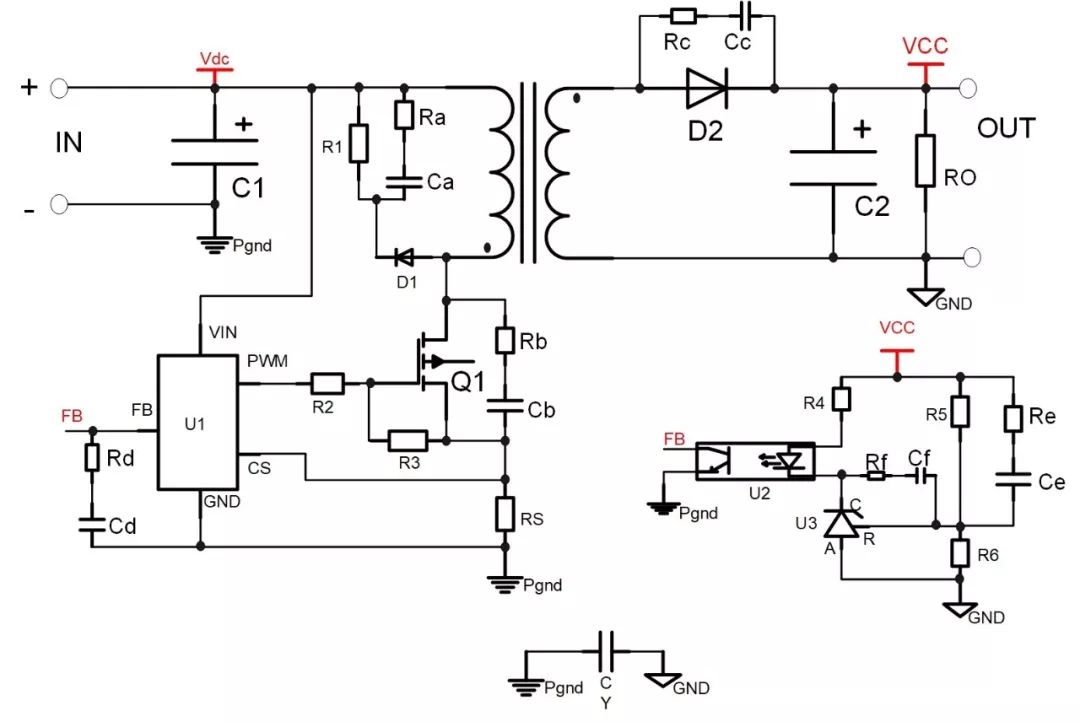

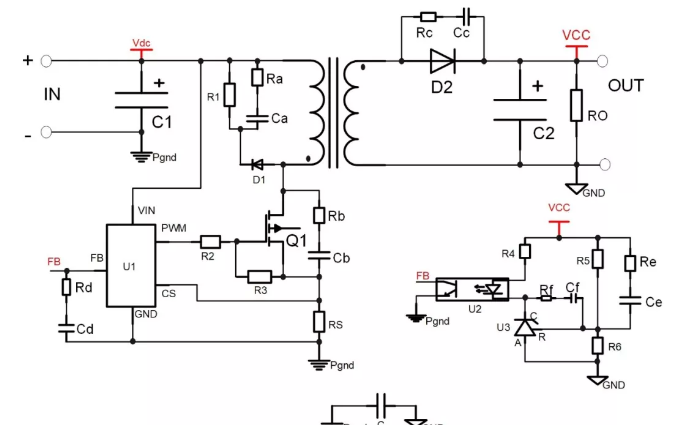

圖1

圖1所示的是一個簡單的反激式開關電源電路,從圖中可以看出RC電路在圖中的出現過6次從RaCa—RfCf,每個RC電路的位置不同,作用也不一樣。本文介紹的是圖1中RbCb,RcCc構成的RC吸收電路。這兩個RC電路在圖中主要作用是:

減少導通或關斷損耗;

降低電壓或電流尖峰;

可以間接的改善EMI特性。

在設計RC吸收電路時,我們必須了解整個電源網絡的幾個重要參數,比如輸入電壓、輸入電流、尖峰電壓、尖峰電流等。在圖1所示當Q1關斷時,源極電壓開始上升到2Vdc,而電容Cb限制了源極(D)電壓的上升速度,同時減小了上升電壓和下降電流的重疊,從而減低了開關管Q1的損耗。而在下次開關關斷之前,Cb必須將已經充滿的電壓放完,放電路徑為Cb、Rb、Q1。

圖2開關管源極(D)的Vds電壓波形

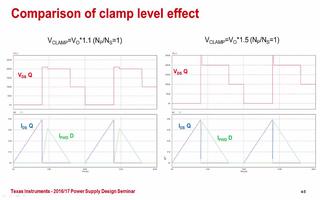

圖2-A表示的是開關管Q1沒有加RC吸收電路的Vds電壓波形,圖中明顯的看出,當開關管Q1斷開時,Vds電壓迅速上升至最高點,而后伴隨這震蕩下跌,震蕩頻率為20MHZ。

圖2-B表示的是開關管上加了RC吸收電路的Vds電壓波形,相對與圖2-A,在加了RC吸收電路后,開關管斷開瞬間,Vds電壓上升比較平緩,且在上升到最高電壓跌落時不會產生高頻震蕩,EMI特性也會偏好。

在感性負載中,開關器件關斷的瞬間,如果此時感性負載的磁通不為零,根據愣次定律便會產生一個自感電動勢,對外界辭放磁場儲能,為簡單起見,一般都采用RC吸收回路,將這部份能量以熱能的方式消耗掉。

設計RC吸收回路參數,需要先確定磁場儲能的大小,在反激變壓器中,磁場儲能由兩部份辭放,其中大部份是通過互感向二次側提供能量,只有漏感部份要通過RC回路處理,需要測量勵磁電感,互感及漏感值,再求得RC回路的初始電流值。

R的取值,以開關所能承受的瞬時反壓,比初始電流值;此值過小則動態功耗過大,引值過大則達不到保護開關的作用;

C的取值,則需要滿足在鉗位電平下能夠儲存磁能的一半,且滿足一定的dV/dt,C關斷緩沖,R開通限流,電阻的阻值基本可以按照:

R=(sqrt(Llk/Cj))/n 這個公式計算,功率根據實際情況選擇,C一般都在102——103之間選擇,選C時在考慮吸收效果的同時還需考慮EMI的相位和后面輸出電容的紋波電流應力,則有:

C=(Ip*Tf)/(2*2*Vdc)

Ip:峰值電流

Tf:集電極電流從初始值下降到零的時間

Vdc:輸入的直流電壓

R=Ton(min)/(3C)

Ton(min):開關管最小的導通時間

總結

根據以上給出的公式,可以很方便地選擇出合適的RC吸收電路。但在設計時,應該根據整個電源設計的性能指標,通過實際調試才能得到真正合適的參數。有時候,為了達到系統的性能指標,犧牲一定的效率也是必要的。總之,在設計RC吸收電路參數時,必須綜合考慮性能和效率,最終選擇合適的RC參數。

ZLG致遠電子自主研發、生產的隔離電源模塊已有近20年的行業積累,目前產品具有寬輸入電壓范圍,隔離1000VDC、1500VDC、3000VDC及6000VDC等多個系列,封裝形式多樣,兼容國際標準的SIP、DIP等封裝。

同時,ZLG致遠電子為保證電源產品性能建設了行業內一流的測試實驗室,配備最先進、齊全的測試設備,全系列隔離DC-DC電源通過完整的EMC測試,靜電抗擾度高達4KV、浪涌抗擾度高達2KV,可應用于絕大部分復雜惡劣的工業現場,為用戶提供穩定、可靠的電源隔離解決方案。

-

開關電源

+關注

關注

6459文章

8328瀏覽量

481756 -

寄生電感

+關注

關注

1文章

155瀏覽量

14595 -

RC電路

+關注

關注

2文章

162瀏覽量

30247

原文標題:電源設計經驗:RC吸收電路篇

文章出處:【微信號:ZLG_zhiyuan,微信公眾號:ZLG致遠電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一種既能降低開關管損耗,且可降低變壓器的漏感和尖峰電壓的RC電路

一種既能降低開關管損耗,且可降低變壓器的漏感和尖峰電壓的RC電路

評論