隨著它們承載的器件的復雜性提高,PCB設計也變得越來越復雜。相當長一段時間以來,電路設計工程師一直相安無事地獨立進行自己的設計,然后將完成的電路圖設計轉給PCB設計工程師,PCB設計工程師獨立完整自己的工作后,將Gerber文件再轉給PCB制造廠。電路設計工程師、PCB設計工程師和PCB制造廠的工作都是相互隔離的,少有溝通。

隨著采用大型BGA封裝的可編程器件的應用不斷普及,以及高密度互連(HDI)、時序關鍵的差分對信令的廣泛應用,現在再采用這樣一種相互隔離的PCB設計方式將帶來災難性后果,而并行開發流程允許多個開發過程同步進行,有助于確保設計成功,避免延誤、額外開銷以及返工。本文總結了并行PCB設計各個階段的關鍵準則。

PCB設計的第一步是在概念階段。這時,電路設計工程師應該與PCB設計工程師一起進行技術評估。這個評估應考慮這么一些問題:

1. 采用哪些器件?2. 器件選用哪種封裝?管腳數多少?管腳配置怎樣?3. 基于成本和性能的權衡,采用幾層PCB?4. 時鐘頻率和信令速度等參數的目標值是什么?

此外,設計工程師還應考慮總線架構、是采用并行還是串行連接等因素,以及阻抗匹配策略。阻抗不匹配時會出現反射、振鈴及其它不期望的干擾。

協同工作

PCB設計的這些考慮提出了成功PCB設計中的一個關鍵問題是溝通,因為PCB設計不再是一個人的工作,而是不同組的工程師之間的團隊合作。溝通這一主旨貫穿整個PCB設計流程的始終,電路設計團隊必須清楚地就其設計意圖與PCB設計團隊進行溝通,他們還必須在清楚了解其PCB設計工具能干什么、不能做什么的前提下參與到該過程中。

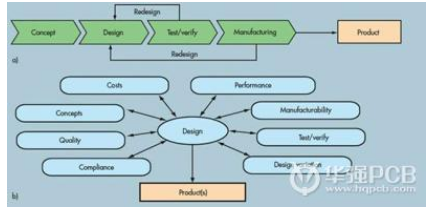

隨著PCB布線的復雜性日益增加,信號速率日益提高,協同的PCB設計方式可比傳統的串行流程得到更好效果(圖1)。將對元件的研究和選擇與整個設計流程的其它部分隔離開,以及將原理圖輸入、仿真與布局布線階段也獨立出來一直是常用手法。因此,設計工程師最好選擇便于分享數據的工具和流程,這是在分布在不同地方的設計團隊能利用并行工作的好處并縮短整個設計周期的唯一途徑。

圖1:(a) 傳統PCB串行開發流程的設計周期長,信息共享有限,而成本持續上升;(b) 并行開發流程允許多個開發程同步進行,有助于確保設計成功,避免延誤、額外開銷以及返工

設計創建

在設計創建階段,工程師將最終確定好器件并為其生成各種庫,這樣反過來又加快了原理圖輸入。在該階段,設計工程師評估和選擇構造模塊,并可以登陸制造商的網站搜索數據表和規范。完成這項工作的一個更好方法,是直接在原理圖輸入過程中選擇器件。通過以這種方式來實現原理圖輸入,這個流程可被用作為一種試驗方法。 在原理圖輸入過程中,設計工程師能迅速添加、刪減或變更器件(甚至整個設計結構)的能力很重要。例如,為手機開發高頻濾波器的設計工程師應在原理圖輸入時,通過對不同容抗和感抗值進行試驗來設定通帶及其它濾波器參數。

在創建原理圖時,PCB設計工具也在后臺為該電路生成一個網絡表。網絡表描述了電路的器件如何連接以及后續放置和布線工具如何將其用于PCB布局布線的信息。此時,設計工程師將為諸如FPGA或其它可編程器件等所謂的“大元件”創立符號和物理管腳布局布線圖。也是在這個時候,設計約束被捕獲,這是一個需要審慎思考的關鍵步驟,特別是對后續流程而言。

對于目前的PCB設計來說,最好一切都按規矩辦。過去是受到制造問題的制約,而現在當工程師努力減小PCB的體積且仍使其具有可制造性時,一切都要受到復雜約束的限制。雖然設計需求也許會導致大量約束,但不讓設計被過分約束也很重要。與簡單地用約束設計相比,更多地借鑒仿真和分析是更明智的方法。

在設計創建過程中,工程師需留意也許會在后續流程中出現的信號完整性問題。最好在設計輸入階段及PCB布局布線階段就將信號完整性問題考慮進去,當然設計流程必須支持這種方式,因為無法在設計輸入階段解阻抗失配問題。

仿真是關鍵

電路一旦設計完成并繪制好原理圖后,接著就該進行功能驗證,它通常采用仿真工具完成。仿真的目的不是取代物理原型生成,而為了避免反復生成原型,因為仿真使設計工程師能發現一般要等到原型生成才能發現的設計缺陷。

在仿真過程中,可以嘗試各種設計拓撲,并用不同廠商的器件進行替代,來檢驗它們對電路性能的影響。但在仿真時,伴隨模型的可用性及有效性的問題層出不窮。目前所有常用的PCB設計工具包都帶有昂貴的模型庫,但可能不止一次會出現某個特定器件不在庫內的情況。但器件供應商一般會通過在其網站上推出Spice模型來解決此問題,因此通過器件供應商網站查找它們是個好主意。

迂回布線的限制

但基于Spice的仿真也存在局限性,它能生成理想化從而不一定代表真實條件的仿真信號。真實信號可能有改變真實性的噪聲和相移。

美國國家儀器公司(NI)的PCB設計流程包括虛擬儀器,可將該儀器與NI的許多PXI儀器一起使用,以生成保留隨帶的非線性成分的真實信號。這些信號能以固有的文件格式來捕獲,以用在驗證電路行為的Spice仿真上。另外,虛擬原型可提供對器件選擇的反饋。

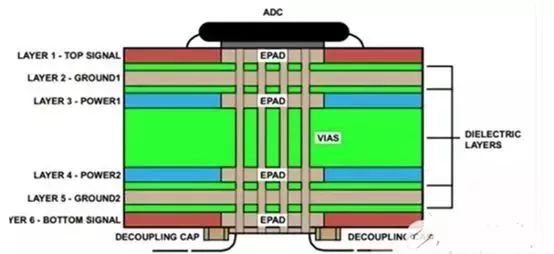

系統級的仿真也很關鍵,它不僅僅是對一個通過PCB的信號實施建模,還必須檢查信號在器件內甚或通過多個板卡時都有什么變化。數Gb的信令速率是使情況更復雜的另一個因素。串行總線架構比并行總線架構更受青睞,這就要求PCB設計工程師對損耗、耦合傳輸線及詳盡的過孔模型實施仿真。

物理實現

當通過仿真剔除性能問題后,下一步是對電路進行布局布線以生成物理原型。布局布線要確保電路性能滿足設計規范要求,并保證板卡外形匹配設計形態參數。這時與機械工程師一起合作將非常必要。

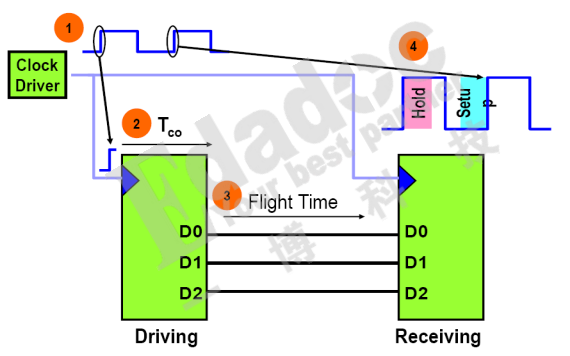

在布局布線階段,由原理圖定義的器件間的互連可由任一家EDA供應商提供的布局布線和布線工具實現。所有這些工具都將提供一定程度的自動布局布線功能,但它是一把雙刃劍。設計工程師需要判斷何時進行手工布線,何時采用自動布線。如果要放置一個關鍵元件,或者必須將一個連接器放在PCB邊緣上,就不要采用自動布局布線功能。欣慰的是,在進行布局布線時,可以對信號完整性問題做些前瞻性考慮。這是個必須認真對待的階段。一般的經驗是,如果信號到達目的地所用的時間超過轉換時間的1/3,則在該路徑上可能存在信號完整性問題。

設計約束

PCB布局布線存在許多挑戰,其中最主要挑戰是確保滿足約束條件。這些約束被用來解決信號完整性問題、可制造性問題、電磁干擾、熱效應或上述這些問題的組合。

除設計約束外,許多與目前特定器件技術相關的因素使PCB布局布線更加復雜,例如板載芯片(COB)等先進半導體封裝技術可令布線變得極其棘手。目前的高密度封裝可以容下2,000多個管腳,管腳間距不到0.65mm。這種封裝將給管理I/O和信號速度帶來很大困難,對這種封裝進行迂回布線(Escape Routing)也是一個高技巧工作。

對可編程邏輯器件進行PCB布局布線是另一個挑戰。一些高端PCB設計工具包能與FPGA供應商的設計工具緊密鏈接,并可用來完成FPGA和PCB本身的集成設計。

以前,大型FPGA的管腳配置一般由FPGA設 計工程師完成,但在進行配設時并沒對PCB布局布線有太多考慮。人們現在意識到,帶可編程I/O的FPGA是走線進或出的源頭,改變FPGA以迎合PCB布局布線比改變PCB來匹配FPGA的I/O設置要容易地多。

最后檢查

在將PCB版圖拿去制造前的最后步驟是最終檢查。必須檢查信號完整性和時序以確保信號能及時到達目的地并具有充分的品質保證。設計約束沖突將在此時表露出來,對此要進行權衡。

在該階段,最大挑戰之一是盡量將這些設計流程的最后驗證步驟提前,具有更好的約束是實現這種要求的一個關鍵。若在創建設計過程中,在確定約束的同時還可進行分析,則改善約束條件的質量。

PCB設計最后必須生成制造數據,包括全部與生產、組裝及測試相關的文檔。在整個設計過程中,設計團隊成員與制造廠家之間必須都有充分溝通,以了解制造商的技術能力和限制。另外,必須對制造數據進行驗證以使設計工程師有最后機會發現錯誤。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

602986 -

pcb

+關注

關注

4319文章

23080瀏覽量

397494 -

BGA

+關注

關注

4文章

543瀏覽量

46800

原文標題:并行PCB設計的關鍵準則

文章出處:【微信號:Mouser-Community,微信公眾號:貿澤電子設計圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB設計有哪些誤區PCB設計的十大誤區下部分內有上部分鏈接

電路設計工程師與PCB設計工程師在進行技術評估時應考慮哪些問題

高頻PCB設計中,工程師需考慮四個方面帶來的干擾問題并給解決方案

可以優化ESD防護的PCB設計準則

并行PCB設計各個階段的關鍵準則資料下載

ADC的PCB設計,告訴你四個關鍵技巧!

PCB設計中的四個小妙招

并行PCB設計有哪些關鍵準則和評估應考慮的四個問題說明

并行PCB設計有哪些關鍵準則和評估應考慮的四個問題說明

評論