PS/PL Interfaces

Zynq在PS和PL之間有9個AXI接口。 在PL方面,有4x AXI Master HP(高性能)端口,2x AXI GP(通用)端口,2x AXI Slave GP端口和1x AXI Master ACP端口。 PS中還有連接到PL的GPIO控制器。

有四個pynq類用于管理Zynq PS(包括PS DRAM)和PL接口之間的數(shù)據(jù)移動。

1.GPIO - 通用輸入/輸出

2.MMIO - 內(nèi)存映射IO

3.Xlnk - 內(nèi)存分配

4.DMA - 直接內(nèi)存訪問

使用的類取決于IP連接的Zynq PS接口以及IP的接口。

在PYNQ上運行的Python代碼可以使IP通過AXI Slave訪問連接到GP端口。 MMIO可用于執(zhí)行此操作。

連接到AXI Master端口的IP不受PS的直接控制。 AXI Master端口允許IP直接訪問DRAM。在執(zhí)行此操作之前,應分配內(nèi)存以供IP使用。 Xlnk類可用于執(zhí)行此操作。對于PS DRAM和IP之間的更高性能數(shù)據(jù)傳輸,可以使用DMA。 PYNQ提供DMA類。

在設(shè)計自己的 overlay時,您需要考慮所需的IP類型以及它如何連接到PS。然后,您應該能夠確定使用IP所需的類。

PS GPIO

從Zynq PS到PL有64個GPIO(線路)。

來自PS的PS GPIO線可以作為非常簡單的方式用來進行PS和PL之間通信。 例如,GPIO可用作復位或中斷的控制信號。

IP連接到GPIO,不必映射到系統(tǒng)存儲器映射。

有關(guān)使用PS GPIO的更多信息,請參閱PS GPIO部分。

MMIO

連接到AXI Slave GP端口的任何IP都將映射到系統(tǒng)存儲器映射中。 MMIO可用于讀/寫內(nèi)存映射位置。 MMIO讀或?qū)懨钍菍?2位數(shù)據(jù)傳輸?shù)酱鎯ζ魑恢没驈拇鎯ζ魑恢脗鬏?2位數(shù)據(jù)的單個事務(wù)。 由于不支持突發(fā)指令,MMIO最適合從IP連接到AXI Slave GP端口讀取和寫入少量數(shù)據(jù)。

有關(guān)使用MMIO的更多信息,請參閱MMIO部分。

Xlnk

必須先分配內(nèi)存,然后才能通過IP訪問內(nèi)存。 Xlnk允許分配內(nèi)存緩沖區(qū)。 Xlnk分配一個連續(xù)的內(nèi)存緩沖區(qū),允許在PS和PL之間有效地傳輸數(shù)據(jù)。 Python或其他代碼運行在PS端的Linux上,可以直接訪問內(nèi)存緩沖區(qū)。

當PYNQ運行Linux時,緩沖區(qū)將存在于Linux虛擬內(nèi)存中。 Zynq AXI Slave端口允許overlay中的 AXI-master IP訪問物理內(nèi)存。 Xlnk還可以提供指向緩沖區(qū)的物理內(nèi)存指針,該指針可以發(fā)送到overlay中的IP。 物理地址存儲在分配的內(nèi)存緩沖區(qū)實例的physical_address屬性中。 然后,overlay中的IP可以使用物理地址訪問同一緩沖區(qū)。

有關(guān)使用Xlnk的更多信息,請參閱Xlnk部分。

DMA

AXI stream接口通常用于高性能流應用。 AXI stream可以通過DMA與Zynq AXI HP端口一起使用。

pynq DMA類支持AXI直接內(nèi)存訪問IP。 這允許數(shù)據(jù)從DRAM讀取,并發(fā)送到AXI stream,或從stream接收并寫入DRAM。

有關(guān)使用DMA的更多信息,請參見DMA部分。

Interrupt

有一些專用中斷與python環(huán)境中的asyncio事件相關(guān)聯(lián)。 要集成到PYNQ框架中,必須將專用中斷連接到AXI中斷控制器,該控制器又連接到PS的第一個中斷線。 如果需要超過32個中斷,則可以級聯(lián)AXI中斷控制器。 對于不受PYNQ直接控制的IP,例如SDSoC加速器,這種安排使其他中斷空閑。

中斷由Interrupt類管理,實現(xiàn)基于asyncio構(gòu)建,asyncio是Python標準庫的一部分。

-

接口

+關(guān)注

關(guān)注

33文章

8961瀏覽量

153273 -

Xilinx

+關(guān)注

關(guān)注

73文章

2183瀏覽量

124464

原文標題:泵的基礎(chǔ)知識與選型原則、經(jīng)驗

文章出處:【微信號:gongkongworld,微信公眾號:工控資料窩】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

PYNQ項目——Pynq開發(fā)板啟動實驗

PYNQ案例(一):ZYNQ的PL與PS開發(fā)

如何為自己的ZYNQ板卡創(chuàng)建Pynq鏡像

【PYNQ-Z2申請】基于PYNQ的神經(jīng)網(wǎng)絡(luò)自動駕駛小車

【PYNQ-Z2試用體驗】玩轉(zhuǎn)PYNQ系列:一、板卡簡介與資源整理

【PYNQ-Z2試用體驗】PYNQ-Z2開箱上手以及基本的功能驗證(年底比較忙,今天才傳的報告)

【PYNQ-Z2試用體驗】玩轉(zhuǎn)PYNQ系列:三、PYNQ數(shù)字圖像處理之圖像采集

請問USB接口的四個引腳到底分別是什么?

PYNQ開源方案

【KV260視覺入門套件試用體驗】Zynq超強輔助-PYNQ配置,并使用XVC(Xilinx Virtual Cable)調(diào)試FPGA邏輯

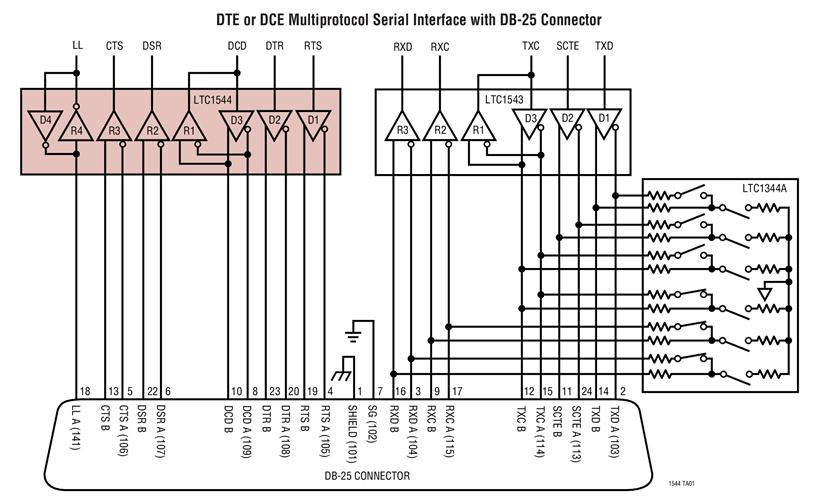

有四個驅(qū)動器/四個接收器的多協(xié)議收發(fā)器LTC?1544

如何運行UltraScale PCI Express解決方案的四個主要數(shù)據(jù)接口

示波器經(jīng)常說“四個部分”是哪四個部分?

耐輻射V類,四個2輸入正-非門數(shù)據(jù)表

評論