1. 快速學(xué)習(xí)的能力

作為一個通信汪,我就以通信設(shè)備方面來說吧!

一方面,通信技術(shù),標(biāo)準(zhǔn),芯片更新的太快了,快到你根本來不及系統(tǒng)的了解它,只能通過特定的項目,需求進(jìn)行了解;另一方面對于公司來說,需要做的硬件產(chǎn)品也是變化很快,客戶需要T1, E1, PDH, SDH,Ethernet, VoIP, Switch, Router, 沒有人是什么都懂的,都需要能夠結(jié)合客戶的需求,選擇的芯片方案進(jìn)行詳細(xì)了解,尤其對于接口協(xié)議和電氣特性。

2. 對協(xié)議和標(biāo)準(zhǔn)的理解

通信設(shè)備,顧名思義,就是用來實現(xiàn)多種通信協(xié)議(比如T1, E1, V.35,PDH, SDH/SONET, ATM, USB, VoIP, WiFi, Ethernet, TCP/IP,RS232等等常用協(xié)議)實現(xiàn)通信的設(shè)備,各種電路,PCB板,電源都是為了通信協(xié)議服務(wù)的。

通信協(xié)議一般都是由芯片實現(xiàn),要么是成熟的 ASIC,要么是自己開發(fā)的FPGA/CPLD,芯片工程師或者FPGA工程師比硬件工程師跟靠近通信協(xié)議,他們需要對于通信協(xié)議理解很透徹,實現(xiàn)各種邏輯上的狀態(tài)機(jī)以及滿足協(xié)議規(guī)定的電氣參數(shù)標(biāo)準(zhǔn)。按照OSI的七層模型,硬件工程師尤其需要專注于一層物理層和二層數(shù)據(jù)鏈路層的協(xié)議標(biāo)準(zhǔn),以 Ethernet距離,物理層是由PHY/transceiver芯片完成,數(shù)據(jù)鏈路層是由MAC/switch 芯片完成,對于從事Ethernet相關(guān)開發(fā)的硬件工程師來說,需要對于PHY和Switch芯片理解透徹,從編碼方式,電氣參數(shù),眼圖標(biāo)準(zhǔn),模板,信號頻率到幀格式,轉(zhuǎn)發(fā)處理邏輯,VLAN等等。

3. 寫文檔的能力

誠如軟件設(shè)計一樣,好的軟件設(shè)計需要好的設(shè)計文檔,明確需求,實現(xiàn)什么功能,達(dá)到什么驗收標(biāo)準(zhǔn),隨著芯片集成度的增加,接口速率的提高,單板復(fù)雜度的提高,硬件設(shè)計也越來越復(fù)雜以及對應(yīng)熱穩(wěn)定性,可靠性,電磁兼容,環(huán)境保護(hù)的要求,已經(jīng)不是通過小米加步木。倉的游擊戰(zhàn)可以解決了,每一個硬件項目都是一場戰(zhàn)爭,都需要好好的規(guī)劃,好好的分析,這就需要好好做文檔。

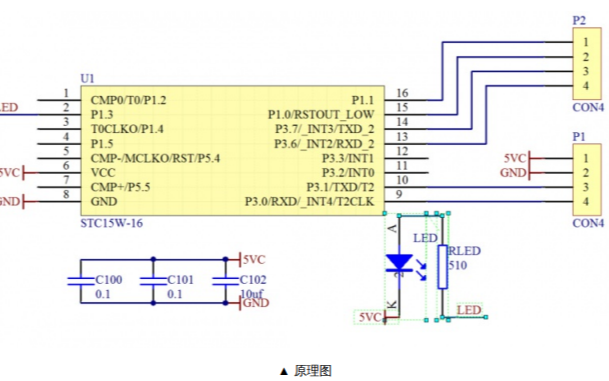

對于硬件工程師來說,最重要的文檔有兩個:一個是硬件設(shè)計規(guī)范(HDS : hardware design specification)和硬件測試報告(一般叫EVT:Engineering Validation& Test report或者DVT: Design Validation & Test report),對于HDS的要求是內(nèi)容詳實,明確,主芯片的選擇/硬件初始化,CPU的選擇和初始化,接口芯片的選擇/初始化/管理,各芯片之間連接關(guān)系框圖(Block Diagram),DRAM類型/大小/速度,F(xiàn)LASH類型/大小/速度,片選,中斷,GPIO的定義,復(fù)位邏輯和拓?fù)鋱D,時鐘/晶振選擇/拓?fù)洌琑TC的使用,內(nèi)存映射(Memory map)關(guān)系, I2C器件選擇/拓?fù)洌涌谄骷?線序定義,LED的大小/顏色/驅(qū)動,散熱片,風(fēng)扇,JTAG,電源拓?fù)?時序/電路等等。

好的硬件工程師無論是做的文檔還是報道都是令人一目了然,這個硬件系統(tǒng)需要用什么方案和電路,最后驗證測試的結(jié)果如何。內(nèi)容詳實,不遺漏各種接口/電路;簡單名了,不說廢話;圖文并茂,需要的時候一個時序圖,一個示波器抓圖就很能說明問題了。

4. 電路設(shè)計的能力

隨著芯片集成度的提高,硬件設(shè)計似乎變簡單了。首先是邏輯連接,其次考慮信號完整性需要的串行電阻選擇和并行電容選擇,電源濾波,退耦。

不過對于好的硬件工程師來說,簡單的邏輯連接(這個芯片的同樣總線的輸出接另一個芯片的輸入,等等),只是硬件設(shè)計的最基本技能,電路是芯片功能,通信協(xié)議和各種軟件的載體,沒有對電路的深入理解,根本談不上對硬件設(shè)計的深入理解,尤其對于芯片后面列的電氣性能參數(shù)或者離散器件各種參數(shù)的理解,胡亂亂接,可能在3.3V的總線上可以工作。

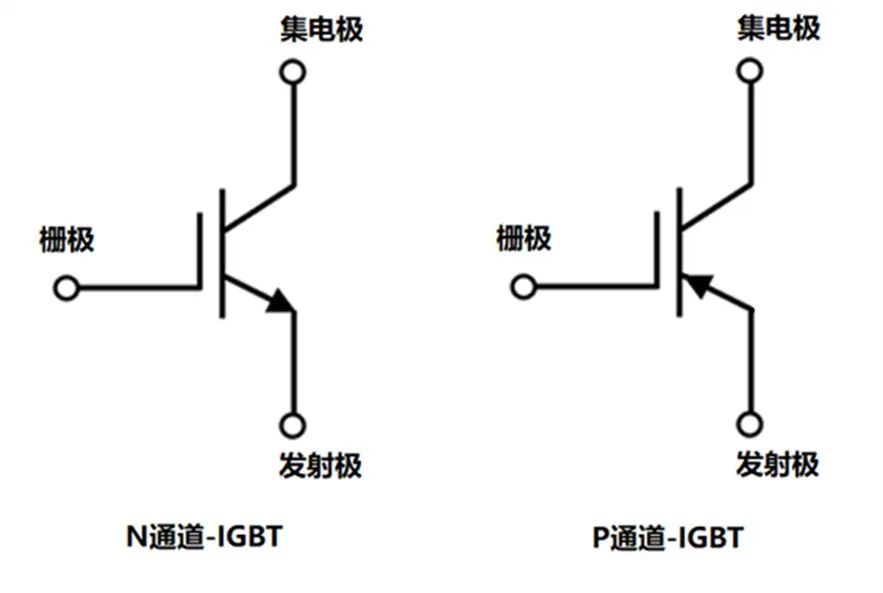

但是現(xiàn)在工作電壓已經(jīng)降到1V了,什么概念,信號線上的噪聲都已經(jīng)大到可以使采樣出現(xiàn)誤判了,隨著信號速率的提高和工作電壓的降低,數(shù)字信號已經(jīng)越來越模擬化了,這就需要對于PCB的阻抗,容抗,感抗,離散器件(電阻,電容,電感,二極管,三極管,MOSFET,變壓器等),ASIC的接口電氣參數(shù)深入了解,這都需要對電路原理,模擬電路甚至電磁場理論深入學(xué)習(xí),電路可以說是電磁場理論的子集,沒有電磁場理論的理解,根本談不上對于電容,電感,串?dāng)_,電磁輻射的理解。

5. 溝通和全局控制的能力

硬件工程師在一個硬件項目中,一般處于Team leader的作用,要對這個硬件項目全權(quán)負(fù)責(zé),需要協(xié)調(diào)好PCB工程師,結(jié)構(gòu)工程師,信號完整性工程師,電磁兼容工程師等各種資源,并與產(chǎn)品經(jīng)理,項目經(jīng)理,軟件工程師,生產(chǎn)工程師,采購工程師緊密配合,確保各個環(huán)節(jié)按部就班,需要對整個項目計劃了然于胸,各個子任務(wù)的發(fā)布時間,對于可能出現(xiàn)的技術(shù)難題和風(fēng)險的估計,控制。

-

芯片

+關(guān)注

關(guān)注

456文章

50965瀏覽量

424862 -

通信協(xié)議

+關(guān)注

關(guān)注

28文章

899瀏覽量

40339 -

通信設(shè)備

+關(guān)注

關(guān)注

3文章

339瀏覽量

32101

原文標(biāo)題:學(xué)會這5大技能,你就可以在工程圈混了!

文章出處:【微信號:elecfans,微信公眾號:電子發(fā)燒友網(wǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

一分鐘,就可以看出你的殺毒軟件行不行

然后彈出你設(shè)置的過孔,選擇就可以

解鎖了這些姿勢!你就可以嘿!嘿!嘿!

具備了這些特點(diǎn),你就可以大聲宣布我是一個編程老手了!

黑科技:要不了多久 ,你就可以用手勢操控家里的所有家電了!

電子工程師為什么要學(xué)會用FPGA 有什么好處?

【微信精選】學(xué)會這4大硬件加密方法,你就可以在單片機(jī)界混了!

華為推出一款快速充電電池,只需5分鐘就可以充滿50%電量

谷歌機(jī)器人不用干預(yù) 就可以自己學(xué)會走路

人臉識別耳機(jī):無需面對屏幕就可以向他人發(fā)送消息

如何讓STC單片機(jī)接上電就可以開始工作

為什么讓光線更彎就可以把電路傳輸速度提高千倍?資料下載

PLC控制伺服到底需要哪些信號就可以實現(xiàn)定位控制了?

學(xué)會這5大技能,你就可以在工程圈混了!

學(xué)會這5大技能,你就可以在工程圈混了!

評論