流水線設(shè)計(jì)

流水線概述

如下圖為工廠流水線,工廠流水線就是將一個(gè)工作(比如生產(chǎn)一個(gè)產(chǎn)品)分成多個(gè)細(xì)分工作,在生產(chǎn)流水線上由多個(gè)不同的人分步完成。這個(gè)待完成的產(chǎn)品在流水線上一級(jí)一級(jí)往下傳遞。

圖片來自網(wǎng)絡(luò)

比如完成一個(gè)產(chǎn)品,需要8道工序,每道工序需要10s,那么流水線啟動(dòng)后,不間斷工作的話,第一個(gè)產(chǎn)品雖然要80s才完成,但是接下來每10s就能產(chǎn)出一個(gè)產(chǎn)品。使得速度大大提高。當(dāng)然這也增加了人員等資源的付出。

對(duì)于電路的流水線設(shè)計(jì)思想與上述思想異曲同工,也是以付出增加資源消耗為代價(jià),去提高電路運(yùn)算速度。

流水線設(shè)計(jì)實(shí)例

這里以一個(gè)簡(jiǎn)單的8位無符號(hào)數(shù)全加器的設(shè)計(jì)為實(shí)例來進(jìn)行講解,實(shí)現(xiàn)

assign {c_out,data_out [7:0]} = a[7:0] + b[7:0] +c_in

c_out 為進(jìn)位位。

(源碼鏈接:https://pan.baidu.com/s/1-imO5A51dJ_pfWpRfOYcHg 提取碼:dx0k)

如果有數(shù)字電路常識(shí)的人都知道,利用一塊組合邏輯電路去做8位的加法,其速度肯定比做2位的加法慢。因此這里可以采用4級(jí)流水線設(shè)計(jì),每一級(jí)只做兩位的加法操作,當(dāng)流水線一啟動(dòng)后,除第一個(gè)加法運(yùn)算之外,后面每經(jīng)過一個(gè)2位加法器的延時(shí),就會(huì)得到一個(gè)結(jié)果。

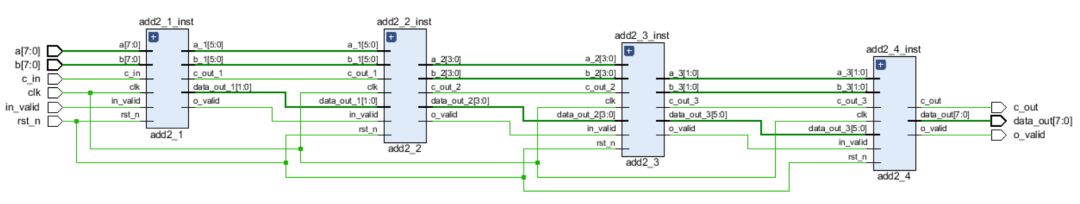

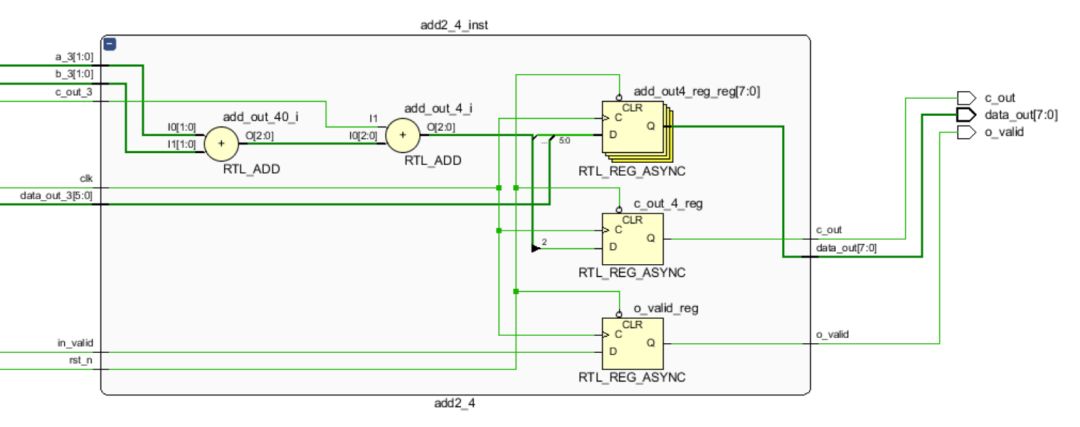

整體結(jié)構(gòu)如下,每一級(jí)通過in_valid,o_valid信號(hào)交互,分別代表每一級(jí)的輸入輸出有效信號(hào)。

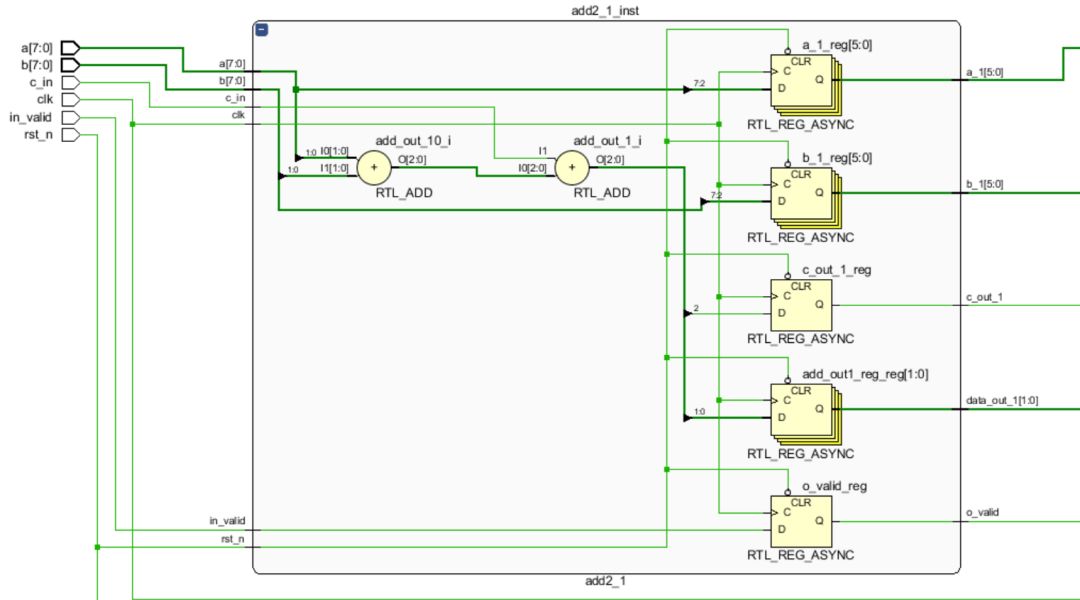

第一級(jí):做最低兩位與進(jìn)位位的加法操作,并將運(yùn)算結(jié)果和未做運(yùn)算的高六位傳給下一級(jí)。

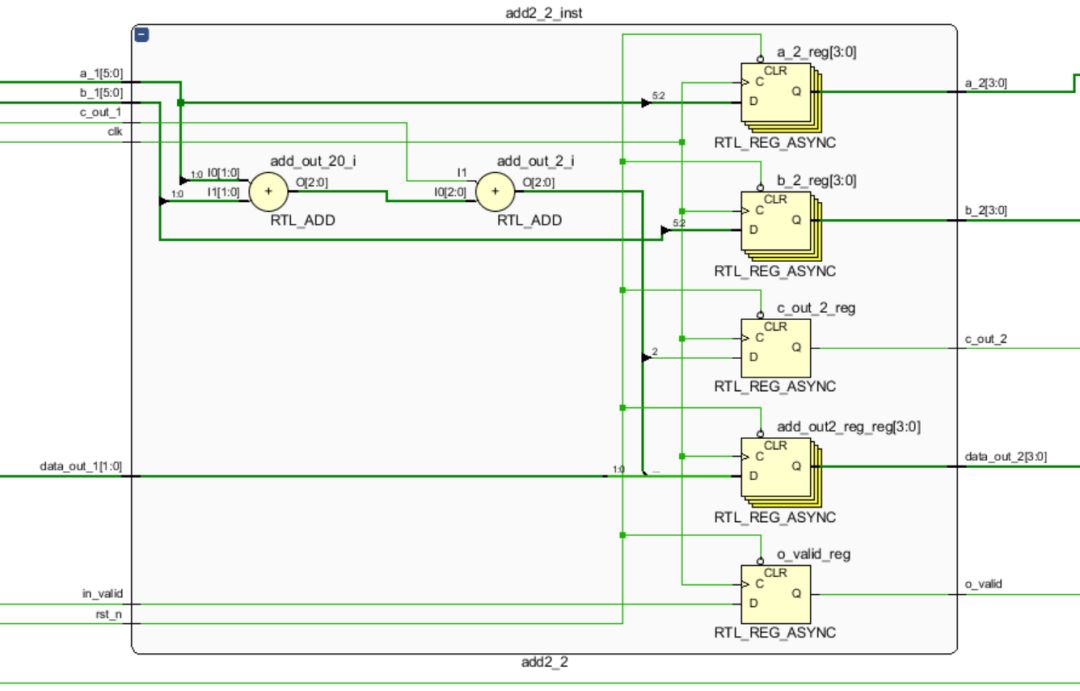

第二級(jí):做2,3兩位與上一級(jí)加法器的進(jìn)位位的加法操作,并將本級(jí)運(yùn)算結(jié)果和未做運(yùn)算的高4位傳給下一級(jí)。

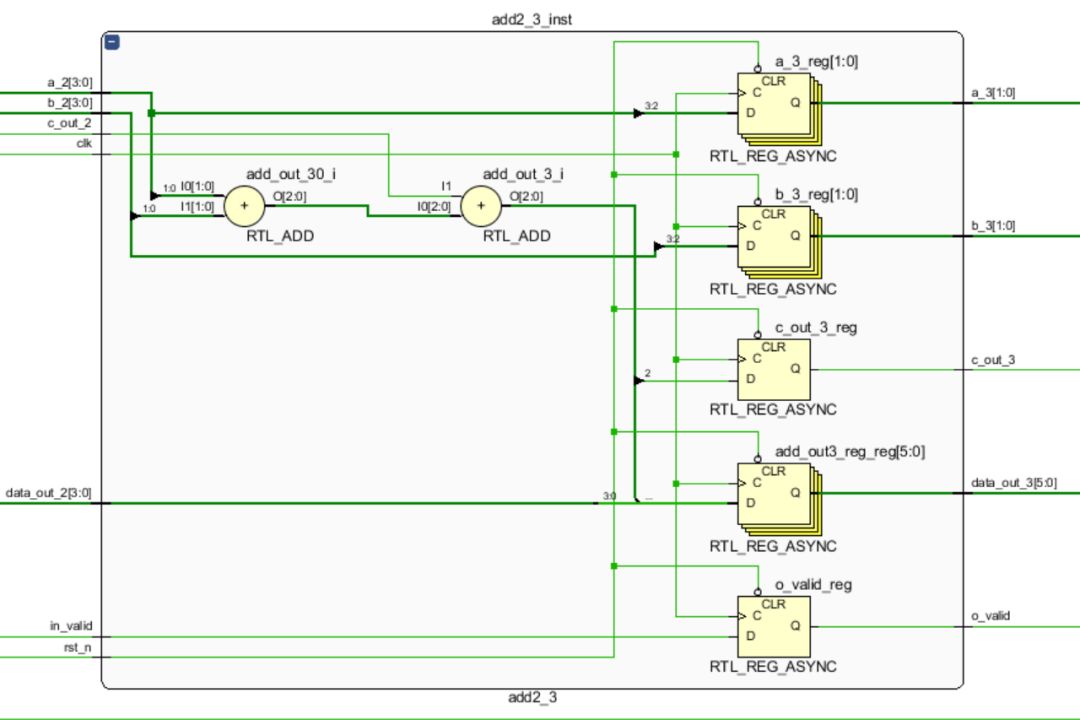

第三級(jí):做4,5兩位與進(jìn)位位的加法操作,并將運(yùn)算結(jié)果和未做運(yùn)算的高2位傳給下一級(jí)。

第四級(jí):做最高兩位與上一級(jí)加法器輸出的進(jìn)位位的加法操作,并將結(jié)果組合輸出。

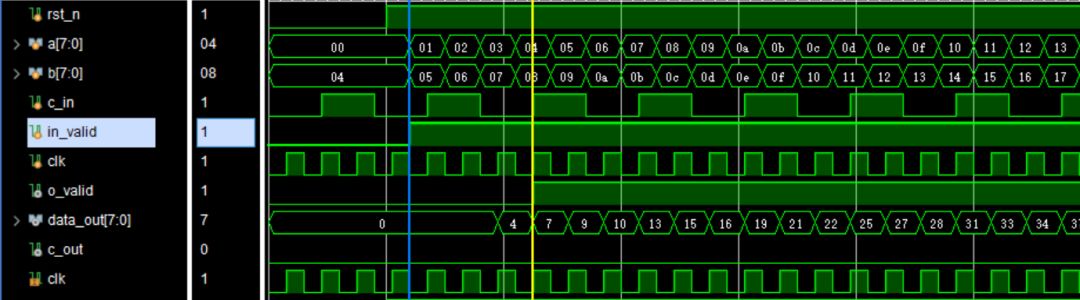

仿真結(jié)果如下:如圖,當(dāng)整體模塊in_valid有效時(shí),送進(jìn)去的數(shù)據(jù)a=1,b=5,c_in=1;故經(jīng)過四個(gè)周期后,o_valid信號(hào)拉高,同時(shí)獲得運(yùn)算結(jié)果data_out=7。(本設(shè)計(jì)的流水線每級(jí)延時(shí)為一個(gè)時(shí)鐘周期)

總結(jié)

流水線就是通過將一個(gè)大的組合邏輯劃分成分步運(yùn)算的多個(gè)小組合邏輯來運(yùn)算,從而達(dá)到提高速度的目的。

在設(shè)計(jì)流水線的時(shí)候,我們一般要盡量使得每級(jí)運(yùn)算所需要的時(shí)間差不多,從而做到流水匹配,提高效率。因?yàn)榱魉€的速度由運(yùn)算最慢的那一級(jí)電路決定。

-

流水線

+關(guān)注

關(guān)注

0文章

124瀏覽量

26506 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1637瀏覽量

81618

原文標(biāo)題:流水線設(shè)計(jì)

文章出處:【微信號(hào):LF-FPGA,微信公眾號(hào):小魚FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA中的流水線設(shè)計(jì)

周期精確的流水線仿真模型

FPGA重要設(shè)計(jì)思想及工程應(yīng)用之流水線設(shè)

流水線中的相關(guān)培訓(xùn)教程[1]

流水線中的相關(guān)培訓(xùn)教程[4]

FPGA之為什么要進(jìn)行流水線的設(shè)計(jì)

滾筒輸流水線故障排除方法

如何選擇合適的LED生產(chǎn)流水線輸送方式

嵌入式_流水線

評(píng)論