美國國防高級研究計(jì)劃局(DARPA)于2017年6月1日宣布推出電子復(fù)興計(jì)劃(Electronics Resurgence Initiative,簡稱ERI)。計(jì)劃未來五年投入超過 20億美元,聯(lián)合國防工業(yè)基地、學(xué)術(shù)界、國家實(shí)驗(yàn)室和其他創(chuàng)新溫床,開啟下一次電子革命。這是美國在電子領(lǐng)域花重金打造的又一具有國家戰(zhàn)略的科研計(jì)劃,本文將總體概要性的解讀電子復(fù)興計(jì)劃誕生的背景與意義,電子復(fù)興計(jì)劃的3大研究領(lǐng)域及6大研究方向。之后的系列文章將針對3大研究領(lǐng)域:材料與集成、系統(tǒng)架構(gòu)、設(shè)計(jì)分專題進(jìn)行研究與探討。

一、DARPA電子復(fù)興計(jì)劃誕生的背景與意義

DARPA成立于1958年,也正是Kilby提出集成電路的那一年,很多硅時代的進(jìn)步,包括半導(dǎo)體材料的基本進(jìn)步,大規(guī)模集成和精密制造,也都是在DARPA的支持和推動下得以實(shí)現(xiàn)。但是,與大多數(shù)發(fā)展道路一樣,縮放(也即將更多的晶體管放在同一個芯片上)也終將迎來終點(diǎn)。以摩爾定律為代表的電子小型化道路,將逐步觸到物理學(xué)和經(jīng)濟(jì)學(xué)的極限。隨著這個轉(zhuǎn)折點(diǎn)的臨近,微電子技術(shù)的發(fā)展將需要一個新的創(chuàng)新階段,從而繼續(xù)保持電子創(chuàng)新的現(xiàn)代奇跡。

過去70年來,美國因其在電子和半導(dǎo)體領(lǐng)域的領(lǐng)先地位,享受到了經(jīng)濟(jì)、政治和國家安全上的優(yōu)勢。如今,在摩爾定律走向終結(jié),電子領(lǐng)域急需轉(zhuǎn)變突破的關(guān)鍵點(diǎn),在人工智能和量子等新興技術(shù)及產(chǎn)業(yè)涌現(xiàn)的當(dāng)下,美國布局ERI計(jì)劃是為了下一個十年乃至百年的領(lǐng)先,同時也是為國防部一些頂級技術(shù)重點(diǎn)領(lǐng)域,包括量子計(jì)算、人工智能、先進(jìn)制造以及太空和生物技術(shù),打下重要的基礎(chǔ)。

ERI計(jì)劃將專注于開發(fā)用于電子設(shè)備的新材料,開發(fā)將電子設(shè)備集成到復(fù)雜電路中的新體系結(jié)構(gòu),以及進(jìn)行軟硬件設(shè)計(jì)上的創(chuàng)新。ERI計(jì)劃將補(bǔ)充DARPA去年創(chuàng)建的“聯(lián)合大學(xué)微電子學(xué)計(jì)劃”(Joint University Microelectronics Program,簡稱JUMP)。

二、ERI計(jì)劃與JUMP計(jì)劃形成互補(bǔ)

JUMP計(jì)劃是DARPA和行業(yè)聯(lián)盟半導(dǎo)體研究公司聯(lián)合資助的最大的基礎(chǔ)電子研究工作。預(yù)計(jì)在5年時間里投入1.5億美金,聯(lián)合了MIT、伯克利、加州大學(xué)體系里的美國眾多一流高校和研究所,設(shè)置了6個不同的研究中心,探索6大不同的方向,是一個多學(xué)科跨領(lǐng)域的大規(guī)模長期合作計(jì)劃,目標(biāo)是大幅度提高各類商用和軍用電子系統(tǒng)的性能、效率和能力(performance, efficiency, and capabilities)。

根據(jù)JUMP計(jì)劃的公開資料,這些研究和開發(fā)工作應(yīng)該“為美國國防部在先進(jìn)的雷達(dá)、通信和武器系統(tǒng)方面提供無與倫比的技術(shù)優(yōu)勢,為軍事和工業(yè)部門帶來優(yōu)勢,并為美國的經(jīng)濟(jì)和未來的經(jīng)濟(jì)增長,提供獨(dú)特的信息技術(shù)和對商業(yè)競爭力至關(guān)重要的處理能力”。

JUMP計(jì)劃專注于中長期(8到12年)探索性研究,預(yù)期的國防和商業(yè)價(jià)值將在2025到2030年這個時間線實(shí)現(xiàn)。聯(lián)盟致力于將資源集中在高風(fēng)險(xiǎn)、高收益、長期創(chuàng)新研究上面,加速電子技術(shù)和電路及子系統(tǒng)的生產(chǎn)力增長和性能提升,從而解決電子和系統(tǒng)技術(shù)中現(xiàn)有的和新出現(xiàn)的挑戰(zhàn)。

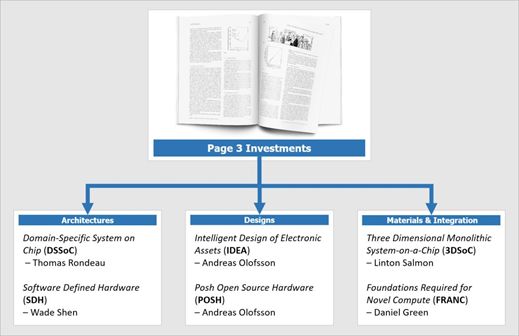

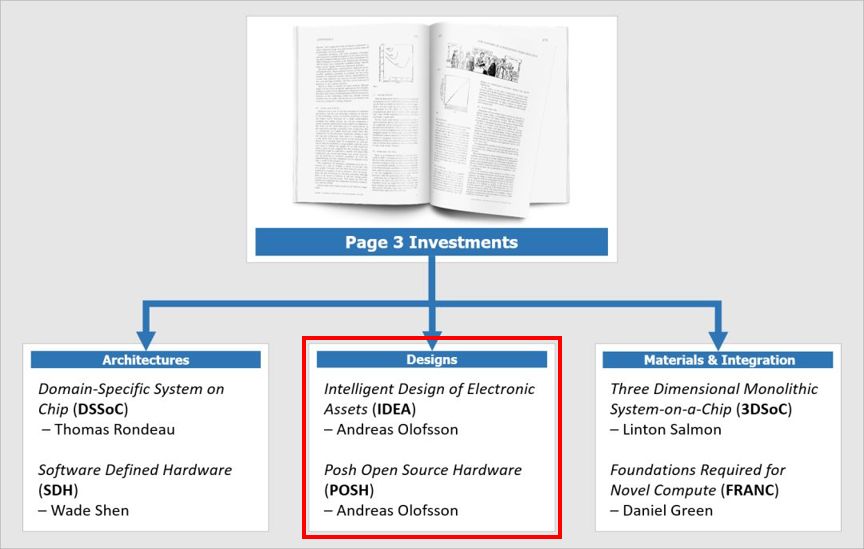

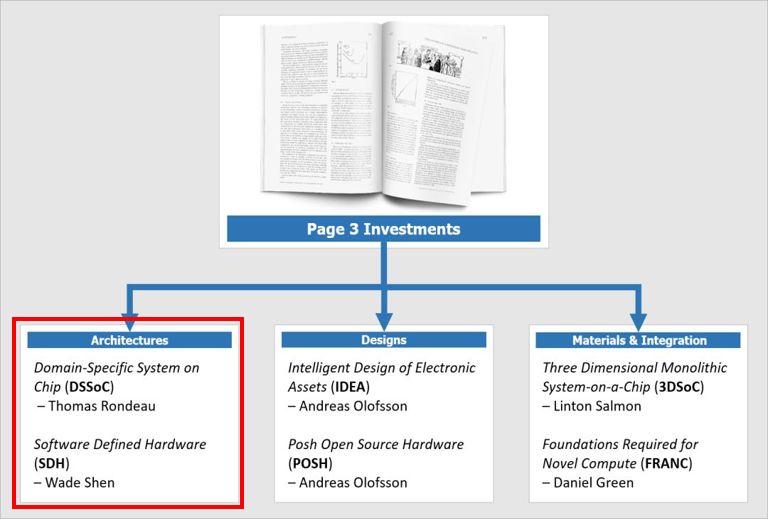

圖1 2017年9月公布的ERI計(jì)劃圖

如果說JUMP是一個更側(cè)重基礎(chǔ)和研究探索的計(jì)劃,那么ERI則更加實(shí)際一點(diǎn),也更接近產(chǎn)業(yè)。ERI的三大關(guān)注重點(diǎn):

開發(fā)用于電子設(shè)備的新材料(Materials and Integration):探索使用非常規(guī)電路元件而非更小的晶體管來大幅提高電路性能。硅是最常見的微系統(tǒng)材料,硅鍺等化合物半導(dǎo)體也在特定應(yīng)用中發(fā)揮了一定的作用,但這些材料的功能靈活性有限。ERI將表明,元素周期表為下一代邏輯和存儲器組件提供了大量候選材料。研究將著眼于在單個芯片上集成不同的半導(dǎo)體材料,結(jié)合了處理和存儲功能的“粘性邏輯”(sticky logic)設(shè)備,以及垂直而非平面集成微系統(tǒng)組件。

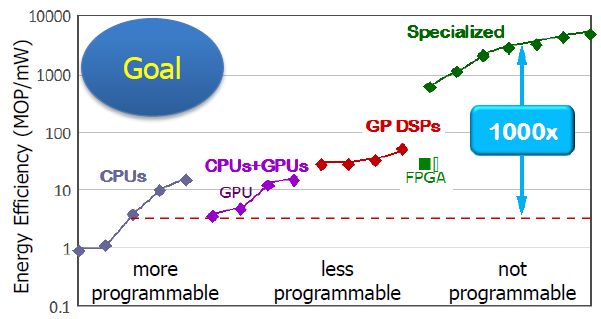

開發(fā)將電子設(shè)備集成到復(fù)雜電路中的新體系結(jié)構(gòu)(Architectures):探索針對其執(zhí)行的特定任務(wù)而優(yōu)化的電路結(jié)構(gòu)。GPU是機(jī)器學(xué)習(xí)持續(xù)進(jìn)展的基礎(chǔ),GPU已經(jīng)證明了從專用硬件體系結(jié)構(gòu)中能夠獲得大幅的性能提升。ERI將探索其他機(jī)遇,例如能根據(jù)所支持的軟件需求調(diào)整進(jìn)行可重新配置的物理結(jié)構(gòu)。

進(jìn)行軟硬件設(shè)計(jì)上的創(chuàng)新(Design):重點(diǎn)開發(fā)用于快速設(shè)計(jì)和實(shí)現(xiàn)專用電路的工具。與通用電路不同,專用電子設(shè)備可以更快、更節(jié)能。盡管DARPA一直投資于這些用于軍事用途的專用集成電路(ASIC),但ASIC的開發(fā)可能會花費(fèi)大量時間和費(fèi)用。新的設(shè)計(jì)工具和開放源代碼設(shè)計(jì)范例可能具有變革性,使創(chuàng)新者能夠快速便宜地為各種商業(yè)應(yīng)用創(chuàng)建專用電路。

三、DARPA“電子復(fù)興計(jì)劃”峰會宣布六大項(xiàng)目合作研究團(tuán)隊(duì)

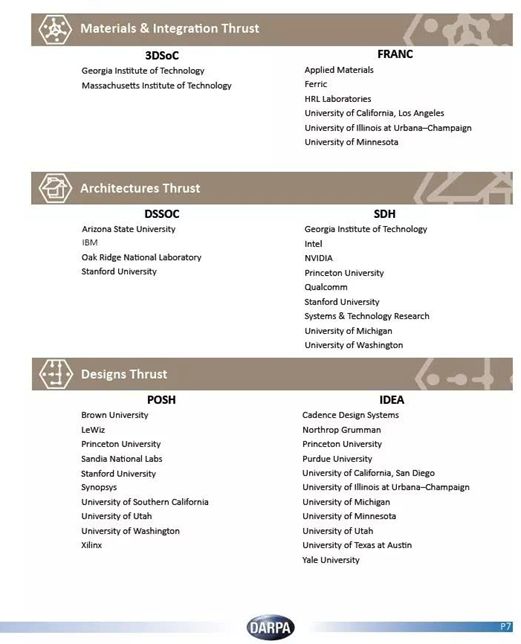

2018年7月23日,DARPA在加利福尼亞州舊金山舉辦的首屆年度“電子復(fù)興計(jì)劃”(ERI)峰會開幕式上,宣布了ERI六大項(xiàng)目合作研究團(tuán)隊(duì),旨在扶持和培養(yǎng)在材料與集成、電路設(shè)計(jì)和系統(tǒng)架構(gòu)三方面的創(chuàng)新性研究。

這六個項(xiàng)目旨在補(bǔ)充傳統(tǒng)晶體管尺寸的不斷縮小并確保持續(xù)改進(jìn)電子性能(解決Moore在50年前即預(yù)測到將在當(dāng)前半導(dǎo)體發(fā)展藍(lán)圖最后階段出現(xiàn)的問題),分別為:

1.“三維單芯片系統(tǒng)”——3DSoC:Three Dimensional Monolithic System-on-a-Chip

2.“新式計(jì)算基礎(chǔ)需求”——FRANC:Foundations Required for Novel Compute

3.“特定領(lǐng)域片上系統(tǒng)”——DSSoC:Domain-Specific System on a Chip

4.“軟件定義硬件”——SDH:Software Defined Hardware

5.“高端開源硬件”——POSH:Posh Open Source Hardware

6.“電子設(shè)備智能設(shè)計(jì)”——IDEA:Intelligent Design of Electronic Assets

圖2 ERI計(jì)劃六大項(xiàng)目專注于系統(tǒng)架構(gòu)、電路設(shè)計(jì)、材料與集成3大領(lǐng)域

1、材料與集成領(lǐng)域

(1)“三維單芯片系統(tǒng)”(3DSoC)項(xiàng)目

傳統(tǒng)微電子芯片為平面、二維結(jié)構(gòu),3DSoC項(xiàng)目主要聚焦在單襯底第三維度垂直向上構(gòu)建微系統(tǒng)所需材料、設(shè)計(jì)工具和制造技術(shù)的研發(fā)。通過該項(xiàng)目可實(shí)現(xiàn)邏輯、存儲及輸入/輸出元件的高效封裝,從而使系統(tǒng)的運(yùn)行功耗更低,計(jì)算速度提升50倍以上。

選定合作研究團(tuán)隊(duì)為Georgia Institute of Technology,Massachusetts Institute of Technology。

(2)“新式計(jì)算基礎(chǔ)需求”(FRANC)項(xiàng)目

項(xiàng)目的目標(biāo)是超越傳統(tǒng)邏輯和存儲功能相分離的馮諾依曼架構(gòu)。當(dāng)前,在馮諾依曼架構(gòu)下,因數(shù)據(jù)在存儲單元和處理器之間傳輸所造成的時間延遲和能量消耗成為阻礙計(jì)算機(jī)性能進(jìn)一步提升的主要原因。針對該項(xiàng)目所提出的研究計(jì)劃需要展示如何通過開發(fā)新型材料、器件及算法加速邏輯電路中的數(shù)據(jù)存儲速度或通過設(shè)計(jì)全新的、比以往更為復(fù)雜的邏輯和存儲電路結(jié)構(gòu)來突破這一“存儲瓶頸”。

選定合作研究團(tuán)隊(duì)為Applied Materials、Ferric、HRL Laboratories、University of California, Los Angeles、University of Illinois at Urbana–Champaign、University of Minnesota。

2、系統(tǒng)架構(gòu)領(lǐng)域

(1)“特定領(lǐng)域片上系統(tǒng)”(DSSoC)項(xiàng)目

該項(xiàng)目的設(shè)立是受通過單一編程框架實(shí)現(xiàn)多應(yīng)用系統(tǒng)快速開發(fā)需求的驅(qū)動。這一單一編程框架能夠使片上系統(tǒng)設(shè)計(jì)人員將通用、專用(如專用集成電路)、硬件加速輔助處理、存儲和輸入/輸出等要素進(jìn)行混合和匹配,從而實(shí)現(xiàn)特定技術(shù)領(lǐng)域應(yīng)用片上系統(tǒng)的簡單編程。例如,軟件定義無線電(software-defined radio)就是這些特定技術(shù)領(lǐng)域中的一種,應(yīng)用范圍包括移動通信、衛(wèi)星通信、私人網(wǎng)絡(luò)、所有類型雷達(dá)和網(wǎng)絡(luò)空間電子戰(zhàn)等。

選定合作研究團(tuán)隊(duì)為Arizona State University、IBM、Oak Ridge National Laboratory、Stanford University。

(2)“軟件定義硬件”(SDH)項(xiàng)目

該項(xiàng)目旨在構(gòu)建可重構(gòu)軟硬件設(shè)計(jì)和制造的決策輔助技術(shù)基礎(chǔ)。這些可重構(gòu)軟硬件需要具備運(yùn)行數(shù)據(jù)密集型算法的能力(具備該能力是實(shí)現(xiàn)未來機(jī)器學(xué)習(xí)和自主系統(tǒng)的基礎(chǔ))和與目前專用集成電路(ASICs)相當(dāng)?shù)男阅堋T诂F(xiàn)代戰(zhàn)爭中,決策是由所獲取的數(shù)據(jù)信息來驅(qū)動的,例如,由成千上萬個傳感器提供的情報(bào)、監(jiān)視和偵察(ISR)數(shù)據(jù)、后勤物流/供應(yīng)鏈數(shù)據(jù)和人員績效評估指標(biāo)數(shù)據(jù)等。對這些數(shù)據(jù)的有效利用依賴于可進(jìn)行大規(guī)模計(jì)算的有效算法。

選定合作研究團(tuán)隊(duì)為Georgia Institute of Technology、Intel、NVIDIA、Princeton University、Qualcomm、Stanford University、Systems & Technology Research、University of Michigan、University of Washington。

3、電路設(shè)計(jì)領(lǐng)域

(1)“高端開源硬件”(POSH)項(xiàng)目

該項(xiàng)目旨在構(gòu)建一個開源的設(shè)計(jì)和驗(yàn)證框架,包括以低成本實(shí)現(xiàn)超復(fù)雜片上系統(tǒng)設(shè)計(jì)的技術(shù)、方法和標(biāo)準(zhǔn)。DARPA“電子復(fù)興”計(jì)劃團(tuán)隊(duì)期望利用可降低復(fù)雜片上系統(tǒng)設(shè)計(jì)門檻的全新設(shè)計(jì)工具開啟專用設(shè)計(jì)創(chuàng)新的新時代。開源軟件最有可能成為在應(yīng)用層面實(shí)現(xiàn)創(chuàng)新的工具。

選定合作研究團(tuán)隊(duì)為Brown University、LeWiz、Princeton University、Sandia National Labs、Stanford University、Synopsys、University of Southern California、University of Utah、University of Washington、Xilinx。

(2)“電子設(shè)備智能設(shè)計(jì)”(IDEA)項(xiàng)目

該項(xiàng)目將開發(fā)創(chuàng)建電子硬件自動化布局生成器所需的算法、方法、軟件,使沒有電子設(shè)計(jì)知識的用戶能夠在24小時內(nèi)完成混合信號集成電路、系統(tǒng)級封裝和印刷電路板等電子硬件的物理設(shè)計(jì)。

選定合作研究團(tuán)隊(duì)為Cadence Design Systems、Northrop Grumman、Princeton University、Purdue University、University of California, San Diego、University of Illinois at Urbana–Champaign、University of Michigan、University of Minnesota、University of Utah、University of Texas at Austin、Yale University。

圖3 DARPA于2018年7月公布6大項(xiàng)目合作研究團(tuán)隊(duì)

2

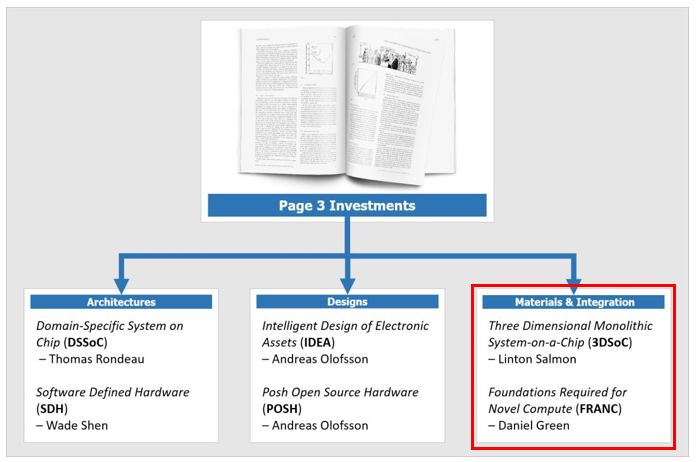

近年來(2005年~2018年),美國國防高級研究計(jì)劃局(DARPA)在集成電路的材料領(lǐng)域進(jìn)行了多項(xiàng)研究,對材料的研究創(chuàng)新不僅僅局限于半導(dǎo)體器件材料的研究,而是更加強(qiáng)調(diào)了材料在集成電路集成中所發(fā)揮的應(yīng)用。下面詳細(xì)介紹DARPA最近推出的電子復(fù)興計(jì)劃(Electronics Resurgence Initiative,簡稱ERI)中與材料相關(guān)的研究內(nèi)容。材料與集成領(lǐng)域的主要研究方向包括三維單芯片系統(tǒng)(3DSoC)和新式計(jì)算基礎(chǔ)需求(FRANC)。

圖1 ERI計(jì)劃中材料與集成領(lǐng)域的研究內(nèi)容

一、“三維單芯片系統(tǒng)”(3DSoC)項(xiàng)目

傳統(tǒng)微電子芯片為平面、二維結(jié)構(gòu),3DSoC項(xiàng)目主要聚焦在單襯底第三維度垂直向上構(gòu)建微系統(tǒng)所需材料、設(shè)計(jì)工具和制造技術(shù)的研發(fā)。通過該項(xiàng)目可實(shí)現(xiàn)邏輯、存儲及輸入/輸出元件的高效封裝,從而使系統(tǒng)的運(yùn)行功耗更低,計(jì)算速度提升50倍以上。該項(xiàng)目材料的研究與系統(tǒng)集成密切相關(guān),主要在于3DSoC芯片中不同邏輯和存儲層的材料選取,以實(shí)現(xiàn)高性能的3DSoC芯片。

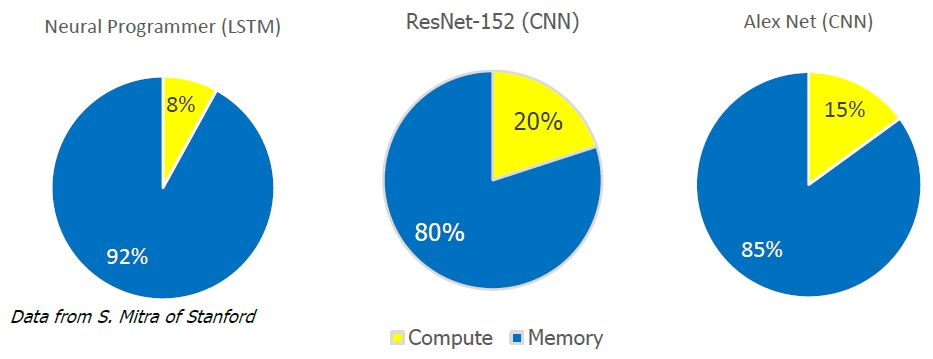

通過對基于7nm技術(shù)和不同算法的最新機(jī)器學(xué)習(xí)加速器的應(yīng)用執(zhí)行時間分析(如圖2所示),雖然不同的機(jī)器學(xué)習(xí)算法從存儲器中讀寫數(shù)據(jù)的時間略有不同,但是不管何種算法,存儲器讀寫數(shù)據(jù)占用的時間均達(dá)到了80%以上,是限制計(jì)算速度的主要瓶頸。

圖2 基于7nm技術(shù)和不同算法的最新機(jī)器學(xué)習(xí)加速器的應(yīng)用執(zhí)行時間分析

通過構(gòu)建3DSoC芯片能縮短存儲器和邏輯運(yùn)算結(jié)構(gòu)之間的物理距離,從而進(jìn)一步減少存儲器讀寫數(shù)據(jù)的時間,提高預(yù)算速度。作為3DSoC系統(tǒng)的一個成功舉例,下圖為Stanford大學(xué)S. Mitra 等人將3DSoC中的邏輯層和存儲層制造在同一Die上的新型器件結(jié)構(gòu)。

圖3 Stanford大學(xué)S. Mitra團(tuán)隊(duì)研究的新型3DSoC解決方案

二、“新式計(jì)算基礎(chǔ)需求”(FRANC)項(xiàng)目

項(xiàng)目的目標(biāo)是超越傳統(tǒng)邏輯和存儲功能相分離的馮諾依曼架構(gòu)。當(dāng)前,在馮諾依曼架構(gòu)下,因數(shù)據(jù)在存儲單元和處理器之間傳輸所造成的時間延遲和能量消耗成為阻礙計(jì)算機(jī)性能進(jìn)一步提升的主要原因。針對該項(xiàng)目所提出的研究計(jì)劃需要展示如何通過開發(fā)新型材料、器件及算法加速邏輯電路中的數(shù)據(jù)存儲速度或通過設(shè)計(jì)全新的、比以往更為復(fù)雜的邏輯和存儲電路結(jié)構(gòu)來突破這一“存儲瓶頸”。

FRANC項(xiàng)目分為兩大技術(shù)領(lǐng)域如下所示:

技術(shù)領(lǐng)域1(TA1)研究新的拓?fù)潆娐吩?/p>

子領(lǐng)域1:實(shí)現(xiàn)超越馮-諾伊曼拓?fù)涞碾娐吩? 利用現(xiàn)有的材料和集成技術(shù), 集成處理器和存儲器來創(chuàng)建革命性的功能

子領(lǐng)域2: 允許利用新材料或集成技術(shù),在馮-諾伊曼體系中集成非馮諾伊曼結(jié)構(gòu)的加速器,加速器的性能優(yōu)勢可量化

技術(shù)領(lǐng)域2(TA2)研究新型計(jì)算的功能模組

開發(fā)支持超越馮-諾伊曼結(jié)構(gòu)的組件或子系統(tǒng),特別是開發(fā)新材料或集成技術(shù),使未來的2.5D或3D集成解決方案能夠在超越馮-諾伊曼計(jì)算拓?fù)涞谋尘跋聦?shí)現(xiàn),研究主題包括加速材料發(fā)現(xiàn)、非易失性存儲器(NVM)、IC電源管理、芯片級光子組件。

圖4 創(chuàng)新拓?fù)潆娐吩偷膬煞N方式

三維單芯片系統(tǒng)(3DSoC)和新式計(jì)算基礎(chǔ)需求(FRANC)兩大研究方向的目的都是問了解決存儲器讀寫數(shù)據(jù)占用時間長這一限制計(jì)算速度的主要瓶頸,3DSoC是從3D垂直結(jié)構(gòu)的角度出發(fā),試圖通過新材料與3D結(jié)構(gòu)的融合實(shí)現(xiàn)這一目的。而FRANC項(xiàng)目用“新的材料和集成方案”創(chuàng)建“新穎的計(jì)算拓?fù)洹保ㄗh采取內(nèi)存內(nèi)計(jì)算、近內(nèi)存計(jì)算等全新的拓?fù)錂C(jī)構(gòu)來消除或減少數(shù)據(jù)移動的方式來加快處理數(shù)據(jù)的速度。通過這兩個研究項(xiàng)目,我們可以發(fā)現(xiàn)DARPA強(qiáng)調(diào)材料在集成電路器件集成中發(fā)揮的作用,希望通過新材料結(jié)合新架構(gòu)、新拓?fù)浣Y(jié)構(gòu)提高處理大數(shù)據(jù)的能力,為人工智能、超級計(jì)算等前沿領(lǐng)域的發(fā)展奠定基礎(chǔ)。

3

上一章介紹了DARPA電子復(fù)興計(jì)劃(Electronics Resurgence Initiative,簡稱ERI)在材料與集成領(lǐng)域的布局和兩個重點(diǎn)研究方向,本章介紹電子復(fù)興計(jì)劃中與電子電路設(shè)計(jì)相關(guān)的研究內(nèi)容。電子電路設(shè)計(jì)領(lǐng)域的主要研究方向包括電子設(shè)備智能設(shè)計(jì)(IDEA)和高端開源硬件(POSH)。

圖1 ERI計(jì)劃中電子電路設(shè)計(jì)領(lǐng)域的研究內(nèi)容

一、電子設(shè)備智能設(shè)計(jì)(IDEA)項(xiàng)目

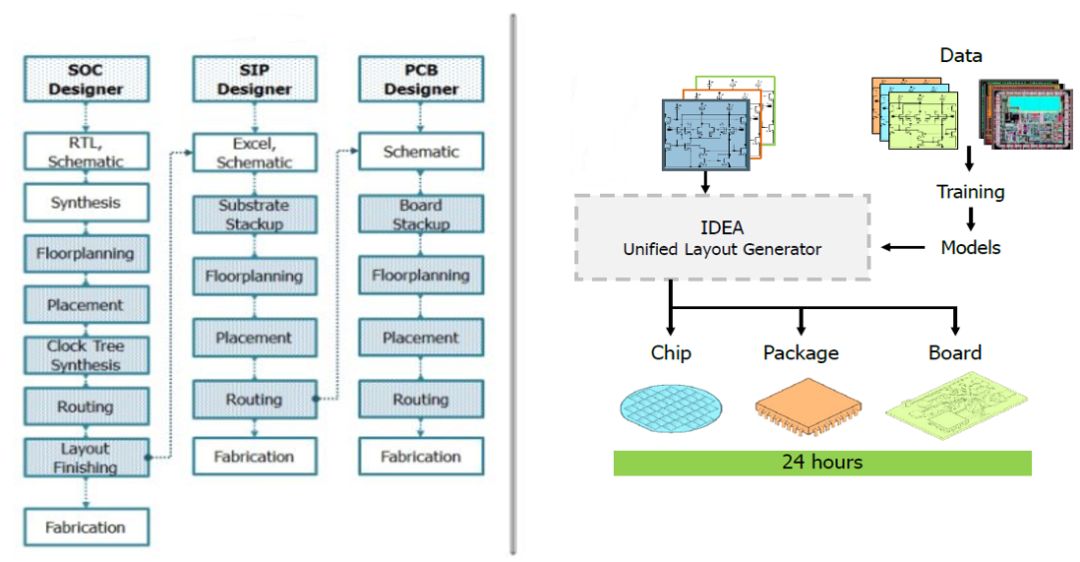

相比軟件行業(yè),芯片行業(yè)除了需要流片之外,還要解決兩大關(guān)鍵問題,第一是版圖設(shè)計(jì),在電路設(shè)計(jì)完成之后需要通過版圖設(shè)計(jì)生成GDS,第二是設(shè)計(jì)復(fù)用問題。IDEA項(xiàng)目就是針對第一大關(guān)鍵問題醞釀而生,目前數(shù)字電路的版圖生成自動化程度已經(jīng)相當(dāng)高,但是模擬和混合信號電路仍然非常依賴手工去做版圖。IDEA項(xiàng)目的研究目標(biāo)是實(shí)現(xiàn)“設(shè)計(jì)過程中無人干預(yù)”的能力,在混合信號集成電路、多集成電路模塊系統(tǒng)級封裝和印刷電路板等復(fù)雜電子技術(shù)的24小時設(shè)計(jì)框架中也無需專家進(jìn)行設(shè)計(jì)。

如下圖所示,當(dāng)今的SOC、SIP和PCB的設(shè)計(jì)流程在大部分環(huán)節(jié)都非常依賴于專業(yè)設(shè)計(jì)人員的知識輸入,專業(yè)知識的載體是技術(shù)人員。IDEA項(xiàng)目的特點(diǎn)是通過收集大量的原始設(shè)計(jì)數(shù)據(jù),通過人工智能和機(jī)器學(xué)習(xí)的方法訓(xùn)練得到模型,進(jìn)而將模型導(dǎo)入一個統(tǒng)一的版圖生成器中,通過版圖生成器在24小時之內(nèi)完成混合信號集成電路、多集成電路模塊系統(tǒng)級封裝和印刷電路板等的設(shè)計(jì)。IDEA的特點(diǎn)是專業(yè)知識的載體是軟件,設(shè)計(jì)周期短,自動化程度高。

圖2 當(dāng)今SOC、SIP、PCB設(shè)計(jì)的流程(左)和IDEA項(xiàng)目的設(shè)計(jì)框架(右)

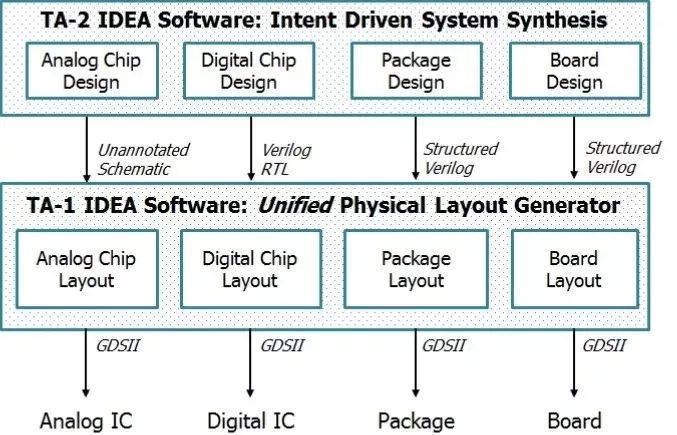

IDEA項(xiàng)目的兩大技術(shù)領(lǐng)域分別是技術(shù)領(lǐng)域1(TA1):機(jī)器自動生成物理版圖, 為模擬和數(shù)字SoCs, SiPs, PCBs開發(fā)一個統(tǒng)一的物理版圖生成器和技術(shù)領(lǐng)域2(TA2):意圖驅(qū)動的系統(tǒng)合成,開發(fā)一個意圖驅(qū)動的、自動建構(gòu)校正的系統(tǒng)生成器,如下圖3所示。技術(shù)領(lǐng)域1的輸入是用于模擬IC設(shè)計(jì)的netlist、用于數(shù)字IC設(shè)計(jì)的Verilog RTL、用于SiPs的結(jié)構(gòu)化Verilog netlist和用于PCBs的結(jié)構(gòu)化Verilog netlist,其輸出是模擬電路、數(shù)字電路、多集成電路模塊系統(tǒng)級封裝和印刷電路板的版圖設(shè)計(jì)。設(shè)計(jì)領(lǐng)域2則主要是根據(jù)系統(tǒng)的需求,基于一些組件模塊,比如可用的封裝、SiP用的die、SoC IP,生成設(shè)計(jì)網(wǎng)表,提供給技術(shù)領(lǐng)域1工具進(jìn)行物理設(shè)計(jì)。

圖3 IDEA項(xiàng)目的兩大技術(shù)領(lǐng)域

二、高端開源硬件(POSH)項(xiàng)目

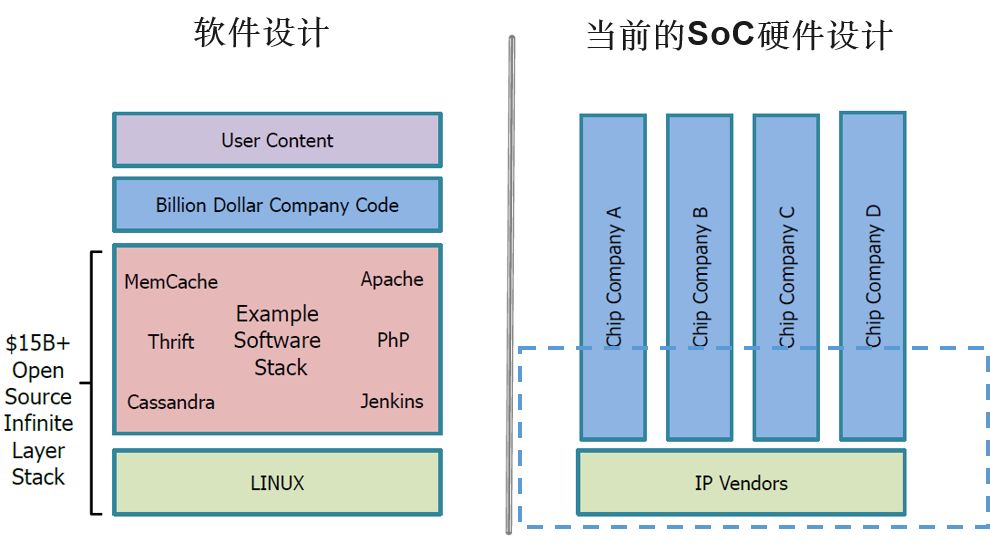

開源軟件的蓬勃發(fā)展是目前軟件開發(fā)可以快速、低成本實(shí)現(xiàn)的一個關(guān)鍵。從Linux,GNU,Android到現(xiàn)在各種開源的AI Framework,成功的開源項(xiàng)目往往能夠產(chǎn)生革命性的影響。而在硬件設(shè)計(jì)難度和成本越來越高的情況下,“能否在硬件領(lǐng)域復(fù)制開源軟件的成功”,自然成為一個值得考慮的問題。在這個背景下,DARPA的高端開源硬件(POSH)項(xiàng)目將提供開源設(shè)計(jì)和驗(yàn)證框架,包括技術(shù)、方法、標(biāo)準(zhǔn),從而實(shí)現(xiàn)具有成本效益的超復(fù)雜片上系統(tǒng)設(shè)計(jì)。DARPA希望可降低復(fù)雜片上系統(tǒng)設(shè)計(jì)障礙的新工具能夠打開一個特定應(yīng)用設(shè)計(jì)創(chuàng)新的新時代。

圖4 軟件設(shè)計(jì)和硬件設(shè)計(jì)對比

如圖4所示,目前軟件設(shè)計(jì)中開源的部分很多,例如圖中所提到的開源分布式NoSQL數(shù)據(jù)庫系統(tǒng)Cassandra、開源的持續(xù)集成工具Jenkins、開源的軟件框架Thrift、開源軟件開發(fā)框架PhP等。對比軟件的開源性,目前的SoC設(shè)計(jì)方法使IC設(shè)計(jì)開始進(jìn)一步分工細(xì)化,出現(xiàn)了IP設(shè)計(jì)和SoC系統(tǒng)設(shè)計(jì)。對應(yīng)于IP設(shè)計(jì)的IP Vendor的類型很多,主要包括了芯片設(shè)計(jì)公司、Foundry廠商、專業(yè)IP公司、EDA廠商等,其提供的IP核是芯片的核心組成部分,往往極具商業(yè)價(jià)值而非開源公開的。

在芯片設(shè)計(jì)項(xiàng)目中最重要的工作之一是驗(yàn)證工作,因?yàn)樾酒荒苁。ɑ蛘哂腥毕荩H绻酒布袩o法解決的bug,它帶來的損失輕則是一次投片的費(fèi)用打水漂,重則影響產(chǎn)品的上市時間或者公司的信譽(yù),導(dǎo)致客戶的流失,可能帶來致命的打擊。芯片項(xiàng)目和軟件項(xiàng)目對Bug的容忍度有著根本的不同,基于此特點(diǎn),POSH項(xiàng)目確立了三個主要技術(shù)目標(biāo):技術(shù)目標(biāo)1(TA1):Hardware Assurance Technology指的是開發(fā)快速、有效、低成本的硬件驗(yàn)證方法對開源硬件進(jìn)行有效質(zhì)量驗(yàn)證;技術(shù)目標(biāo)2(TA2):Open Source Hardware Technology指的是通過開發(fā)設(shè)計(jì)方法、標(biāo)準(zhǔn)、核心IP組件來創(chuàng)建一個可行的開源SoC生態(tài)系統(tǒng);技術(shù)目標(biāo)3(TA3):Open Source System-On-Chip Demonstration指的是通過設(shè)計(jì)一個最先進(jìn)的開源SoC來驗(yàn)證開源硬件實(shí)施的可行性。

硬件開源是一個討論了很久的話題,最近由于Nvidia開源DLA獲得了更多關(guān)注。軟件開源的成功能否能復(fù)制到硬件,既面臨技術(shù)的挑戰(zhàn),又有生態(tài)和經(jīng)濟(jì)因素等諸多限制,挑戰(zhàn)很大。但不管怎么說,能將自己的知識成果分享給大家,POSH、NVDLA和其它開源硬件項(xiàng)目能夠開源就是非常有價(jià)值的事情。

4

上一章文章介紹了DARPA電子復(fù)興計(jì)劃(Electronics Resurgence Initiative,簡稱ERI)在電子電路設(shè)計(jì)領(lǐng)域的布局和兩個重點(diǎn)研究方向,本章介紹電子復(fù)興計(jì)劃中與系統(tǒng)架構(gòu)相關(guān)的研究內(nèi)容。系統(tǒng)架構(gòu)領(lǐng)域的主要研究方向包括特定領(lǐng)域片上系統(tǒng)(DSSoC)和軟件定義硬件(SDH)。

圖1 ERI計(jì)劃中系統(tǒng)架構(gòu)領(lǐng)域的研究內(nèi)容

一、特定領(lǐng)域片上系統(tǒng)(DSSoC)項(xiàng)目

特定領(lǐng)域(Domain-Specific)的概念現(xiàn)在提的越來越多,大家也都逐漸看到它的重要性。現(xiàn)在的芯片項(xiàng)目越來越復(fù)雜,軟件所占的比例非常高,投片、研發(fā)和應(yīng)用的成本和風(fēng)險(xiǎn)越來越高。一套能把軟硬件設(shè)計(jì)垂直整合起來的方法和工具,可以在不同但相似的應(yīng)用間最大限度的實(shí)現(xiàn)重用,從而提高設(shè)計(jì)效率,降低成本。DSSoC項(xiàng)目的研究目標(biāo)是將開發(fā)一種由通用處理器、專用處理器、硬件加速器、存儲器、輸入/輸出元件等多個內(nèi)核組成的異構(gòu)片上系統(tǒng),進(jìn)而通過單個可編程器件實(shí)現(xiàn)多應(yīng)用系統(tǒng)的快速開發(fā)。

如下圖所示,當(dāng)前許多高性能的專用芯片是以可編程性作為代價(jià),特定芯片存在可編程弱和系統(tǒng)集成難度大的困難。如何設(shè)計(jì)一個系統(tǒng)架構(gòu),能夠同時權(quán)衡專用性和通用性?特定領(lǐng)域計(jì)算的本質(zhì)是建立一套完整的方法學(xué)和工具,能夠高效的設(shè)計(jì)和實(shí)現(xiàn)面向一個領(lǐng)域的軟硬件系統(tǒng),同時這套方法和工具還可以方便的應(yīng)用到新的領(lǐng)域。DSSoC項(xiàng)目提供一套垂直整合的方法,通過一個full-stack integration,提供一個軟硬件框架,讓程序員不必要了解底層硬件,但仍然可以充分的利用硬件的效率。目前,我們做一個架構(gòu)設(shè)計(jì)的時候,往往要在通用性(可編程性)和專用性(高效率)之間做很多權(quán)衡。如果這個項(xiàng)目成功,那么在通用性和專用性之間的權(quán)衡就可以變得不那么困難了。

圖2 當(dāng)前芯片在可編程性和高性能方面的對比分析

如下圖所示,DSSoC在軟硬件垂直整合的方法體系中提出了5大關(guān)鍵技術(shù):(1)Intelligent Scheduler:通過在系統(tǒng)中增加專用于調(diào)度的處理器,以及讓每個Processor Elements (PE)都可以分析并上報(bào)自己的運(yùn)行狀態(tài)實(shí)現(xiàn)資源智能調(diào)度;(2)Software:軟件工具包括開發(fā)工具,如編譯器和調(diào)試器,算法庫,以及Domain的應(yīng)用程序和示例。軟件工具是特定領(lǐng)域計(jì)算能否真正落地的最重要部分,一個基本要求是可以支持領(lǐng)域內(nèi)的新的設(shè)計(jì);(3)Domain ontology:描述Domain的特征,反映不同分組間的關(guān)系,對算法的細(xì)節(jié)特征進(jìn)行描述,支持項(xiàng)目中的智能調(diào)度等工作;(4)Medium access control (MAC):MAC層是在PE間交換數(shù)據(jù)結(jié)構(gòu)的媒介,既包括物理結(jié)構(gòu),拓?fù)洌€包括一個標(biāo)準(zhǔn)編程接口;(5)Hardware integration:異構(gòu)的SoC硬件, 包括CPU,GPU,TPU,Neuromorphic Unit,DSP,硬件加速器等。

圖3 DSSoC項(xiàng)目提出的軟硬件垂直整合方法

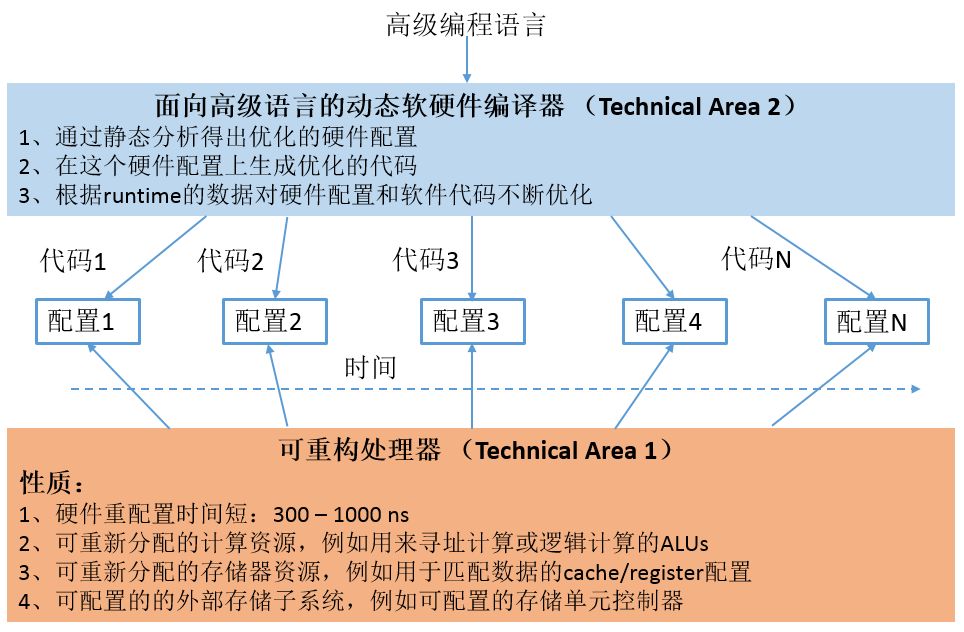

二、軟件定義硬件(SDH)項(xiàng)目

軟件定義硬件項(xiàng)目的研究目標(biāo)是創(chuàng)建運(yùn)行時可重新配置的硬件和軟件,在不犧牲數(shù)據(jù)密集型算法的可編程性的情況下實(shí)現(xiàn)類似專用集成電路(ASIC)的性能,且沒有專用集成電路開發(fā)相關(guān)的成本、開發(fā)時間或單個應(yīng)用限制。在處理器設(shè)計(jì)過程中需要權(quán)衡的因素包括數(shù)學(xué)/邏輯資源、存儲器、地址計(jì)算、數(shù)據(jù)讀寫和傳送等,最優(yōu)硬件配置根據(jù)算法不同而不同,沒有一種硬件配置能有效解決所有的問題。現(xiàn)在雖然硬件設(shè)計(jì)水平已經(jīng)達(dá)到專業(yè)化,但每個算法需要設(shè)計(jì)一個芯片,因此芯片設(shè)計(jì)成本高,往往也不具備可再編程性。通過SDH項(xiàng)目希望實(shí)現(xiàn)軟硬件的Runtime優(yōu)化,進(jìn)而實(shí)現(xiàn)一個芯片實(shí)現(xiàn)多個應(yīng)用,節(jié)約芯片設(shè)計(jì)成本,硬件通過高級語言實(shí)現(xiàn)可再編程性。

SDH程序?qū)?chuàng)建一個可擴(kuò)展的硬件/軟件架構(gòu),與ASIC不同,允許應(yīng)用程序在運(yùn)行時修改硬件配置。 SDH將實(shí)現(xiàn)兩大目標(biāo):(1)輸入數(shù)據(jù)變化時動態(tài)優(yōu)化代碼和硬件; (2)能夠重用硬件來解決新問題,支持新算法。 為了實(shí)現(xiàn)這些目標(biāo),SDH把重點(diǎn)放在高速硬件重配置(very fast hardware reconfiguration speeds)和動態(tài)編譯(dynamic compilation)。

SDH項(xiàng)目確立了兩個主要技術(shù)目標(biāo):技術(shù)目標(biāo)1(TA1)可重構(gòu)處理器:可重構(gòu)處理器要求重配置速度高于FPGA,而效率又要接近ASIC,功耗要遠(yuǎn)低于FPGA。而且這個處理器不僅要求片上的運(yùn)算和存儲可以重構(gòu),外部存儲子系統(tǒng)也要求能夠被配置為不同的數(shù)據(jù)訪問模式;技術(shù)目標(biāo)2(TA2)面向高級語言的動態(tài)軟硬件編譯器:在runtime時的優(yōu)化同時包括了軟件和硬件,編譯器需要能夠把高級語言轉(zhuǎn)換為機(jī)器語言以及面向應(yīng)用的硬件配置。

圖4 SDH項(xiàng)目的兩大技術(shù)領(lǐng)域

-

芯片

+關(guān)注

關(guān)注

455文章

50725瀏覽量

423177 -

集成電路

+關(guān)注

關(guān)注

5387文章

11534瀏覽量

361652 -

DARPA

+關(guān)注

關(guān)注

4文章

72瀏覽量

27827

原文標(biāo)題:深入解讀DARPA電子復(fù)興計(jì)劃

文章出處:【微信號:BIEIqbs,微信公眾號:北京市電子科技情報(bào)研究所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

DARPA電子復(fù)興計(jì)劃誕生的背景與意義

DARPA電子復(fù)興計(jì)劃誕生的背景與意義

評論