UART(串口)收發模塊設計- 01

UART協議介紹

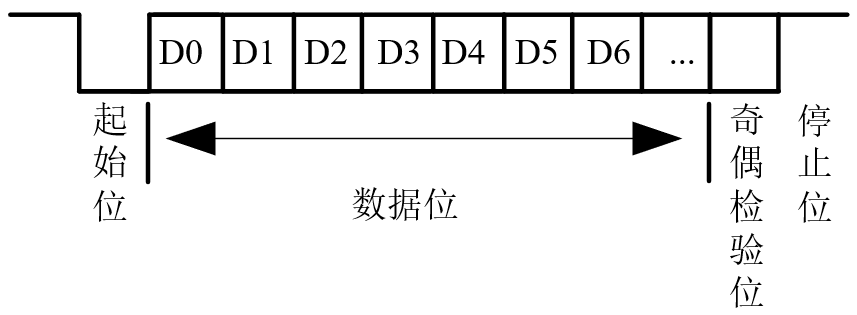

UART作為異步串口通信協議的一種,工作原理是將要傳輸的數據一位一位地傳輸。其中每一位(bit)的意義如下。

空閑位:在無數據傳輸的時候,傳輸線上的電平為高電平,即為空閑位。

起始位:當開始傳輸數據時,先發出1bit位寬的低電平,表示數據開始傳輸,即為起始位。

數據位:真正的需要發送的數據,位寬可以為4到10bit。數據從低bit開始向外一位一位的發送。

奇偶校驗位(可不要):當數據發送完畢后,再發送1位校驗位,以此來校驗數據傳送的正確性。

(偶校驗:數據位加上這一位后,使得“1”的位數應為偶數

奇校驗:數據位加上這一位后,使得“1”的位數應為奇數)

停止位:在最后發送一位高電平的停止位。

UART每一位的位寬時長由波特率決定,波特率既1s發送的數據位數。一般選擇的波特率有,9600,19200,115200等。

設計實例概述

本設計代碼鏈接:https://pan.baidu.com/s/1VJoSPJRSHYMhmx3rs2t4IA

提取碼:jsak

復制這段內容后打開百度網盤手機App,操作更方便哦

本實例設計的UART特性:

(1) 并沒有支持奇偶檢驗,故沒有奇偶校驗位

(2) 并不支持數據位寬可配,數據位位寬固定為8bit。

(3) 支持輸入時鐘與波特率可配。

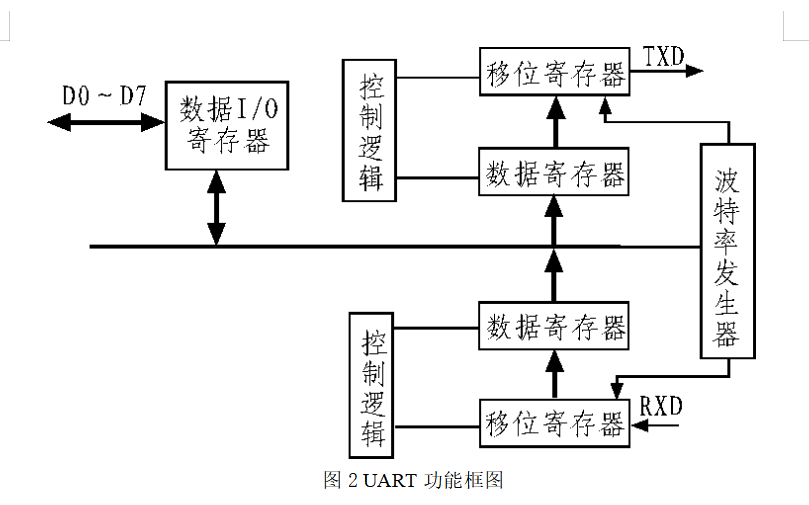

原理圖如下,分兩個大模塊,一個數據接收控制模塊(Receive_Control),一個數據發送控制模塊(Send_Control):

端口說明:

接收控制模塊與發送控制模塊內部都有一個波特率時鐘產生模塊(BuadRate_set),用于將電路輸入時鐘(clk)進行分頻產生波特率時鐘,用于接收和發送數據控制。

可以看到,BuadRate_set模塊有一個enable控制信號,只有當enable信號為高時,BuadRate_set模塊才工作。在發送控制模塊里面,只有發送數據的時候才拉高其相應的enable;在接收控制模塊里面,只有檢測到有數據發送進來的時候才拉高其相應的enable。這是為了降低功耗。

后文預告

后文將會具體介紹內部各個模塊的設計細節以及收發速度匹配和仿真驗證等問題。

-

控制模塊

+關注

關注

2文章

130瀏覽量

18852 -

uart

+關注

關注

22文章

1235瀏覽量

101355 -

異步串口

+關注

關注

0文章

11瀏覽量

9197

原文標題:UART(串口)收發模塊設計- 01

文章出處:【微信號:LF-FPGA,微信公眾號:小魚FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

協議棧介紹--TCP/IP

協議棧介紹

用verilog實現UART協議理解何為接口以及如何進行模塊化設計

FPGA片內FIFO的功能概述和模塊劃分

請問我怎樣設置實現串口UART通信?

UART串口通訊協議是什么

了解一下DMX512的基本協議

DMX512的基本協議相關資料分享

SKYLAB:簡單介紹兩款UART接口的WiFi模塊

如何設計和實現基于UART的機器人分布式控制通信協議概述

使用FPGA和模塊化設計方法實現UART的設計論文

振弦采集模塊UART 通訊協議

UART的基本協議與設計實例模塊劃分以及整體實現概述

UART的基本協議與設計實例模塊劃分以及整體實現概述

評論