有時,微控制器本身可以完全吸收設計的所有功能要求。對于絕大多數嵌入式系統設計而言,編程良好,高度集成的嵌入式處理器是工程師可以使用的最具成本效益,功效最高,速度最快的解決方案。

當原始性能至關重要時,捕獲的邏輯專用硬件可實現最高性能。例如,定序器可以比軟件中實現的相同邏輯快一個數量級。由于分立邏輯器件占用大量空間和功率,因此添加FPGA是一種可行的替代方案。在許多情況下,FPGA和微控制器的組合是一個很好的解決方案。當微控制器在FPGA的邏輯中實現時,可以實現更密集的解決方案。作為硬編碼的宏,或者在每個新設計中被替換和布線的軟宏,整個微控制器吸收到FPGA的房子不僅可以產生最高的密度,而且可以產生最大的靈活性,特別是如果你足夠勇敢地修改核心以提高性能。本文著眼于在現有FPGA中快速運行的微核。這些可以從各種來源獲得,包括開放和封閉,免費和IP許可。

比原始版本更好

可以使用傳統架構和專有架構,每種架構都有優勢。傳統內核與傳統微處理器兼容,并提供熟悉的體系結構。您公司生產的產品可以使用已經過測試和驗證的代碼。當需要下一代產品甚至是新的改進模型時,組織良好且可靠的代碼庫的可重用性可以節省大量時間。

幾種流行的內核已經以原始邏輯形式實現了各種各樣的FPGA系列包括諸如Microchip PIC,Intel 8051,Atmel AVR,Motorola 6502,Intel 8080和Zilog Z80微控制器等處理器。一個不那么明顯的優點是能夠改進初始化建筑。如果時間和資源允許,可以克服缺點,因為您可以修改設計。例如,非常流行的8051架構最初采用有序架構,每條指令需要12個時鐘周期。精確的傳統實現可以反映初始功能,或者可以實現更現代的風格,減少每條指令的時鐘周期數。

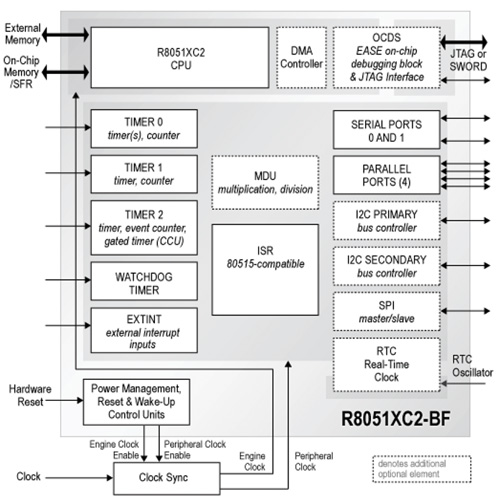

改進的8051 IP內核也可用于跨平臺開發。 R8051XC2-BF核心1可用于ASIC或Xilinx和Altera FPGA;它通過添加第二個數據指針(初始設計的缺點)和JTAG調試接口(圖1)改進了初始設計。

圖1:傳統核心的商業可用實現通常會改進初始的離散設計。這個8051內核每個指令運行一個時鐘,并添加JTAG和第二個數據指針。

ARM內核雖然許多設計可以使用8位內核,但現代功能可能需要更高的總線寬度來簡化處理。如果您正在操作24位寬的圖形數據,則單個32位傳輸比三個8位傳輸更有效。

最流行的32位架構也許是ARM?Cortex?,令人驚訝的是,它已成為FPGA實現的流行且受到良好支持的架構。從面積和功耗角度來看,ARM Cortex非常高效。可擴展的架構得到眾多工具和開發套件的很好支持,以及外圍設備,內存管理,數學和DSP功能的開源代碼。

ARM內核的一個很好的特性是它們不屬于一個FPGA制造商,可以在不同制造商的設備上實現。這意味著隨著設計的發展或需求的變化,您不會被鎖定在一個供應商中。另一個好處是,架構可以從更簡單,功能更少的Cortex M0擴展到非常高端的多核A8和A9風格。此外,還具有經過賽道驗證的驅動程序和堆棧,可用于高端外設,如USB,以太網,Wi-Fi,ZigBee,藍牙等。

Xilinx系列產品是嵌入式微核的大支持者,而ARM架構也不例外。像XC5VLX50-1FFG676C這樣的器件是XilinxVirtex?5系列的一部分,它是一個非常大,密集,高端的FPGA的例子,它可以在芯片上安裝一個快速而密集的系統。 550 MHz器件具有440個I/O和超過46,000個邏輯模塊,不僅支持ARM內核功能,還支持高達72位寬的存儲器寬度,流水線操作,FIFO,具有高達16.4 Mbits內部塊存儲器的雙端口存儲器和DSP功能。

Microsemi是另一家提供ARM內核支持的FPGA制造商,ProASIC3系列是一款優秀的目標技術,具有令人印象深刻的低端到高端邏輯,I/O,RAM和門數15,000到3,000,000。一個很好的例子是A3PE3000-FGG484具有341個I/O和516 Kbits的內部RAM。

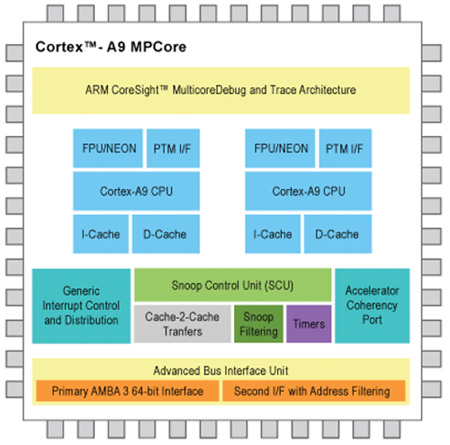

Altera具有可比較的部件,如EP3SL50F780C4N,它同樣支持ARM核心處理器,并為DDR,DDR2,DDR3,SDRAM提供內存支持更多,最多24個模塊化I/O bank,448 I/O(系列中最多744個)。作為Stratix?III系列的成員,Altera可以訪問Altera Mega-Function合作伙伴計劃(AMPP),以獲取可用的外設,內核和支持。 Altera還通過其Altera MegaCore功能支持多種知識產權(圖2)。

圖2:高端32位ARM架構是許多FPGA的流行核心。該Altera版本增加了多核調試和跟蹤功能,簡化了單個FPGA內多個實例化處理器內核的設計。

專有內核

除了行業標準的微控制器內核外,FPGA制造商還提供專有內核,這些內核具有非常高的邏輯效率,可擴展至8至32位的性能水平。這些供應商的關鍵不是在不需要的功能和外圍設備上浪費邏輯;經常縮減,實現了裸機處理單元,以提供基本的可編程性和FPGA內部大型邏輯池的接口。這不僅可以讓內核快速運行,而且還可以保持它們足夠小,以便在SoC內部創建自己的雙核,四核甚至八核處理器。

Xilinx指定Blaze這樣的內核,可以同時使用PicoBlaze和MicroBlaze口味。 PicoBlaze是一種8位RISC架構,具有高達240 MHz的性能。它主要設計用于VHDL設計流程,并作為VHDL源文件提供。一旦在13個不同的Xilinx系列中實現,它就不需要外部元件,完全在主機部分內部運行。

支持的系列包括Kinetex-7,Artix-7,Virtex(4,5,6,7,II-Pro) )和Spartan?(3和6)。從資源和復雜性的角度來看,PicoBlaze是Spartan(雙關語)。它具有一個16 x字節寬的通用數據寄存器,1K可編程片上程序存儲器(在FPGA配置期間自動加載),一個帶有CARRY和ZERO指示器標志的字節寬運算邏輯單元(ALU),64字節內部暫存器RAM,256個輸入和256個輸出端口,便于擴展和增強。另一方面,它具有可預測的性能,每條指令總是兩個時鐘周期,高達240 MHz(或Virtex-4中的100 MIPS) FPGA)和88 MHz(或Spartan-3 FPGA中的44 MIPS)。 PicoBlaze對Xilinx用戶免費提供,并附帶匯編程序和VHDL源代碼。

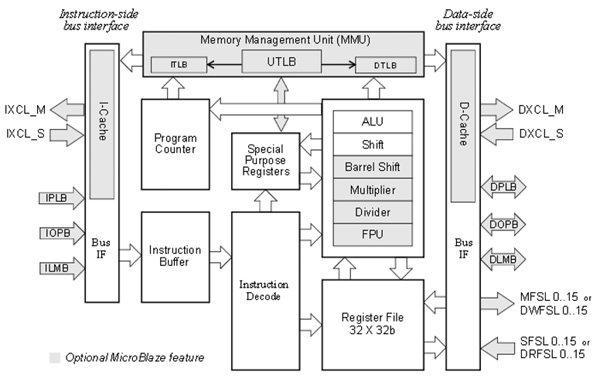

高端是Xilinx MicroBlaze。這是一個32位RISC Harvard架構軟核處理器內核,具有32個通用32位寄存器,ALU,針對嵌入式應用優化的豐富指令集,三級MMU/MPU支持等。

靈活性該核心(圖3)允許您選擇性能優化的五級流水線,使用Kinetix-7系列(例如XC7K70T-1FBG676C)或3級流水線區域優化版本可實現高達317 DMIPS在Xintex-7或Virtex-6和7系列器件(如XC6VLX130T-1FFG784C)上仍然可以達到令人尊敬的264 DMIPS。

圖3:用于Xilinx FPGA的專有32位MicroBlaze內核有條件編譯指令允許你添加你需要的塊,并消除你不保存邏輯和提高密度的塊。

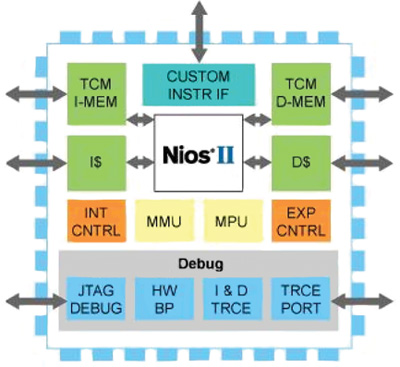

Altera還提供了一個名為NIOS的專有內核,現在是第二代NIOS II版本(圖4) 。作為業界使用最廣泛的軟處理器,它具有功率靈敏度和安全關鍵(DO-254)兼容性的實時性能。

圖4:Altera的第二代NIOS II內核被譽為FPGA中使用最廣泛且支持的IP內核,并帶來了許多開發和調試功能。

六級流水線NIOS內核可以實現少至600個邏輯單元和特征向量中斷控制,緊密內存和DSP耦合,以及添加自定義指令(最多256個)的能力。它可以使用內存管理單元(MMU),并在開源和商業支持的版本中支持嵌入式Linux。

可行的替代方案

您的設計細節將決定您是應該選擇硬宏還是軟宏。硬宏占用FPGA內部的特定位置和資源,但硬編碼宏的特性更好,可以實現更好的性能。

軟宏也可以實現良好的性能,特別是如果你足夠勇敢修改,改進,或平行他們。一如既往,良好的設計實踐將產生最佳結果。總之,當需要盡可能高的密度和/或性能時,選擇FPGA內部的軟處理器而不是傳統的微控制器及其所有支持電路可能在靈活性,效率,性能,功耗和空間方面,這是一個更好的解決方案。

-

微控制器

+關注

關注

48文章

7552瀏覽量

151417 -

FPGA

+關注

關注

1629文章

21736瀏覽量

603319 -

mcu

+關注

關注

146文章

17148瀏覽量

351186

發布評論請先 登錄

相關推薦

FPGA VI中不同的Xilinx內核生成器IP設計實現與子模板說明

在Xilinx FPGA上單源SYCL C++實現運行的方法

在Nimbix云加速工作流中實現FPGA開發和運行

MCU之SWM在KEIL環境中實現代碼在RAM中運行

在FPGA中實現MCU內核的快速運行

在FPGA中實現MCU內核的快速運行

在FPGA中實現MCU內核的快速運行

評論