許多設計人員遲早都會發現,微控制器或微處理器上運行的固件可能會變得太慢。現場可編程門陣列 (FPGA) 為此提供了一種可編程方法,以硬件速度來解決高速、實時、嵌入式設計問題。然而,為了最大限度地利用 FPGA,傳統上涉及到一個技術學習曲線,但由于成本和期限壓力,許多工程師無法負擔這樣的學習曲線。

FPGA 的學習曲線常常涉及學習新的編程語言(Verilog 或 VHDL),下載大型開發工具包,學習全新工具開發流程以生成 FPGA 比特流,而且可能要花大量資金(可能數百或數千美元)用于購買 FPGA 開發板。由于這些障礙,盡管 FPGA 是嵌入式設計工具箱中極其有用的工具,但許多設計工程師都避免使用它們。

一些供應商試圖通過提供入門 FPGA 板來減少使用 FPGA 的障礙,但學習新硬件描述語言和開發工具的必要性仍然是很高的門檻,阻礙了 FPGA 的更廣泛采用。為了破除這些障礙,Arduino 作出了最新的努力,推出一款名為 Arduino MKR Vidor 4000 的新型低成本開發板,其代表了一種在嵌入式系統設計中使用 FPGA 的獨特方法。

Arduino MKR Vidor 4000 提供了多種 FPGA 編程方法,這些方法可無縫集成到廣受歡迎的 Arduino IDE 中。借助這種方式,通過特殊的 Arduino 庫擴展獲得 FPGA 級性能,便能使嵌入式系統開發人員直接從 Arduino 草圖中快速獲益。同時,隨著更高級的設計人員對該技術的信心增強,他們可以采取更復雜的 FPGA 使用模型。

本文將首先討論有關 FPGA 的需求,再介紹 MKR Vidor 4000 開發板的功能。然后,本文將深入闡述如何應用 Arduino 的新型簡化方法來使用 FPGA。

第一代 Arduino 開發板

2005 年推出的第一款 Arduino 開發板是基于一個簡單的 8 位微控制器:Atmel(現為 Microchip Technology)AVR。此開發板的很多后續產品同樣基于該微控制器系列的不同器件。由于成本低且 Arduino IDE 簡單易用,Arduino 開發板系列已成為物聯網 (IoT) 產品開發的流行平臺,常用于 STEM/STEAM 項目。事實上,最初的 Arduino 板就是第一個獲得廣泛成功的開源硬件項目。

現在,全世界有成千上萬的設計師、工程師、開發人員和創客在使用各種版本的 Arduino 開發板系列,其已成為讓學生們第一次接觸嵌入式編程的首選。人們的創意無限,從音樂、游戲、玩具、智能家居、農業到自主駕駛車輛,其應用范圍非常廣泛。

隨著 Arduino 用戶不斷將最初的 Arduino 架構推進到越來越復雜的應用領域,性能問題開始出現。一部分問題是最初的 Arduino 微控制器的 8 位架構過于簡單。另一部分問題是許多實時外設的軟件實現,尤其是時間關鍵型外設,例如高速定時器、高頻 PWM(脈沖寬度調制)輸出和正交編碼器。這個問題的一種解決辦法是使用速度更快、功能更強大的微控制器,但最終軟件在實時環境中能做的事情是有限的。一些高速實時功能必須在硬件中實現。

Arduino 和 FPGA 結合

挑戰在于讓使用 Arduino 的嵌入式開發人員能使用 FPGA 資源,但又不破壞 Arduino 的簡易性。Arduino 從硬件角度解決了這一挑戰:將 FPGA 添加到 Arduino 架構中,使得 FPGA 可通過 Arduino 庫擴展 Arduino 的微控制器外設資源。現有 Arduino 用戶很熟悉這些庫;當使用 Arduino 的原生外設時,以及向 Arduino 擴展排針添加外設板時,經常會使用這些庫。

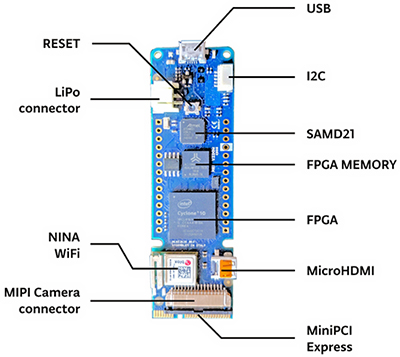

由此產生的 Arduino 開發板稱為 MKR Vidor 4000,其結合了基于 32 位 Arm? Cortex?-M0+ 處理器內核的 Microchip Technology SAMD21 低功耗微控制器的處理能力與 Intel(前身為 Altera)Cyclone 10 10CL016 FPGA(圖 1)。

圖 1:Arduino MKR Vidor 4000 開發板基于 Microchip SAMD21 微控制器和 Intel Cyclone 10 FPGA。(圖片來源:Arduino)

該 FPGA 包含 15,408 個可編程邏輯單元、516,096 比特的嵌入式 RAM 和 56 個 18 x 18 位硬件乘法器,可用于實現高速 DSP。每個 FPGA 的 I/O 引腳切換速度快于 150 兆赫茲 (MHz),這比板載 SAMD21 微控制器的 I/O 速度要快得多。簡而言之,板載 FPGA 為 Arduino MKR Vidor 4000 板提供了可觀的處理和 I/O 能力。

Arduino MKR Vidor 4000 屬于 Maker Arduino 板系列,其新式 MKR 外形尺寸與之前的 Arduino 板不相符。MKR 系列還包括:

Arduino MKR WAN 1300 連接板,帶有用于物聯網應用的板載 LoRa 射頻模塊

Arduino MKR GSM 1400 連接板,帶有板載蜂窩 RF 模塊,適合于需要全球 GSM 連接的物聯網應用

與之前的 Arduino 開發板一樣,Arduino 的 MKR 系列不僅是針對初學者而開發,專業人員同樣可以使用它來快速開發系統原型。Arduino 組織發現越來越多的正規工程項目使用 Arduino 開發板進行原型開發甚至生產,因而開發了該系列板。

Arduino MKR Vidor 4000 包括許多外設,其中有幾個是較早期、較簡單的 Arduino 所不曾涉及的。有一個 28 針 MKR 排針接口,其與最初的 Arduino 擴展板排針在概念上相似,但在物理上不同。該排針接口中的 I/O 引腳可由 SAMD21 微控制器或 Intel Cyclone 10 FPGA 控制。除了標準化 MKR 排針接口外,Arduino MKR Vidor 4000 板上的外設端口列表還包括:

與 Raspberry Pi 相機模塊兼容的 MIPI 攝像機連接器

采用 U-BLOX NINA-W102 射頻收發器模塊實現的 Wi-Fi 和 BLE(低功耗藍牙)RF 接口

MiniPCIe 連接器,具有多達 25 個用戶可編程引腳

請注意,Arduino MKR Vidor 4000 開發板沒有真正的 PCIe 接口端口。它只是改造了與 MiniPCIe 端口相關的連接器,在 MiniPCIe 邊緣連接器上分接出 Cyclone 10 FPGA 的許多 I/O 引腳。這是一種經濟實惠的大容量連接器,現已廣泛應用于數以百萬計的 PC 主板中,這足以證明其可靠性。MiniPCIe 連接器可用來輕松地將 Arduino MKR Vidor 4000 板插入更大的系統或 I/O 擴展板中。

盡管有如此多的 I/O 連接器,Arduino MKR Vidor 4000 開發板卻很小。其尺寸為 83 mm(3.25 英寸)× 25 mm(0.98 英寸),這樣便適合安裝在嵌入式計算應用越來越常見的狹小空間中。該板的電流消耗額定值為 100 毫安 (mA),因此應當也適合許多嵌入式系統項目的功率包絡,其中包括電池供電系統。

該板有一個用于直接連接 3.7 伏鋰聚合物 (LiPo) 電池的連接器,如圖 1 所示。但是,電流消耗將取決于 FPGA 中實現的功能以及實例化硬件的運行速度,這會使電池容量的計算變得復雜,最終將需要進行一些實驗才能確定電池的正確大小。

MKR Vidor 4000 板的視頻輸出是由 Intel Cyclone 10 FPGA 生成的真正 HDMI 視頻輸出。Arduino MKR Vidor 4000 板的 Arduino IDE 中包含了 Adafruit GFX 圖形核心庫,這允許 SAMD21 微控制器使用 Arduino 草圖在軟件控制下生成圖形。

此外,Arduino 還通過兩個專門為 MKR Vidor 4000 板創建的主庫向 Arduino IDE 添加了幾個硬件 IP 塊:VidorPeripherals 和 VidorGraphics。當 Arduino 草圖中包含相關外設庫時,Arduino MKR Vidor 4000 上的 Intel Cyclone 10 FPGA 會自動構建這些硬件 IP 塊。目前的外設 IP 塊清單包括:

I2C 端口

SPI 端口

高頻 PWM 控制器

高速定時器

高速正交解碼器

Adafruit Neopixel 可尋址 RGB 智能 LED 控制器

同樣,Arduino MKR Vidor 4000 板的軟件庫包含用于該板 MIPI 攝像頭輸入的視頻捕獲代碼。此庫中的例程可以從連接的攝像頭中捕獲 640 x 480 像素視頻圖像。攝像頭的 24 位 RGB 圖像存儲在開發板的 8 MB SDRAM 中,該 SDRAM 直接連接到 Cyclone 10 FPGA。此外,可以使用 Arduino MKR Vidor 4000 板的其中一個 I2C 接口訪問所連攝像頭的控制和狀態寄存器。

其中一些外設(例如 I2C 和 SPI)已經作為軟件 IP 塊用于早前的 Arduino 板。這些早期軟件實現與 Arduino MKR Vidor 4000 板的 FPGA 上實現的等效 IP 塊的區別在于,FPGA 版本的外設性能更好。

例如,每個 I2C 和 SPI 實例化都是通過板上 FPGA 內部的獨立可編程硬件塊實現的。因此,實例化若干個這樣的串行端口時沒有性能損失。

FPGA 速度示例:快速正交編碼

正交編碼器常用作 3D 打印機所用步進電機的定位反饋機制。基于軟件的編碼器可能會出現問題,因為其速度有限;當處理器忙于執行其他代碼時,這些編碼器可能會錯失計數。Arduino MKR Vidor 4000 板的正交編碼器是在 Cyclone 10 FPGA 硬件中實現實例化,其時鐘頻率為 100 MHz,并采用 32 位硬件計數器實現,因此在任何實際物理系統中都不會錯失計數。

每個實例化的正交編碼器都利用單獨的 FPGA 塊實現,因此實例化多個編碼器時不會有性能損失。若要實現更多編碼器,只需要使用 FPGA 的更多內部可編程邏輯。這是 FPGA 硬件并行性的關鍵優勢。

輕松使用 FPGA — Arduino 方式

通過以 FPGA 硬件實現外設塊,并借助無數 Arduino 草圖編寫人員已經熟悉的相同庫機制使其可用,Arduino MKR Vidor 4000 板簡化了 FPGA 的使用。無需學習 VHDL 或 Verilog 之類新的硬件描述語言 (HDL)。對于開發人員來說,基于 FPGA 的外設與程序員眼中的任何其他 C++ 對象并無二致。Arduino 計劃日后添加更多此類硬件 IP 塊外設。

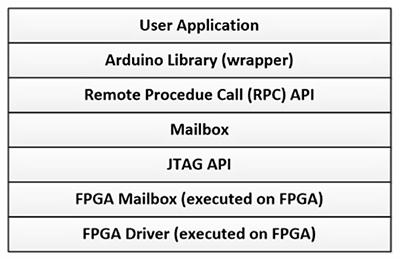

Arduino 已經完成了這個魔法,通過使用的軟件堆棧遠遠低于最初 Arduino IDE 的軟件堆棧,讓 FPGA 硬件看起來就像硬件化的外設塊。MKR Vidor 4000 板的軟件堆棧使用遠程過程調用在 Arduino C++ 版本編寫的高級草圖與開發板的 FPGA 硬件之間建立鏈接;這些過程調用發送到 FPGA 上實例化的郵箱,而 FPGA 通過 JTAG 連接到 SAMD21 微控制器(圖 2)。

圖 2:Arduino MKR Vidor 4000 開發板的軟件堆棧使用遠程過程調用,其通過 JTAG API 傳輸到 Intel Cyclone 10 FPGA,而 FPGA 可編程硬件上實例化了一個 Arduino 驅動器。(圖片來源:Steve Leibson)

使用此軟件堆棧訪問基于 FPGA 的外設非常簡單,只需正確調用適當的 Vidor 外設庫即可。Arduino 草圖編寫人員不必知道 Vidor 的 FPGA 魔法工作原理。它切實有效。

要借助 FPGA 提升系統性能,一種有效的方法當然是訪問利用可編程硬件實現的預定義外設 IP 塊,不過這樣獲得的性能提升僅僅是 FPGA 全部能力的一小部分。盡管如此,Arduino 仍然鼓勵 MKR Vidor 4000 用戶開發更多外設塊,以便通過龐大的 Arduino 開源社區擴大選擇范圍。

然而,Arduino MKR Vidor 4000 板還不是通用的 FPGA 開發板,因為它不支持使用 HDL 代碼對板載 Cyclone 10 FPGA 直接編程。不過,Arduino 還計劃發布一個 Intel Quartus 項目,演示直接在 MKR Vidor 4000 板上實現 FPGA HDL 代碼,從而讓更多高級用戶可以通過 Arduino MKR Vidor 4000 板的 FPGA 來實現更多用途。Quartus 是一款全面的 HDL 開發工具,Intel 將其提供給設計人員開發采用該公司 FPGA 的 FPGA 設計。

當 Arduino 為 Arduino MKR Vidor 4000 板發布此 Quartus 項目時,想要學習 HDL 編程的設計師、工程師、創客和學生們將能把該板用作更高級 FPGA 項目的低成本開發與生產平臺。借助這種直接 FPGA 編程功能,設計人員將能在 Arduino MKR Vidor 4000 板的 FPGA 中實例化幾乎任何類型的硬件塊。例如,板載 FPGA 資源足以在 FPGA 結構中容納 Arm Cortex-M1 處理器內核。這樣做將會把 Arduino MKR Vidor 4000 板變換成雙處理器嵌入式系統。

總結

雖然 FPGA 與微控制器或微處理器一起能為許多處理功能提供更高的性能,但這需要很長的學習曲線。Arduino MKR Vidor 4000 板和配套的 Arduino IDE 大大降低了學習如何使用 FPGA 開發更高級應用的門檻。想要了解 FPGA“水有多深”的設計人員可能會發現,Arduino MKR Vidor 4000 這個池塘中的水不深也不淺,剛剛合適。

-

微控制器

+關注

關注

48文章

7544瀏覽量

151325 -

FPGA

+關注

關注

1629文章

21729瀏覽量

603026 -

微處理器

+關注

關注

11文章

2259瀏覽量

82406

發布評論請先 登錄

相關推薦

正點原子fpga開發板不同型號

正點原子和野火開發板哪個好

正點原子的stm32開發板能用stlink嗎

ARM開發板與FPGA的結合應用

linux開發板與樹莓派的區別

linux開發板和單片機開發的區別

FPGA核心板 Xilinx Artix-7系列XC7A100T開發平臺,米爾FPGA工業開發板

fpga開發板與linux開發板區別

如何使用FPGA開發板編程出更高級的應用

如何使用FPGA開發板編程出更高級的應用

評論