隨著“Alexa”、“Hey Siri”或“Hi Google”等多個產品成功響應關鍵詞,關鍵字檢測 (KWS) 已成為越來越多嵌入式應用的一項重要要求。雖然典型的先進 KWS 解決方案依賴于復雜的卷積神經網絡 (CNN) 和其他深度神經網絡 (DNN) 機器學習算法,但資源受限型產品的開發人員可以使用二值神經網絡 (BNN) 獲得所需的準確結果。

本文介紹了將 KWS 添加到可穿戴設備和其他低功耗物聯網設備的優勢,以及所面臨的各項挑戰。在描述 BNN 架構及其為何適用于資源受限型 KWS 應用之后,本文還介紹了一種通過低功耗 FPGA 實現 BNN 的可用解決方案。該解決方案將用于展示如何利用一小部分 CNN 資源要求,為低功耗 KWS 應用實現 CNN 的高精度。

KWS 的起源和演進

KWS 也被也稱為關鍵詞檢測,多年來一直應用于信息處理應用。例如,在文檔處理中,KWS 提供了一種更有效的光學字符識別替代方法,可為大規模數字化文檔編制索引。隨著聲控服務在智能手機、手表、家用產品等設備中變得可用,基于語音的 KWS 方法在產品開發中迅速獲得關注。在這些產品中,“始終運行”功能允許產品連續處理音頻輸入,尋找可激活基于語音的用戶界面的關鍵字。

諸如 XMOS VocalFusion 4-Mic 套件之類板級產品可與 Amazon 語音服務完全集成,提供了一種即用型解決方案,可在許多應用中添加語音助手服務。但對于功率預算有限的可穿戴設備或其他電池供電型產品,開發人員很大程度上只能去尋找自己的 KWS 解決方案。

過去,實現自定義 KWS 機制要求開發人員不僅在音頻工程方面具有深厚背景,而且在時間模式識別的統計方法應用方面也具有同樣的要求。過去幾十年來,基于隱馬爾可夫模型和相關算法的統計方法為字識別解決方案提供了基礎。

最近,像卷積神經網絡 (CNN) 這樣的 DNN 架構已經開始用作許多 KWS 應用的基礎。

滿足深度神經網絡 (DNN) 要求

DNN 架構基于多層神經元,這些神經元經過訓練,可從輸入數據中提取特征,并預測輸入數據對應于訓練期間所用類之一的概率1。特別是得益于這些算法實現的高識別精度,CNN 架構已成為圖像識別的卓越方法。

同樣,不同類型的 CNN 架構已經在包括 KWS 實現在內的語音處理中取得了成功。“傳統”CNN 架構的難點在于其尺寸和處理要求。例如,在圖像處理中,CNN 模型已經增長到數百兆字節的大小。大存儲容量加上廣泛的數值計算要求,對模型處理平臺提出了很高的要求。

用于實現傳統 CNN 架構的方法提供的幫助很少。CNN 和其他 DNN 算法通過對網絡中每層的每個神經元執行通用矩陣乘法 (GEMM) 運算,實現其精度。在訓練期間,當模型可能需要處理數百萬個標記的特征向量以獲得預期結果時,GEMM 和其他矩陣計算的數量可以很容易地達到數十億,從而推動了圖形處理單元 (GPU) 在此模型開發階段加速處理的需求。當部署模型以在應用中執行推理時,人們希望維持低延時和高精度,這繼續決定了在要求最為嚴苛的應用中對 GPU 的需求。

在具有較為適中的推理要求的應用中,開發人員可以通過犧牲延時和精度來部署傳統 CNN,即使在 Raspberry Pi Foundation Raspberry Pi 3 等通用平臺上,或基于 Arm? Cortex?-M7 的 MCU(例如 Microchip Technology、NXP 或 STMicroelectronics 的 MCU)上亦如此2。

但是,對于對推理準確性和延時提出嚴格要求的應用,傳統 CNN 算法在資源有限的平臺上根本不實用。CNN 提出的存儲器和處理要求遠遠超出了典型線路供電型消費產品內置的嵌入式系統的資源范圍,更不用說電池供電型可穿戴設備或其他預期提供“始終運行”的KWS 功能的移動設計。模型壓縮技術的發展需要 DNN 算法能夠支持這些平臺。

高效的 DNN 方法

為了解決呈螺旋上升的模型尺寸問題,機器學習科學家已經找到了在無顯著精度損失的情況下大幅降低存儲器需求的方法。例如,研究人員修剪了對結果貢獻很小的內部網絡連接。他們還將內部參數所需的精度降低到 8 位甚至 5 位值。通過應用上述方法和其他方法,他們在無明顯精度損失的情況下,將行業黃金標準 CNN 模型的尺寸減小 30 倍至 49 倍,從而減少了存儲器需求3。

除了降低存儲器需求外,模型壓縮技術還有助于降低處理要求:修剪減少了所需計算次數,而精度降低則加快了計算速度。

但是,即使降低了精度,這些網絡仍需要大量屬于機器學習算法核心的 GEMM 運算。這些運算的范圍不僅推動了對推理平臺高性能硬件的需求,而且還直接影響了這些平臺的功率預算。饋送這些矩陣運算需要大量訪問存儲器,單是這方面的功耗,就輕易超過電池供電型設備的功率預算。

為了解決移動設備的存儲器、處理和功耗限制,研究人員已將模型壓縮的概念擴展到極致。研究人員將模型參數量化為 +1 或 -1(或 0)值,以建立稱為二值神經網絡 (BNN) 的架構,而不是簡單地將內部參數的精度降低到 8 位或更低位。

BNN 如何將 KWS 引入資源有限的設計

在基本拓撲方面,BNN 與 CNN 大致相同,并且所含層類型相同(包括卷積層、歸一化層、激活層和池化層)。這些層內使用 1 位參數(權重與偏置值),在運算上差異巨大。

BNN 不是執行傳統 CNN 中所需的 32 位浮點 GEMM 運算,而是可以使用更簡單的按位 XNOR 運算。雖然這種方法可能導致訓練時間延長,但研究人員發現,BNN 模型的準確率幾乎與使用 32 位浮點值的模型相當4。二進制化參數的使用不僅減少了 BNN 的存儲器占用空間,而且還減少了其存儲器訪問要求,因為可以在單字訪問周期中獲取多個 1 位參數,并且饋送 XNOR 運算所需的參數更少。

BNN 的計算簡化后,處理要求也隨之顯著降低。因此,BNN 可以在不顯著影響精度的情況下,實現比先前方法更高的推理率。在一項研究中,研究人員比較了在 Xilinx XC7Z020 FPGA 片上系統 (SoC) 上實現 CNN 和 BNN 的性能,其中該片上系統在基于 XC7Z020 的開發平臺(如 Digilent 的 ZedBoard)上運行。使用 XC7Z020 FPGA 后,兩個 DNN 均實現了高效性能,但 CNN 實現了每瓦特 7.27 每秒十億次運算 (GOPS),而 BNN 在相同零件上的數據為 44.2 GOPS/瓦5。

由于其可編程性和高能效,FPGA 已成為使用 CNN 的應用(如嵌入式視覺)的熱門推理平臺6。先進的 FPGA 組合了嵌入式存儲器和多個并行處理數字信號處理 (DSP) 單元,可加快 GEMM 和其他矩陣計算。雖然 BNN 需要的 DSP 資源僅是 CNN 所需的一小部分,但 FPGA 仍然非常適合這些架構。例如,開發人員可利用能夠加速此架構中二進制卷積或其他按位運算的專用邏輯,來增強其基于 FPGA 的 BNN。

但是,對于專注于大型應用的典型開發人員而言,即使縮短項目日程以適應快速發展的應用領域(如可穿戴設備和其他聲控連接產品),只要對基于 FPGA 的 DNN 進行優化設計,不論類型如何,都會造成拖延。Lattice Semiconductor 的 SensAI? 技術堆棧通過專門的 DNN IP、參考設計、設計服務以及用于實現推理模型的簡單 FPGA 開發工作流程消除了這一障礙。

基于 FPGA 的 BNN 解決方案

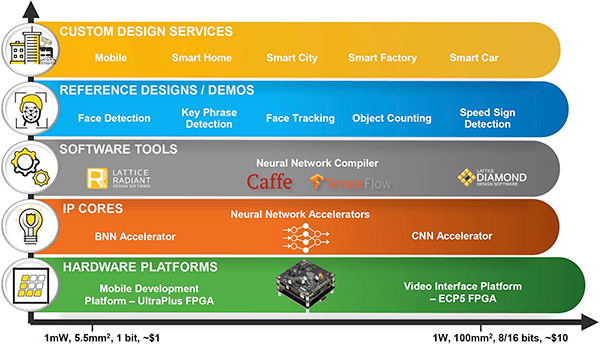

SensAI 將 DNN IP 與神經網絡編譯器結合在一個工作流程中,旨在加快實現通過行業標準機器學習框架(包括 Caffe 和 TensorFlow)創建的神經網絡模型(圖 1)。

圖 1:Lattice SensAI 技術堆棧可幫助開發人員使用通過標準機器學習框架創建的 CNN 和 BNN 模型,在 Lattice iCE40 UltraPlus 和 ECP5 FPGA 上實現低功耗推理引擎。(圖片來源:Lattice Semiconductor)

Lattice 的 CNN IP 旨在與 Lattice ECP5 FPGA 配合使用,支持在 Lattice 基于 ECP5 的嵌入式視覺開發套件上運行 1 W 或更低功耗的高性能圖像識別功能。但是,對于資源受限的設計,Lattice 的 BNN IP 使開發人員能夠充分利用這種高效架構,在低功耗 Lattice ICE40 UltraPlus FPGA 上實現推理引擎。

使用 Lattice BNN IP 后,這些基于 ICE40 UltraPlus 的推理引擎可以在顯著降低運行功耗、使用更少存儲器和處理資源的情況下實現高精度。Lattice 通過 KWS 推理模型的完整 ICE40 UltraPlus FPGA 實現,展示了此 BNN IP 的效率,其中推理模型實現在 Lattice 移動開發平臺 (MDP) 上的運行功耗約為 1 mW。

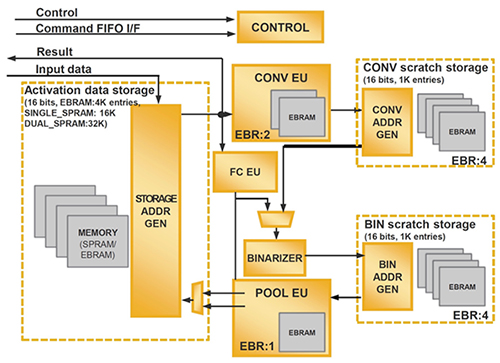

Lattice SensAI BNN IP 包括實現 BNN 推理解決方案所需的全套模塊(圖 2)。

圖 2:Lattice SensAI IP 提供了在 Lattice iCE40 UltraPlus FPGA 上實現 BNN 解決方案所需的全套模型層、存儲器子系統、控制邏輯和系統接口。(圖片來源:Lattice Semiconductor)

除了支持卷積、池化和其他 DNN 層功能外,該 IP 還有多個存儲器子系統,包括用于訓練期間所開發模型的固定參數和推理期間所執行計算的中間結果的子系統。除了輸入、輸出和控制線的接口邏輯外,該 IP 還提供了一個控制子系統,用于處理實現模型操作的命令序列。

對于新項目,開發人員使用 Lattice Radiant 軟件包中的一些簡單菜單為其特定設計生成基本 IP 內核。這里,開發人員只需使用 Radiant IP 配置向導中提供的菜單選項,為所需存儲器(8、16 或 64 KB)和二進制類型(+ 1/-1 或 +1/0)配置 BNN IP 塊。開發人員通過使用另一個 Radiant 菜單來完成此簡單設置過程,生成 RTL 和其他支持文件,Radiant FPGA 程序員使用這些文件,根據其所選 BNN 配置對設備進行編程。

雖然此 FPGA 編程工作流程為 BNN 模型提供了底層執行平臺,但模型本身的編程遵循 SensAI 環境中的單獨路徑。

在 SensAI 工作流程的模型開發部分,開發人員使用 Lattice 神經網絡編譯器將 Caffe 或 TensorFlow 模型轉換成相應文件,這些文件包含在所配置 BNN 核心上實現這些模型所需的模型參數和命令序列。在最后一步中,開發人員使用 Radiant 將模型文件和 FPGA 比特流文件加載到 FPGA 平臺中。

KWS 實現

Lattice 利用了一個旨在運行于 Lattice MDP 之上的基于 BNN 的完整 KWS 模型演示此 BNN 開發過程。MDP 本身就是一個出色的平臺,結合了 iCE40 UltraPlus FPGA 和一系列可能在典型低功耗移動應用中遇到的外設。

此開發板集成了四個 iCE40 UltraPlus 器件,在演示該板內置的 1.54 英寸顯示屏、640 x 480 圖像傳感器和 RGB LED 的應用中,每個器件都有展示。該板還包含一整套傳感器,包括壓力傳感器、羅盤傳感器、3 軸線性加速計、3D 加速計和 3D 陀螺儀。針對像關鍵字檢測這樣的音頻應用,該電路板還包括兩個 I2S 麥克風和兩個 PDM 麥克風。對于要求更高的應用,開發人員可以將 Lattice 的 8 麥克風 LF-81AGG-EVN 子板插入 MDP,以支持音頻波束形成,從而在聲控應用中增強方向響應(圖 3)。

圖 3:Lattice 移動開發平臺 (MDP) 集成了一套廣泛的支持功能和外設,同時為 8 麥克風陣列(圖中顯示為與 MDP 相連)等擴展組件提供連接器。(圖片來源:Lattice Semiconductor)

該開發板的內置電源管理電路允許開發人員采用內部鋰離子電池實現獨立操作,或采用外部電源為該板供電。在開發過程中,可通過主機開發平臺 USB 連接為該板供電。此主機可運行 Lattice iCEcube2,用于創建自定義設計,或運行 Lattice Radiant 編程器,以使用像 Lattice 關鍵詞檢測演示這樣預先建立的設計對板載 iCE40 FPGA 進行編程。

Lattice DNN 演示(包括用于關鍵字詞檢測的演示)提供了一整套常規情況下通過 SensAI 工作流生成的文件。因此,開發人員使用 Radiant 編程器即可加載這些文件,以評估模型的性能,例如關鍵字詞檢測演示中的 BNN 推理模型。

對于希望檢查實現細節的開發人員,演示項目還提供模型文件,包括 TensorFlow .pb 文件以及 Caffe .proto 和 .caffeemodel 文件。開發人員可以檢查這些模型以評估所提供的網絡設計。對于具有更多特殊要求的應用,這些模型可用作開發人員自有模型的起點。通常,設計人員會發現基于典型 CNN 類型設計的拓撲。

在 Lattice 關鍵詞檢測演示項目中,所提供的 BNN 網絡設計使用熟悉的拓撲結構,重復多個階段,每個階段包括卷積層、批量歸一化層、縮放層、ReLu 激活層和池化層(圖 4)。盡管與傳統的 CNN 設計在很大程度上無甚區別,但 Lattice BNN 實現采用內部二值參數和相關機制,這是此高效架構的核心。

圖 4:BNN 包含在 Lattice 演示項目中,使用一個由三個相似卷積模塊組成的流水線執行關鍵詞檢測,每個卷積模塊包括卷積層、批量歸一化層、縮放層、ReLu 激活層和池化層。(圖片來源:Lattice/Ethereon)

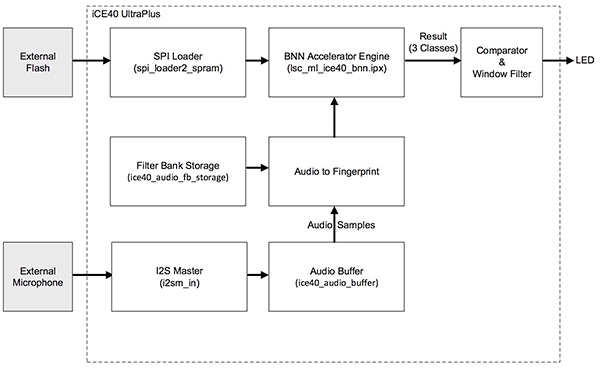

Lattice 演示使用用于管理從外部閃存加載的音頻流和命令序列的模塊,將此 BNN 推理模型實現為嵌入 FPGA 中的 BNN 加速器引擎實現(圖 5)。

圖 5:Lattice 關鍵詞檢測演示在單個低功耗 Lattice iCE40 UltraPlus FPGA 上實現了一個完整的 KWS 系統。(圖片來源:Lattice Semiconductor)

這里,I2S 主模塊接受來自外部麥克風的音頻數據,并將數據傳遞到音頻緩沖器。音頻到指紋塊進而從緩沖器中讀取音頻樣本,并使用從濾波器組存儲區讀取的濾波器生成基本音頻頻譜圖。此操作可提供合適的結果,且沒有傳統 FFT 頻譜圖的計算復雜性。

最后,BNN 加速器引擎使用此經處理的音頻流進行推理,產生三種可能的輸出:靜默、關鍵詞、無關鍵詞。

在配置好開發板并加載演示文件后,開發人員只需通過為 MDP 板供電并說出關鍵詞(在本例中為“seven”一詞)即可運行演示。當推理引擎檢測到關鍵詞時,FPGA 將打開 MDP 中的內置 RGB LED。

總結

機器學習功能強大,可為增強可穿戴設備和其他移動應用提供強大的解決方案,例如與聲控用戶界面配合使用的關鍵字檢測。雖然像 CNN 這樣的機器學習模型架構可以提供高度準確的結果,但是它們對存儲器、處理和功率的要求通常超出電池供電型設備的資源能力。

如本文所述,BNN 架構解決了這些問題。使用 Lattice Semiconductor 的先進機器學習解決方案,開發人員可以借助這一功耗僅約 1 mW 的 KWS 模型快速增強其設計。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603008 -

神經網絡

+關注

關注

42文章

4771瀏覽量

100715 -

機器學習

+關注

關注

66文章

8406瀏覽量

132565

發布評論請先 登錄

相關推薦

通過FPGA實現深度神經網絡的解決方案

通過FPGA實現深度神經網絡的解決方案

評論