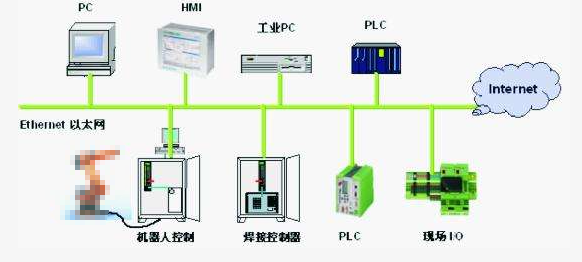

以太網在企業網絡中的主導地位使其在工業網絡領域具有明顯的優勢。在整個企業中使用單核協議可以使數據從工廠無縫地流向業務部門,從而可以更有效地管理生產計劃,最大限度地降低庫存成本并優化維護操作。

以太網不是為然而,工廠車間以及標準以太網的主要缺點是它無法提供許多工業應用所需的實時響應,例如過程和電機控制。幾十年來,諸如CAN(控制器區域網絡)和PROFIBUS(過程現場總線)之類的確定性協議主導了工業網絡。盡管這些協議仍然保持著相當大的市場份額,但幾年前以太網變體開始出現,提供了標準以太網所缺乏的實時性能。

為了合理化工業網絡中產生的非生產性多樣性,2001年開放設備供應商協會(OVDA)的成立是為了創建和維護通用工業協議(CIP)以確保某種程度的兼容性。從那時起,包括EtherNet/IP,DeviceNet,ControlNet和CompoNet在內的多種協議已在其協議棧的上層實現了CIP。現在有數百家供應商支持CIP。

EtherNet/IP是CIP在IEEE 802.3定義的標準以太網上實現的名稱。 EtherNet/IP中的“IP”代表工業協議。

EtherNet/IP技術

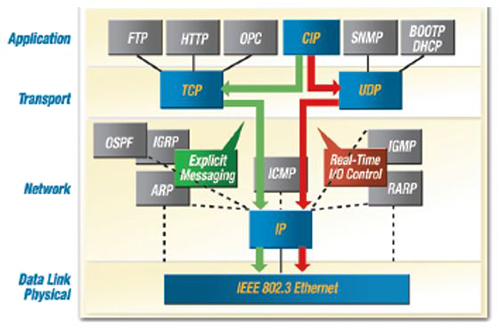

圖1顯示了如何使用CIP實現多標準環境。來自頂層CIP塊的紅色箭頭定義了通過UDP進行實時控制的路徑。綠色箭頭顯示標準IEEE 802.3以太網的路徑。總之,它們包含EtherNet/IP。可以使用現有的TCP/IP堆棧開發產品,或者在工業應用中,可以簡單地修改現有的Modbus接口以與PLC通信。

圖1:CIP完全兼容以太網和Internet協議(由開放設備供應商協會提供)。面向對象的編程模型

CIP使用對象模型來簡化軟件開發。在應用層中定義了與公共接口和行為相關的一組對象和設備配置文件。 CIP使用三類對象:應用程序對象,它定義表示設備數據的方法;定義以太網/IP特定功能的網絡對象以及如何配置IP地址等參數;和通信對象,它們創建了建立通信關聯和訪問設備數據和服務的方法。

CIP網絡上設備之間的端到端通信由CIP通信服務處理。由于EtherNet/IP將CIP通信服務映射到以太網和TCP/IP,因此可確保多廠商互操作性。

EtherNet/IP節點的組件

每個EtherNet/IP節點包含四個與OSI模型對應的層。它們如下:

物理層(PHY)。只要支持100 Mbit/s數據速率,就可以使用任何標準以太網介質(雙絞銅線或光纖)。

數據鏈路層將數據包從設備傳輸到設備并包含以太網/IP MAC,可以通過ASIC,FPGA或運行高速固件的定制硬件實現。

會話/傳輸層,處理TCP/IP以及真實的UDP/IP時間消息。 CIP對象定義也在此層中以啟用與應用程序層的通信。

應用程序層。在節點內部,應用程序可以在硬件上運行,也可以由嵌入式CPU實現的硬件/軟件組合運行。當然,應用程序必須支持基于EtherNet/IP的協議。

在實現EtherNet/IP節點時,設計人員可以選擇多種架構。只要節點完全由硬件實現,就可以使用ASIC,FPGA或板級解決方案。雖然這些簡單的數字I/O設備解決方案適用于對成本敏感的產品,但需要配置,監控和控制的應用通常也需要MCU。例如,傳感器通常由MCU控制。在EtherNet/IP節點中,MCU還可以實現設備驅動程序并運行EtherNet/IP協議棧。 ASIC或FPGA仍然是架構不可或缺的一部分。

嵌入式MCU實現

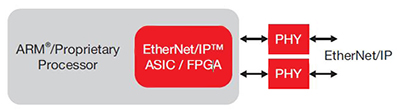

更復雜的架構將EtherNet/IP節點作為帶有集成CPU的MCU的外設實現。該架構如圖2所示。處理器可以使用FPGA中的可用門配置。

圖2:帶處理器的集成EtherNet/IP節點(由德州儀器公司提供)。不使用具有EtherNet/IP節點的MCU作為外設,而是可以反轉拓撲結構,并且MCU可以在實現EtherNet/IP節點的同一FPGA或ASIC上實現。從設計角度來看,這種方法需要仔細考慮嵌入式MCU所需的處理能力和時鐘頻率,既適用于目標應用,也適用于未來可能的設計旋轉。 FPGA實現也可能使滿足產品價格目標成為一項挑戰。無論如何實現,MCU都需要一些方法來執行與另一個嵌入式外設的實時操作。

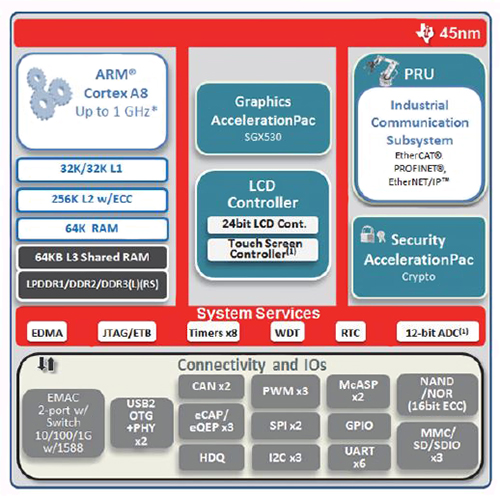

‘Sitara?例如,AM33x處理器通過可編程實時單元(PRU)解決了這個問題,它支持與兩個PHY收發器芯片的低級交互,這兩個PHY收發器芯片是圖2所示解決方案的一部分。使用固件,Sitara AM33X處理器將整個以太網MAC層封裝在PRU子系統中。

為了優化傳輸效率,EtherNet/IP節點僅處理專門發送給它們的數據包。中斷用于維護應用程序和ARM處理器之間的實時通信。由于幾乎所有的低級,高速EtherNet/IP功能都由PRU子系統處理,因此ARM處理器幾乎可以分配所有處理能力來運行堆棧和復雜的應用,如電機控制。

TI’s Sitara AM335x處理器采用ARM Cortex-A8處理器,工作頻率為275 MHz,適用于高達1 GHz的基本應用,適用于電機控制等高性能應用。

Sitara AM3352采用275 MHz(AM3352ZCE27),600 MHz(AM3352BZCZ60)和1 GHz(AM3352BZCZA100)版本。

圖3顯示了TI Sitara AM335x處理器的框圖。

圖3:Sitara AM335x框圖(由德州儀器提供)。

以太網PHY設備,如德州儀器的TLK110收發器完善了設計。 TLK110針對低延遲性能進行了優化。它還具有先進的電纜診斷功能,可以快速定位電纜故障。除了TI的解決方案,飛思卡爾半導體還為其幾個處理器系列開發了EtherNet/IP實現產品。 Molex的實時EtherNet/IP堆棧已移植到飛思卡爾的PowerQUICC和ColdFire處理器上。

軟件和固件

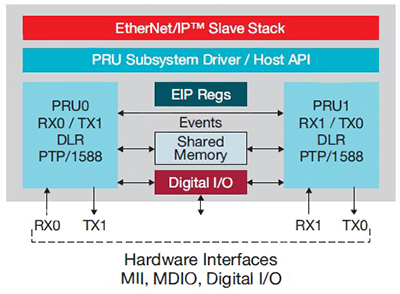

除硬件配置外,開發人員還應熟悉Sitara解決方案和固件架構等軟件。用于EtherNet/IP從站實現。軟件包含三個基本元素:

數據鏈路層功能微代碼,在PRU中實現

EtherNet/IP從屬協議棧和非IP/IP棧兩者都在ARM處理器上運行的實時通信

應用程序

使用兩個以太網堆棧,因為實時消息傳遞由UDP/IP和 - 來處理最大化效率 - 不經常的低優先級消息(例如綁定到業務單元的消息)由TCP/IP處理。

數據鏈路層中的固件包括兩個PRU,每個收發器一個。 PRU管理與兩個硬件接口的連接,并執行基本的以太網交換機協議,如MAC學習,風暴防御和數據包統計。兩個PRU使用一組特殊指令通過共享存儲器相互通信以確保協調。

由于冗余和同步是實時網絡中的重要屬性,因此Sitara固件還執行環形冗余協議(設備級環網或DLR)和IEEE的精確時間協議(PTP/1588)進行同步。采用TLK110的TI Sitara AM335x處理器的延遲小于2μs,這使其成為領先的EtherNet/IP從站解決方案。

固件架構如圖4所示。

圖4:固件架構(禮貌:德州儀器)。

EtherNet/IP設計

EtherNet/IP從站節點可以在TI的多個AM335x處理器上實現,這些處理器有多種工作頻率可供選擇。毫不奇怪,TI為此解決方案提供模擬產品。 TLK110以太網PHY芯片和TPS65910電源管理芯片都是任何EtherNet/IP從節點實現的理想選擇。

TI還提供全套工具和軟件代碼。 Sitara AM335x工業軟件開發套件(SDK)包括EtherNet/IP協議的固件,軟件驅動程序,硬件初始化程序,堆棧應用程序編程接口(API)的適配層以及EtherNet/IP協議棧。

對于硬件設計,TI開發了一款Sitara AM3359評估板,該評估板面向工業通信,可編程邏輯控制器(PLC)和運動控制系統。該套件的軟件包括TI的SYS/BIOS?實時內核,EtherNet/IP固件以及EtherNet/IP應用級堆棧的評估版。

該主板的主要組件是EtherNet/IP優化的PHY設備,調試硬件,SD/MMC,以太網和UART。附加組件包括用于特定應用,例如運動,電機和過程控制。該套件還可用于開發其他工業通信標準,如PROFIBUS,PROFINET-RT和CAN,以及POWERLINK,EtherCAT和SERCOS III等實時以太網標準。

TI還提供低成本Sitara AM3359工業通信引擎2板(TMDSICE3359),一種小型(70 x 90 mm)開發板,專為通信模塊,I/O設備,傳感器和類似應用而開發,包括EtherNet的基本外設/IP,PROFINET,PROFIBUS和EtherCAT通信標準。 SDK包括基于SYS/BIOS的實時內核,其中包含應用程序級通信堆棧和設備驅動程序。該平臺還包含開發和調試工具鏈。

-

處理器

+關注

關注

68文章

19275瀏覽量

229756 -

mcu

+關注

關注

146文章

17141瀏覽量

351102 -

以太網

+關注

關注

40文章

5421瀏覽量

171666

發布評論請先 登錄

相關推薦

利用LWIP 2.2實現以太網的DHCP功能

采用嵌入式MCU實現以太網在工業網絡領域的應用

采用嵌入式MCU實現以太網在工業網絡領域的應用

評論