在由北京未來芯片技術高精尖創新中心和清華大學微電子學研究所聯合主辦的第三屆未來芯片論壇上,清華大學正式發布了《人工智能芯片技術白皮書(2018)》。

《白皮書》首次整合了國際化的學術和產業資源,緊扣學術研究和產業發展前沿,對人工智能芯片技術進行了深入探討、專業闡述,完成了對AI芯片各種技術路線梳理及對未來技術發展趨勢和風險預判。

據悉,《白皮書》由斯坦福大學、清華大學、香港科技大學、***新竹清華大學,北京半導體行業協會及新思科技的頂尖研究者和產業界資深專家,包括10余位IEEE Fellow共同編寫完成。

無芯片不AI,新計算范式來襲

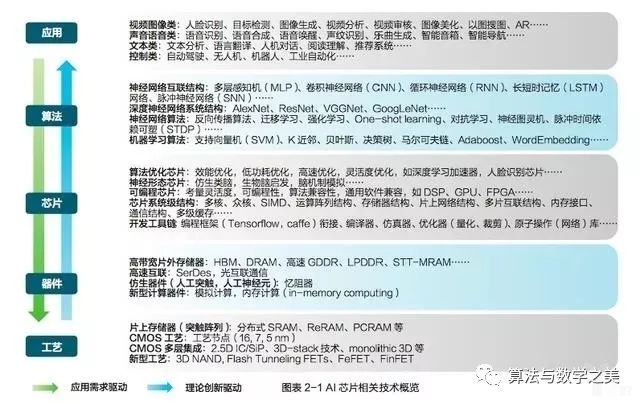

近些年隨著大數據的積聚、理論算法的革新、計算能力的提升及網絡設施的發展,使得持續積累了半個多世紀的人工智能產業,又一次迎來革命性的進步,人工智能的研究和應用進入全新的發展階段。

實際上,人工智能產業得以快速發展,都離不開目前唯一的物理基礎——芯片。可以說,“無芯片不AI”。

目前,關于AI芯片的定義沒有一個嚴格和公認的標準。較為寬泛的看法是面向人工智能應用的芯片都可以稱為AI芯片。具體來說,報告中探討的AI芯片主要分為三類,一是經過軟硬件優化可高效支持AI應用的通用芯片,如GPU;二是側重加速機器學習(尤其是神經網絡、深度學習)算法的芯片,這也是目前AI芯片中最多的形式;三是受生物腦啟發設計的神經形態計算芯片。

AI芯片的計算既不脫離傳統計算,也具有新的計算特質,主要特點有三:處理內容往往是非結構化數據,如視頻、圖像及語音等,需要通過樣本訓練、擬合基環境交互等方式,利用大量數據來訓練模型,再用訓練好的模型處理數據;處理過程需要很大的計算量,基本的計算主要是線性代數運算,大規模并行計算硬件更為適合;處理過程參數量大,需要巨大的存儲容量,高帶寬、低延時的訪存能力,及計算單元和存儲器件間豐富且靈活的連接。

AI芯片的新計算范式,也為芯片提出了處理非結構化數據、計算量大及存儲和計算間的訪問連接等新問題。

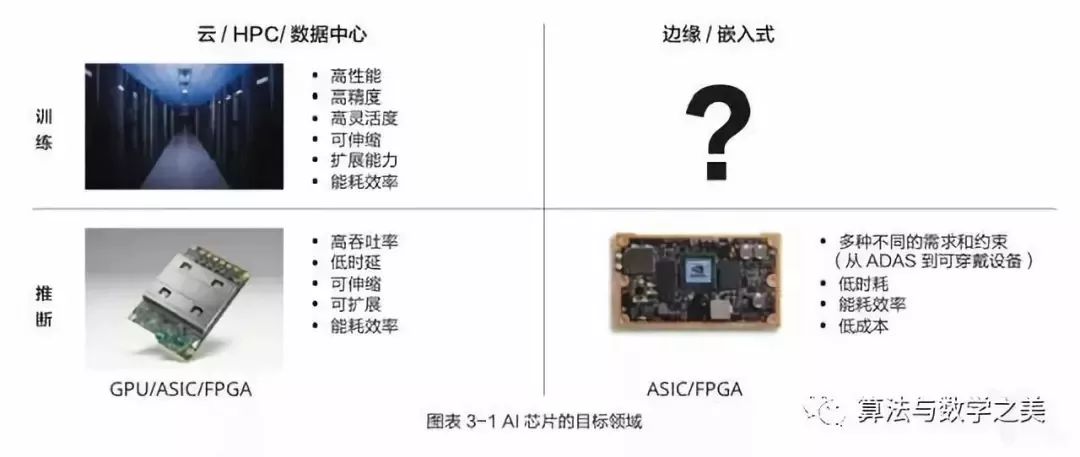

AI芯片發展現狀:云、邊結合

在應用場景上,AI芯片的應用主要分為云端和終端,以深度學習的算法來說,云端人工智能硬件負責“訓練+推斷”,終端人工智能硬件負責“推斷”,因而終端的計算量更小,相對沒有傳輸問題。但從自動駕駛、智慧家庭,到loT設備等,速度、能效、安全和硬件成本等是重要因素。

云端AI計算:目前各大科技巨頭紛紛在自有云平臺基礎上搭載人工智能系統,主要有IBM的waston、亞馬遜的AWS、以及國內的阿里云、百度云平臺等。其中英偉達的GPU采用更為廣泛,賽靈思、英特爾、百度等廠商也在積極采用FPGA在云端進行加速,一些初創公司,如深鑒科技等也在開發專門支持 FPGA 的 AI 開發工具。另外,除GPU和FPGA外,AI領域專用架構芯片ASIC則因其更好的性能和功耗,成為云端領域新的攪局者,如谷歌的TPU。

邊緣AI計算:隨著人工智能應用生態的爆發,越來越多的AI應用開始在端設備上開發和部署。

智能手機是目前應用最為廣泛的邊緣計算設備,包括蘋果、華為、高通、聯發科和三星在內的手機芯片廠商紛紛推出或者正在研發專門適應 AI 應用的芯片產品。另外,也有很多初創公司加入這個領域,如地平線機器人、寒武紀、深鑒科技、元鼎音訊等。傳統的IP 廠商,包括 ARM、Synopsys 等公司也都為包括手機、智能攝像頭、無人機、工業和服務機器人、智能音箱以及各種物聯網設備等邊緣計算設備開發專用 IP 產品。

自動駕駛是未來邊緣AI 計算的最重要應用之一,MobileEye SOC 和 NVIDIA Drive PX 系列提供神經網絡的處理能力可以支持半自動駕駛和完全自動駕駛。

目前云和邊緣設備在各種AI應用中往往是配合工作。最普遍的方式是在云端訓練神經網絡,然后在云端(由邊緣設備采集數據)或者邊緣設備進行推斷。

AI芯片的技術挑戰:馮·諾依曼、CMOS工藝和器件瓶頸

由于前文所述的AI芯片需要滿足高效的數據訪問,以及深度學習下的新的計算范式,AI芯片在發展上,也遇到了一些瓶頸問題,特別是馮·諾依曼瓶頸,及CMOS工藝和器件瓶頸。

馮·諾依曼瓶頸:在傳統“馮·諾依曼架構”中,計算模塊和存儲單元互相分離,數據從處理單元外的存儲器提取,處理完之后再寫回存儲器。每一項任務,如果有十個步驟,那么CPU會依次進行十次讀取、執行,再讀取、再執行,這就造成了延時,以及大量功耗花費在了數據讀取上。

可以不夸張地說,大部分針對AI,特別是加速神經網絡處理而提出的硬件架構創新都是在和這個問題做斗爭。概括來說,目前的解決思路包括減少訪問存儲器的數量,降低訪問存儲器的代價。

CMOS工藝和器件瓶頸:目前,人工智能,特別都是機器學習的發展將需要更有力的、超過每秒百億次運算能力的計算系統,而構建這些系統的基礎是CMOS技術的芯片,而CMOS工藝能不斷提高系統性能主要得益于集成尺寸的縮小。過去30年,摩爾定律很好預測了這種計算進步,但由于基礎物理原理限制和經濟的原因,持續提高集成密度變得越來越困難。

目前的解決方案是通過開發提供大量存儲空間的片上存儲器技術,并探索利用片上存儲器去構建未來的智能芯片架構。另外,近年來,可以存儲模擬數值的非易失性存儲器發展迅猛,能同時具有存儲和處理數據能力,可以破解傳統計算體系結構的一些基本限制,有望實現類腦突觸功能。

AI芯片架構設計趨勢:云端、邊緣設備、軟件定義

而針對以上AI芯片計算和應用上的需求,目前云端和邊緣設備的AI芯片都在進行新的研發。

AI云端訓練和推斷:大存儲、高性能、可伸縮。從英偉達和谷歌的設計實踐可以看出云端AI芯片在架構層面,技術發展的幾個特點和趨勢:存儲的需求(容量和訪問速度原來越高);處理能力推向每秒千萬億,并支持靈活伸縮和部署;專門針對推斷需求的FPGA和ASIC。

邊緣設備:目前,衡量AI 芯片實現效率的一個重要指標是能耗效率——TOPs/W,這也成為很多技術創新競爭的焦點。

其中,降低推斷的量化比特精度是最有效的方法;除降低精度外,提升基本運算單元MAC的效率還可以結合一些數據結構轉換來減少運算量;另一個重要的方向是減少對存儲器的訪問,如把神經網絡運算放在傳感器或存儲器中;此外,在邊緣設備的AI芯片中,也可以用各種低功耗設計方法來進一步降低整體功耗。最后,終端設備AI芯片往往呈現一個異構系統,專門的AI加速器和CPU、GPU、ISP、DSP等協同工作以達到最佳效率。

軟件定義芯片:通用處理器如CPU、GPU,缺乏針對AI算法的專用計算、存儲單元設計,功耗大;專用芯片ASIC功能單一;現場可編程陣列FPGA重構時間開銷過大,且過多的冗余邏輯導致其功耗過高。以上傳統芯片都難以實現AI芯片所需要的“軟件定義芯片”。

可重構計算技術允許硬件架構和功能隨軟件變化而變化,具備處理器的靈活性和專用集成電路的高性能、低功耗,是實現“軟件定義芯片”的核心,被公認為是突破性的下一代集成電路技術,清華大學的AI芯片Thinker目前采用可重構計算框架,支持卷積神經網絡、全連接神經網絡和遞歸神經網絡等多種AI算法。

AI芯片中的存儲技術、新興計算技術及神經形態芯片

如前所述,提高AI芯片的性能和能效的關鍵之一在于數據訪問。而在傳統的馮·諾依曼體系結構中,數據從存儲器串行提取并寫入到工作內存,導致相當長的延遲和能量開銷。

近期,面向數字神經網絡的極速器(GPU、FPGA和ASIC)迫切需要AI友好型存儲器;中期,基于存內計算的神經網絡可以為規避馮·諾依曼瓶頸問題提供有效的解決方案;后期,基于憶阻器的神經形態計算可以模擬人類的大腦,是AI芯片遠期解決方案的候選之一。

而對應的新興計算技術包括近內存計算、存內計算,以及基于新型存儲器的人工神經網絡和生物神經網絡。

神經形態芯片,即“仿生電腦”。如前所說,對于馮·諾依曼、CMOS工藝和器件瓶頸形成的AI芯片存儲、計算間的問題,神經形態計算是一種新的路徑。

近些年,神經形態計算也用來指采用模擬、數字、數模混合VLSI以及軟件系統實現的神經系統模型。其將數字處理器當作神經元,把內存作為突觸,內存、CPU和通信部件完全集成在一起,采用模擬人腦神經元結構來提升計算能力。每個神經元計算都是本地的,且從全局來看神經元們是分布式在工作。受到腦結構研究的成果啟發,研制出的神經形態芯片具有低功耗、低延遲、高速處理、時空聯合等特點。

人工智能的未來:算法、架構、器件的不斷探索

“未來能否有一個終極算法來實現通用人工智能?”這個問題還沒有人能給出肯定的答案。芯片是人工智能算法的物理基礎,它與算法唇齒相依。如果能有統一的終極算法出現,那么我們很可能會看到一個終極芯片出現。

但在未來很長一段時期,不同的應用仍然需要不同的算法(也包括傳統算法),因此我們還必須探索不同的架構,探索新的器件甚至材料。隨著底層芯片技術的進步,人工智能算法也將獲得更好的支持和更快的發展。

CMOS 技術與新興信息技術的交叉融合,開源軟件到開源硬件的潮流漸顯,預示著將迎來一個前所未有的協同創新機遇期。

-

人工智能

+關注

關注

1792文章

47409瀏覽量

238924 -

深度學習

+關注

關注

73文章

5507瀏覽量

121272 -

AI芯片

+關注

關注

17文章

1890瀏覽量

35097

原文標題:清華發布《AI芯片技術白皮書》:新計算范式,挑戰馮諾依曼、CMOS瓶頸

文章出處:【微信號:wwzhifudianhua,微信公眾號:MEMS技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Omdia與華為共發布NPS管理白皮書

博世與清華大學續簽人工智能研究合作協議

華為發布天線數字化白皮書

美通社推出《智能科技行業媒體概況》白皮書

中科曙光聯合發布《智能算力產業發展白皮書》

移遠通信《5G RedCap技術發展及應用白皮書》重磅發布

清華大學正式發布了《人工智能芯片技術白皮書(2018)》

清華大學正式發布了《人工智能芯片技術白皮書(2018)》

評論