電磁兼容性是指電氣和電子系統及設備在特定的電磁環境中,在規定的安全界限內以設定的等級運行時,不會由于外界的電磁干擾而引起損壞或導致性能惡化到不可挽救的程 度,同時它們本身產生的電磁輻射不大于檢定的極限電平,不影響其他電子設備或系統的正常運行,以達到設備與設備、系統與系統之間互不干擾、共同可靠地工作 的目的。

一、電磁兼容產生的因素

(1)電阻的頻率特性

在數字電路中,電阻的主要作用在于限流和確定固定電平,在高頻電路中,存在于電阻兩端的高頻寄生電容會對正常的電路特性造成破壞。同樣電阻的引腳電感對電路的EMC影響很大。

(2)電容的頻率特性

電容器一般應用在電源總線,它提供去耦合、旁路和維持固定的直流電壓和電流的作用。但是在高頻電路中,當電路的工作頻率超過了電容的自諧振頻率時,其寄生電感將使電容表現為電感特性,從而失去原有的功能并影響電路的工作性能。

(3)電感的頻率特性

電感器是用來控制PCB內的EMI。當電路的工作頻率增加時,電感的等效阻抗會隨著頻率的增加而增大,當電路的工作頻率超過電感的工作頻率上限時,電感將會影響電路的正常工作。

(4)導線的頻率特性

PCB上的走線和元器件的引腳導線都有寄生電感和電容,這些寄生電感和電容會影響到導線的頻率特性,從而有可能在元器件和導線之 間產生諧振,致使導線成為電磁干擾的重要發射天線。通常,導線在低頻段表現為電阻特性,在高頻段則表現為電感特性,因此在PCB上,導線的長度一般要求小 于工作頻率波長的二十分之一,以避免導線成為電磁干擾的發射源。

(5)靜電

靜電放電問題已經成為電子產品的一大公害,可能給產品帶來永久性的損壞,因此在產品設計中,必須采取相應的靜電防護措施。常用的防靜電措施包括選擇具有防靜電材料,采用電氣隔離措施,提高產品的絕緣強度以及設置良好的靜電屏蔽層和泄放通道等。

(6)電源

隨著高頻開關電源的廣泛應用和電力系統負荷的不斷增加,電源對產品的干擾問題逐漸成為影響產品EMC特性的一個重要因素。因此,一些易受干 擾的敏感設備已經不直接采用交流供電而改用直流供電,這樣雖然增加了系統的復雜性和成本,但是有效提高了系統工作的穩定性。

(7)雷電

雷電實質上是一種正負電荷中和的強靜電放電過程,由此產生的強電磁脈沖導致各種電子設備受損的主要原因。雷電對電子設備的影響包括直擊雷和 感應雷兩種,現在各種室內使用的電子設備,一般不容易遭受直擊雷的影響,但是依然容易受到感應雷的損害。為了確保電子設備的安全運行,必須對電子設備進行 防雷擊保護。常用的防雷措施包括設置避雷針、安裝避雷器和避雷線等。

二、電磁兼容產生的要素

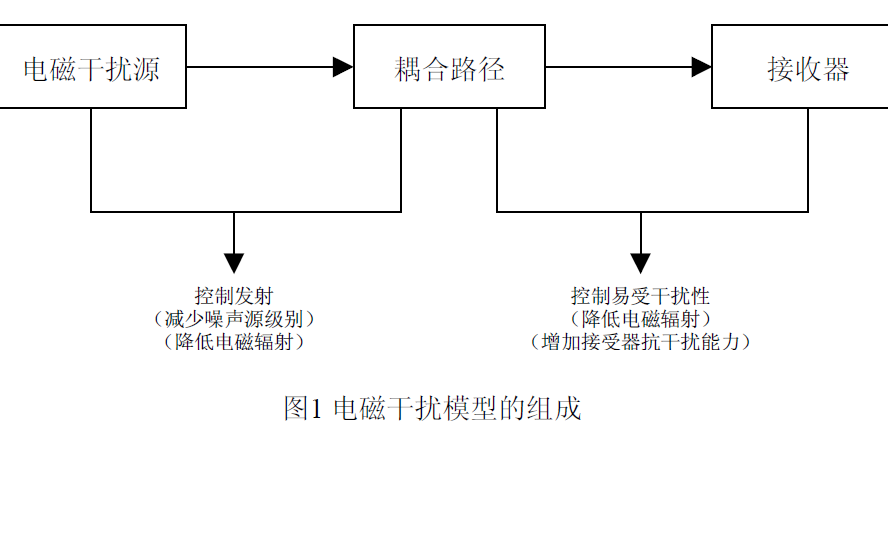

理論和實踐的研究證明,不管復雜系統還是簡單裝置,任何一個電磁干擾的發生必須具備三個基本條件:存在一定的干擾源、有干擾的完整耦合通道、有被干擾對象的響應。

電磁干擾源

電磁干擾源指產生電磁干擾的任何元件、器件、設備、系統或自然現象。高頻電路對電磁干擾尤為敏感,因而需要采取多種措施來抑制電磁干擾。經過理論與實驗分析得知:高頻電路中,電磁干擾主要來自以下幾個方面:

(1)器件工作的噪聲干擾

(a)數字電路工作時產生電磁干擾。

(b)信號電壓、電流變化產生的電磁場干擾。

(2)高頻信號噪聲干擾

(a)串擾:是指一個信號在傳輸通道上傳輸時,因電磁耦合而對相鄰的傳輸線產生不期望的影響,在被干擾信號表現為被注入了一定的耦合電壓和耦合電流。過大的串擾可能引起電路的誤觸發、時序延時,導致系統無法正常工作。

(b)回波損耗:當高頻信號在電纜及通信設備中傳輸時,遇到波阻抗不均勻點時,就會對信號形成反射,這種反射不但導致信號的傳輸損耗增大,并且會使傳輸信號畸變,對傳輸性能影響很大。

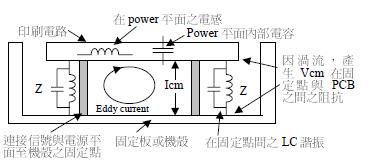

(3)電源噪聲干擾

PCB中的電源噪聲主要由電源自身產生或受擾感應的噪聲組成,主要表現為:①電源本身所固有的阻抗所導致的分布噪聲;②共模場干擾;③差模場干擾;④線間干擾;⑤電源線耦合。

(4)地線噪聲干擾

由于地線上存在電阻、阻抗,當電流通過地線時,就會產生壓降,當電流足夠大或工作頻率足夠高時,這個壓降會大到足以對電路造成干擾。地線導致的噪聲干擾主要包括地線環路干擾和公共阻抗耦合干擾。

(a)地線環路干擾:當多個功能單元連接在地線上時,如果地線中的電流足夠大,則會在設備間的連接電纜上產生壓降。由于各個電路間的電氣特性不平衡,每根導線上的電流會不同,因此產生差模電壓,從而對電路造成影響。此外外部電磁場也有可能在地線環路中感應出電流,從而導致干擾。

(b)公共阻抗耦合干擾;當多個功能單元公用同一段地線時,由于地線阻抗的存在,各個單元的地電位之間會發生相互調制,從而導致各個單元信號間相互耦合產生干擾,在高頻電路中,電路處于高頻工作狀態,地線阻抗往往較大,此時的公共阻抗耦合干擾尤其明顯。

消除公共阻抗耦合的途徑有兩個:一個是減小公共地線部分的阻抗,這樣公共地線上的電壓也隨之減小,從而控制公共阻抗耦合。另一個方法是通過適當的接地方 式避免容易相互干擾的電路共用地線,一般要避免強電電路和弱電電路共用地線,數字電路和模擬電路共用地線。

如前所述,減小地線阻抗的核心問題是減小地線的 電感。這包括使用扁平導體做地線,用多條相距較遠的并聯導體作接地線。對于印刷線路板,在雙層板上布地線網格能夠有效地減小地線阻抗,在多層板中專門用一 層做地線雖然具有很小的阻抗,但這會增加線路板的成本。通過適當接地方式避免公共阻抗的接地方法是并聯單點接地,并聯接地的缺點是接地的導線過多。

因此在 實際中,沒有必要所有電路都并聯單點接地,對于相互干擾較少的電路,可以采用串聯單點接地。例如,可以將電路按照強信號,弱信號,模擬信號,數字信號等分 類,然后在同類電路內部用串聯單點接地,不同類型的電路采用并聯單點接地。

抑制耦合通道

高速電路中電磁干擾的主要耦合通道包括輻射耦合、傳導耦合、電容耦合、電感耦合、電源耦合以及地線耦合等。

對于輻射耦合來說,其主要抑制方法是采取電磁屏蔽,將干擾源與敏感對象有效隔離。

對于傳導耦合來說,其主要的方法是在信號布線的時候,合理安排高速信號線的走向。輸入輸出端用的導線應盡量避免相鄰平行,以免發生信號反饋或串擾,可在 兩條平行線間增設一條地線加以隔離。

對于外連信號線來說,應盡量縮短輸入引線,提高輸入端阻抗。對模擬信號輸入線最好加以屏蔽,當板上信號導線阻抗不匹配 時,會導致信號反射,當印制導線較長時,線路電感會導致減幅振蕩。通過串入阻尼電阻(阻值通常取22~2 200 hm,典型值為470 hm),可有效抑制振蕩,增強抗干擾能力,改善波形。

對于電感、電容的耦合干擾來說,可采用如下兩個方面進行抑制:一方面是選擇合適的 元器件,對于電感電容,應該根據不同元器件的頻率特性來選擇,對于其他元器件,則應選擇寄生電感、電容較小的器件。

另一方面是合理地進行布局和布線,要盡 量避免長距離平行布線,電路中電氣互連點間的布線力求最短。信號(特別是高頻信號)線的拐角應設計成45度走向或稱圓形、圓弧形,切忌畫成小于或等于90 度角度形狀。

相鄰布線面導線采取相互垂直、斜交或彎曲走線的形式以減少過孔的寄生電容和電感,過孔和管腳之間的引線越短越好,并可以考慮并聯打多個過孔或 微型過孔以減少等效電感。選用元器件封裝時,應選擇標準封裝,以減少因封裝不匹配而導致的引線阻抗及寄生電感。

對于電源耦合以及地耦合來說,首先應注意降低電源線和地線阻抗,對公共阻抗、串擾和反射等引起的波形畸變和振蕩現象需采取必須措施。在各集成電路的電源和地線間分別接入旁路電容 以縮短開關電流的流通途徑。將電源線和地線設計成格子形狀,而不用梳子形狀,這是因為格子狀能顯著縮短線路環路,降低線路阻抗,減少干擾。

當印制電路板上 裝有多個集成電路,且部分元件功耗較大,地線出現較大電位差,形成公共阻抗干擾時,宜將地線設計成封閉環路,這種環路無電位差,具有更高的噪聲容限。應盡量縮短引線,將各集成電路的地以最短距離連到電路板的入口地線,降低印制導線產生的尖峰脈沖。讓地線、電源線的走向與數據傳輸方向一致,以提高電路板的噪 聲容限。盡量采用多層印制電路板,降低接地電位差,減少電源線阻抗和信號線間串擾。

當沒有多層板而不得不使用雙面板時,必須盡量加寬地線線條,通常地線應 加粗到可通過3倍于導線實際流過的電流量為宜,或采用小型母線方式,將公共電源線和地線盡量分布于印制板兩面的邊緣。在電源母線插頭處接入 1μF~10μF的鉭電容器進行去耦,并在去耦電容并聯一個0.01 μF~0.1μF的高頻陶瓷電容器。

保護敏感對象

對敏感對象的保護主要集中在兩個方面,一方面是切斷敏感對象與電磁干擾之間的通道。另一方面就是降低敏感對象的敏感度。

電子設備的敏感度是一柄雙刃劍,一方面使用者希望電子裝置的靈敏度高,以提高對信號的接受能力;另一方面,靈敏度高也意味著受噪聲影響的可能性越大。因此電子設備的敏感度應根據具體情況來確定。

對于模擬電子設備來說,通常采用的方法是采用優選電路,比如設計低噪聲電路、減少帶寬、抑制干擾傳輸、平衡輸入、抑制干擾及選用高質量電源等。通過這些方法可以有效降低電子設備對電磁干擾的敏感度,提高設備的抗干擾能力。

對于數字式電子設備來說,應在工作指標許可的情況下,采用直流噪聲容限高的數字電路,例如CMOS數字電路的直流噪聲容限遠高于TTL數字電路的直流噪 聲容限;在工作指標許可的情況下,盡量采用開關速度低的數字電路,因為開關速度越高,由它引起的電壓或電流的變化也就越快,從而越容易產生電路間的耦合干 擾;

在電路可接受的前提下,盡可能提高門檻電壓,利用在電路前設置分壓器或穩壓管的方法來提高門檻電壓;采用負載阻抗匹配的措施,即使負載阻抗等于信號線 的波阻抗,消除數字信號在傳輸過程中由于折射和反射的作用而產生的畸變。

通常情況下,對敏感對象的保護需要與對干擾源的屏蔽以及對耦合通道的抑制結合起來 使用,并且需要在實踐中根據實際情況進行反復實驗,以達到最好的防護效果。

總結

高速電路板的電磁兼容分析與設計是一個系統性很強的工作,需要大量的工作經驗積累。電磁兼容設計是關系電子系統是否能實現功能、滿足設計指標的關鍵之一,隨著電子系統的復雜程度增加,工作頻率增高,電磁兼容設計在電子設計中的地位將越來越突出,越來越重要。

-

電磁兼容

+關注

關注

54文章

1872瀏覽量

97863 -

電路板

+關注

關注

140文章

4951瀏覽量

97689

原文標題:20190120---高速電路板的電磁兼容分析與設計

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

電磁兼容設計—印制電路板篇

電磁兼容設計-電路板級(電子書)

電磁兼容和印刷電路板(理論、設計和布線)

如何設計符合電磁兼容要求的電路板

如何設計電磁兼容的電路板

高速電路板的電磁兼容分析與設計

高速電路板的電磁兼容分析與設計

評論