聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

電源

+關注

關注

184文章

17704瀏覽量

249965 -

穩壓器

+關注

關注

24文章

4223瀏覽量

93762 -

圖像傳感器

+關注

關注

68文章

1897瀏覽量

129528

發布評論請先 登錄

相關推薦

耦合器的噪音控制技術 耦合器性能測試標準與方法

率的材料可以減少信號傳輸過程中的噪音。 設計優化 :通過優化耦合器的結構設計,如調整耦合器的尺寸和形狀,可以減少寄生電容和電感,從而降低噪音。 屏蔽技術 :使用屏蔽材料可以減少外部電磁干擾對耦合器的影響,降低噪音。

詳解LDO電路的電源抑制比

電源抑制(Power Supply Rejection)能力是SoC系統中電源模塊很重要的指標,在當今數字和模擬電路高度集成的趨勢下,一個能提供穩定輸出電壓的系統模塊顯得尤為重要,而這個模塊又很容易受到供電

使用PCM5242,當喇叭輸出最大音量時伴有“沙,沙”低噪音,爆破音很大怎么解決?

使用PCM5242,當喇叭輸出最大音量時伴有“沙,沙”低噪音,爆破音很大

功放前端4通道波形信號1khz時很完美,功放后端失真披鋒較多,看情況應該是后端問題,請問有沒有什么建議?

發表于 10-10 08:23

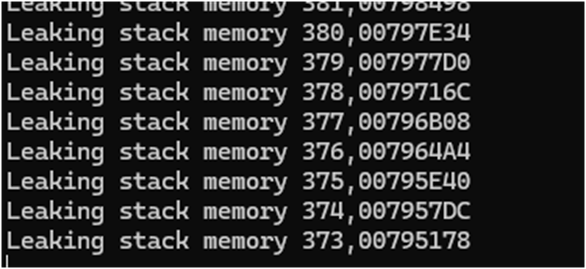

堆棧和內存的基本知識

本文主要聊聊關于堆棧的內容。包括堆棧和內存的基本知識。常見和堆棧相關的 bug,如棧溢出,內存泄漏,堆內存分配失敗等。后面介紹軟件中堆棧統計的重要性,以及如何使用工具工具軟件中堆棧使用的范圍,并給出在軟件開發中,如何降低堆棧問題,優化堆棧的一些實踐。

影響電路共模抑制比的因素有哪些?如何去提高電路的共模抑制比?

此電路用來檢測腦電波的信號,性能要求此電路的共模抑制比要達到不低于80dB,而現在實測只能達到67dB,想知道,影響電路共模抑制比的因素有哪些?如何去提高電路的共模抑制比?

發表于 08-20 07:21

運放的共模抑制比和電源抑制比對輸出精度的影響是什么?

的共模抑制比為120dB,單純考慮共模抑制比的影響電流60A,運放輸出值理論為Vo=0.0335*60,該怎么計算輸出的誤差呢?Gain取大于1和小于1影響是怎么樣的?

2、電源抑制比

發表于 08-15 07:43

如何理解運放的電源抑制比參數?

電源抑制比PSRR有三個參數,如OPA333

1、電源抑制比為1uV/V

2、長期穩定性為1uV

3、通道分離,直流為0.1uV/V

特

發表于 08-12 06:37

LDO電源抑制比的測量方法

LDO電源抑制比(PSRR,Power Supply Rejection Ratio)是衡量線性穩壓器(LDO)在電源電壓變化時對輸出電壓穩定性的影響的一個重要指標。 一、LDO

電機電磁噪音的產生機理和降低措施

電磁噪音的來源進行深入解析,對于降低噪音污染、提高電機性能具有重要意義。本文將從電磁噪音的產生機理、影響因素以及降低噪音的措施等方面進行詳細闡述。

什么是電源抑制比(PSRR)?它有哪些作用和應用?

在電子設備和系統的設計中,電源抑制比(Power Supply Rejection Ratio,簡稱PSRR)是一個至關重要的參數。它描述了電子設備或系統對來自電源的噪聲和干擾的

電源紋波與電源抑制比解析

在電子電路設計中,電源的穩定性和純凈性對電路的性能至關重要。電源紋波和電源抑制比作為評估電源性能的兩個重要參數,對電路的穩定運行和信號質量有

250mA低瞬態電流,超低噪音,高電源抑制比(PSRR) 低壓降線性穩壓器數據表

電子發燒友網站提供《250mA低瞬態電流,超低噪音,高電源抑制比(PSRR) 低壓降線性穩壓器數據表.pdf》資料免費下載

發表于 02-29 16:53

?0次下載

–36V, –200mA,超低噪音,負電源線性穩壓器TPS7A3001-EP數據表

電子發燒友網站提供《–36V, –200mA,超低噪音,負電源線性穩壓器TPS7A3001-EP數據表.pdf》資料免費下載

發表于 02-29 15:41

?0次下載

電源抑制比的基本知識及如何降低噪音

電源抑制比的基本知識及如何降低噪音

評論