FPGA中軟核和硬核的意思

軟核在EDA設計領域指的是綜合之前的寄存器傳輸級(RTL)模型;具體在FPGA設計中指的是對電路的硬件語言描述,包括邏輯描述、網表和幫助文檔等。軟核只經過功能仿真,需要經過綜合以及布局布線才能使用。其優點是靈活性高、可移植性強,允許用戶自配置;缺點是對模塊的預測性較低,在后續設計中存在發生錯誤的可能性,有一定的設計風險。軟核是IP核應用最廣泛的形式。

2、硬核(HardIPCore)

硬核在EDA設計領域指經過驗證的設計版圖;具體在FPGA設計中指布局和工藝固定、經過前端和后端驗證的設計,設計人員不能對其修改。不能修改的原因有兩個:首先是系統設計對各個模塊的時序要求很嚴格,不允許打亂已有的物理版圖;其次是保護知識產權的要求,不允許設計人員對其有任何改動。IP硬核的不許修改特點使其復用有一定的困難,因此只能用于某些特定應用,使用范圍較窄。

IP中軟核和硬核的意思

1、軟核

IP軟核通常是用HDL文本形式提交給用戶,它經過RTL級設計優化和功能驗證,但其中不含有任何具體的物理信息。據此,用戶可以綜合出正確的門電路級設計網表,并可以進行后續的結構設計,具有很大的靈活性,借助于EDA綜合工具可以很容易地與其他外部邏輯電路合成一體,根據各種不同半導體工藝,設計成具有不同性能的器件。軟IP內核也稱為虛擬組件(VC-VirtualComponent)。

2、硬核

IP硬核是基于半導體工藝的物理設計,已有固定的拓撲布局和具體工藝,并已經過工藝驗證,具有可保證的性能。其提供給用戶的形式是電路物理結構掩模版圖和全套工藝文件,是可以拿來就用的全套技術。

-

FPGA

+關注

關注

1630文章

21783瀏覽量

605023 -

軟核

+關注

關注

0文章

14瀏覽量

15869

發布評論請先 登錄

相關推薦

軟通動力入選新華社年度智能零碳成果展

一文搞懂軟核的固化、啟動和MultiBoot實現

RISC-V發展及FPGA廠商為什么選擇RISC-V

靈動微電子MM32H5480榮獲2024年度硬核MCU芯片獎

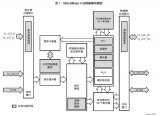

MicroBlaze V軟核處理器的功能特性

新品發布 | 硬核強芯,實力全開,啟揚智能RK3588開發板,助力AIOT應用高效升級!

軟核和硬核的意思

軟核和硬核的意思

評論