無論是7系列FPGA、UltraScale還是UltraScale Plus系列FPGA,都包含Block RAM(BRAM),但只有UltraScale Plus芯片有UltraRAM也就是我們所說的URAM。BRAM和URAM都是重要的片上存儲資源,但兩者還是有些顯著的區(qū)別。

容量

BRAM的容量為36Kb,且可當作兩個獨立的18KbBRAM使用。對于一個36Kb的BRAM,其最能達到的最大位寬為72bit。URAM容量為288Kb,一個URAM深度為4K(4×1024),寬度為72b。

BRAM有兩個時鐘,在RAMB36E2的Primitive聲明中就可以看到這兩個時鐘CLKARDCLK和CLKBWRCLK。而URAM只有一個時鐘,在URAM288的Primitive聲明中可以看到該時鐘CLK。盡管在使用XPM_MEMORY實例化URAM時可以看到clka和clkb,但這兩個端口最終都連接到URAM的物理端口CLK上。

初始值

BRAM的初始值是可以設(shè)定的,無論BRAM是單端口、簡單雙端口還是真雙端口都可以通過COE文件設(shè)定其初始值。而URAM的初始值只能為0,且無法更改,換言之,其初始值是不可設(shè)定的。這也就意味著BRAM可以配置成ROM而URAM不可以。

工作模式

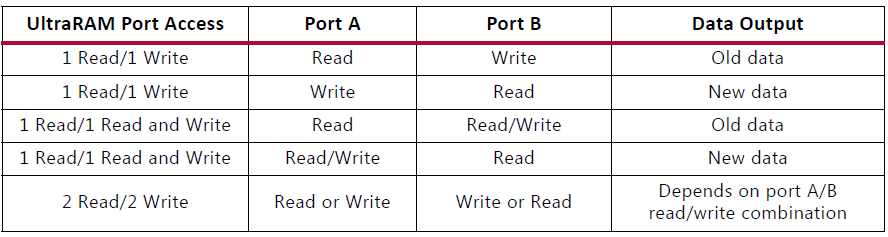

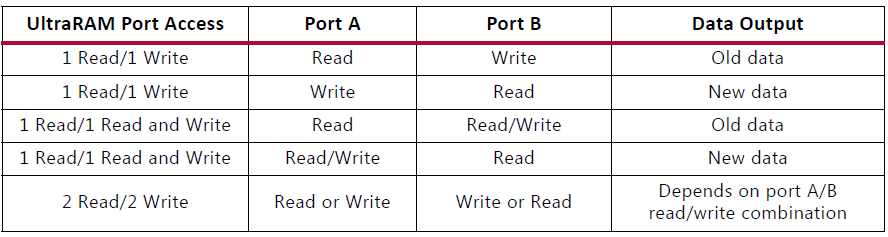

BRAM可配置為單端口、簡單雙端口和真雙端口,但對于URAM,不能簡單地將這三種模式映射過來,其工作行為如下圖所示。可以看到,A/B端口不是獨立的,例如,A端口讀而B端口寫同一地址,讀出的是該地址原有數(shù)據(jù);A端口寫而B端口讀同一地址,讀出的是新寫入的數(shù)據(jù)。

圖片來源:Table 2-6, ug573

實例化方式

對于BRAM,可采用原語、XPM_MEMORY、RTL代碼或者IP Core的方式進行實例化,但URAM目前只支持原語、XPM_MEMORY和RTL代碼的方式。相比而言,XPM_MEMORY的方式更為快捷,也是Xilinx建議的方式。

級聯(lián)方式

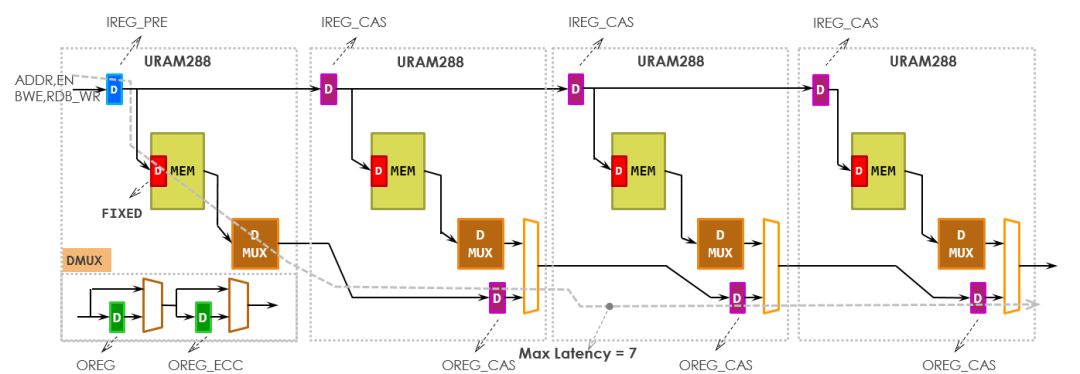

BRAM和URAM都可級聯(lián),只是級聯(lián)方式不同。在使用BRAM時,我們只需要設(shè)定寬度和深度,并根據(jù)時鐘頻率合理選擇Latency,也就是選擇是否需要使用BRAM自帶的輸出寄存器或Slice中的寄存器。而URAM提供了專門的級聯(lián)寄存器,同樣需要根據(jù)時鐘頻率合理選擇Latency,此時會影響到級聯(lián)寄存器的使用。如下圖所示,是4個URAM的級聯(lián)情形。

-

寄存器

+關(guān)注

關(guān)注

31文章

5336瀏覽量

120231 -

BRAM

+關(guān)注

關(guān)注

0文章

41瀏覽量

10956

原文標題:URAM和BRAM有什么區(qū)別

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

請問SYS/BIOS和DSP/BIOS兩者之間有什么區(qū)別?

單片機和嵌入式兩者有什么區(qū)別和聯(lián)系呢

CPLD和FPGA兩者的區(qū)別

無線熱點和無線局域網(wǎng)兩者的區(qū)別以及聯(lián)系

URAM和BRAM有哪些區(qū)別

URAM和BRAM有什么區(qū)別

BRAM和URAM重要的片上存儲資源,兩者有顯著的區(qū)別

BRAM和URAM重要的片上存儲資源,兩者有顯著的區(qū)別

評論