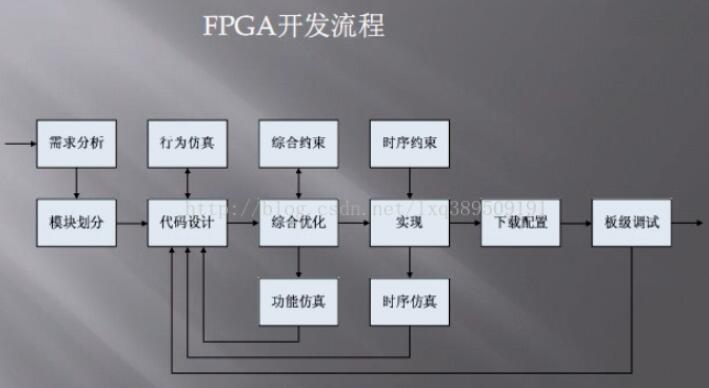

FPGA開發(fā)流程概述

開始學(xué)習(xí)FPGA,想盡快上手FPGA開發(fā),那么先來了解一下FPGA的開發(fā)流程。

1、需求分析到模塊劃分

需求說明文檔;器件選擇(邏輯資源、功耗、IO數(shù)量、封裝等等);配置電路考慮;開發(fā)工具選擇;電路板的可拓展性考慮;在線調(diào)試和板級(jí)調(diào)試考慮;分模塊設(shè)計(jì)。

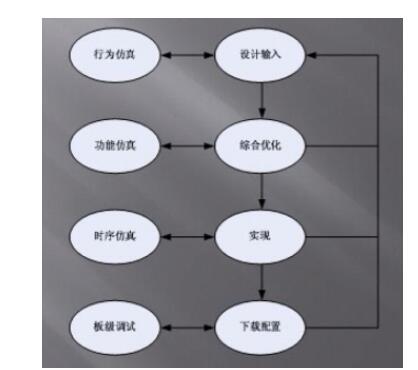

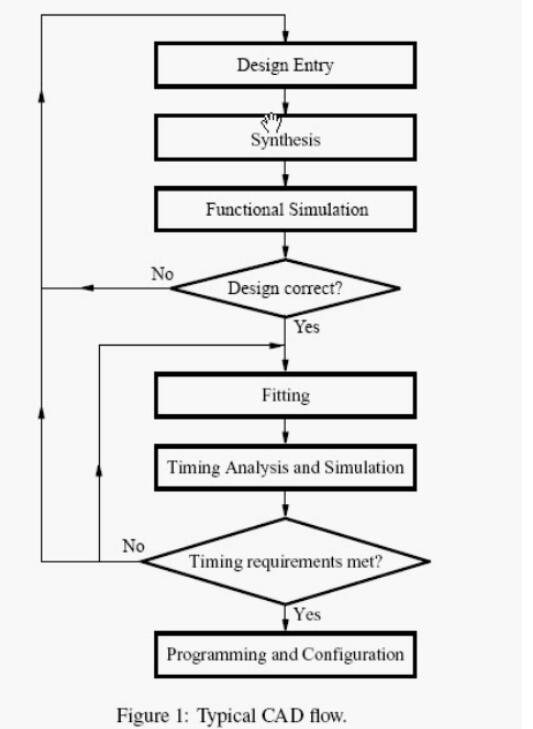

2、設(shè)計(jì)輸入到綜合優(yōu)化

設(shè)計(jì)輸入:原理圖、Verilog、VHDL

綜合:指的是將較高層次的電路描述轉(zhuǎn)化成較為低層的電路描述。就是將設(shè)計(jì)代碼轉(zhuǎn)成底層的與門、非門、RAM、觸發(fā)器等基本邏輯單元相互連接而成的網(wǎng)表,綜合工具使用Synplicity的Synplify,也可使用器件廠商提供的開發(fā)工具進(jìn)行實(shí)現(xiàn)(實(shí)現(xiàn)指的是:翻譯、映射、布局布線)。

代碼設(shè)計(jì)完成后,最好先使用開發(fā)工具進(jìn)行語法檢測(cè),之后進(jìn)行功能仿真,此處仿真不涉及時(shí)序上的延時(shí)。仿真工具首推ModelTech公司的ModelSim,也可以用ISE的Quartus 2進(jìn)行簡(jiǎn)單仿真。

3、實(shí)現(xiàn)到時(shí)序收斂

實(shí)現(xiàn):

翻譯---將綜合后的結(jié)果轉(zhuǎn)化成所選器件的底層模塊和硬件原語;

映射---將翻譯的結(jié)果映射到具體器件上;

布局布線---根據(jù)用戶的設(shè)計(jì)約束,進(jìn)行布局布線,完成FPGA內(nèi)部邏輯的連接;

時(shí)序收斂:(設(shè)計(jì)關(guān)鍵,必須滿足時(shí)序收斂)

工具的最紅布局布線滿足設(shè)計(jì)者輸入的時(shí)序約束要求。

4、仿真到板級(jí)調(diào)試

仿真和板級(jí)調(diào)試用于主要的驗(yàn)證。FPGA的板級(jí)調(diào)試一個(gè)很大的問題在于同步觀察接口信號(hào)數(shù)量受限,很難觀測(cè)內(nèi)部信號(hào)節(jié)點(diǎn)的狀態(tài),假若純板級(jí)調(diào)試,就消耗太大的人力物力了。

FPGA仿真很重要,但是和其他軟件開發(fā)中的仿真概念不大一樣。時(shí)序電路,邏輯的每一步變化都是由時(shí)終沿來觸發(fā)的,調(diào)試時(shí)控制時(shí)鐘頻率顯然不能達(dá)到單步的效果。

開發(fā)團(tuán)隊(duì)一般不會(huì)嚴(yán)格地執(zhí)行所有的三次仿真,一般做行為仿真和時(shí)序仿真,當(dāng)我們熟練的可以編寫可綜合的代碼,我們只需要進(jìn)行功能仿真,時(shí)序仿真也一般不做,我們會(huì)花時(shí)間去做深入細(xì)致的時(shí)序約束,通過時(shí)序報(bào)告分析解決時(shí)序問題。

關(guān)于FPGA的調(diào)試有很多種方法,借助示波器和邏輯分析儀的調(diào)試方法最常用。如ISE的Chipscope、Quartus 2、SignalTap 2。練習(xí)的時(shí)候可以使用Quartus 2 。

關(guān)于Quaryus 2的開發(fā)流程,在該軟件的help---PDF_Tutorials---Verilog HDL users:

Quartus 2的工程建立、使用、編譯,在此就不一一贅述,但是要明白Task窗口的編譯步驟:

Compile Design ---- 使用說明

Analysis & Synthesis ---- 分析綜合

Fitter(Place & Route) ---- 適配(布局布線)

Assembler(Generate programming files)---- 產(chǎn)生相應(yīng)的編程下載配置的文件,一般是 bit數(shù)據(jù)流,sof/pof格式

TimeQuest Timing Analysis ---- 時(shí)序分析

EDA Netlist Writer ---- 給 Quartus 2 支持的第三方提供網(wǎng)表

Program Derice (Open Programmer) ---- 配置

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603000 -

FPGA開發(fā)

+關(guān)注

關(guān)注

1文章

43瀏覽量

14911

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【AG32開發(fā)板體驗(yàn)連載】AG32VF407中開發(fā)流程學(xué)習(xí)

萊迪思Propel工具套件加速FPGA應(yīng)用開發(fā)

FPGA的學(xué)習(xí)筆記---FPGA的開發(fā)流程

品讀《基于FPGA與RISC-V的嵌入式系統(tǒng)設(shè)計(jì)》

fpga原型驗(yàn)證流程

fpga開發(fā)一般用什么軟件

fpga開發(fā)是什么意思

fpga開發(fā)板是什么?fpga開發(fā)板有哪些?

fpga設(shè)計(jì)流程

芯科科技發(fā)布新版藍(lán)牙開發(fā)流程

FPGA開發(fā)流程概述

FPGA開發(fā)流程概述

評(píng)論