說起PDN想必大家都不陌生。在PCB電源趨于低電壓、大電流的今天,電源分配網絡(Power Delivery Network)設計就顯得尤為重要。要保證系統穩定的運行,除了要考慮電源的直流壓降,還需要考慮電源噪聲是否滿足系統要求。每個工程師都希望自己項目的電源都能和自己一樣,安靜的當一個的美男子。

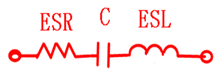

看過《謎一樣的電容》的小伙伴都明白,利用電容的隔直通交屬性,可以將DC電源中的交流噪聲短路進GND來達到濾波的效果。理論上一個電容就能將所有的噪聲都濾除,但是理想很豐滿,現實很骨感。之前為了方便理解電容的特性,我們使用的都是理想電容模型,而實際電容器除了電容之外還有另外的寄生參數。分別是等效串聯電阻(ESR)、等效串聯電感(ESL)。這兩個寄生參數與電容一起構成一個等效電路,影響著電容的實際濾波效果。

實際電容器模型表示如下:

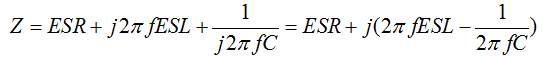

要了解寄生參數是怎么影響電容的濾波效果,就需要引入容抗和感抗。因為寄生參數變化會使容抗、感抗隨之變化,進而影響電容的濾波能力。想了解變化原理的同學就仔細看下公式,不想看公式的同學直接看黑體筆記吧!

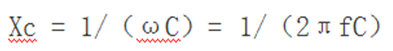

容抗:交流電路中,電荷在電路中做周期性的往返運動,電荷的運動速度與電壓、電容和頻率成正比關系,將電容和頻率相乘,則得到一個類似于電阻的量,由于沒有熱的產生,因此將這一量稱為容抗,容抗的單位和電阻單位一樣,也是歐姆。

容抗公式:

Xc電容容抗值

ω角速度

π圓周率

f 頻率

C電容值 法拉

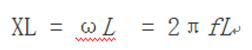

感抗:因為電感對交流電有阻礙作用,所以把電感與頻率的合成效應稱為感抗。單位和容抗一樣都是歐姆。

感抗公式:

XL 電感感抗直

ω 角速度

f頻率

L 電感

電容的阻抗=寄生電阻+(感抗-容抗)

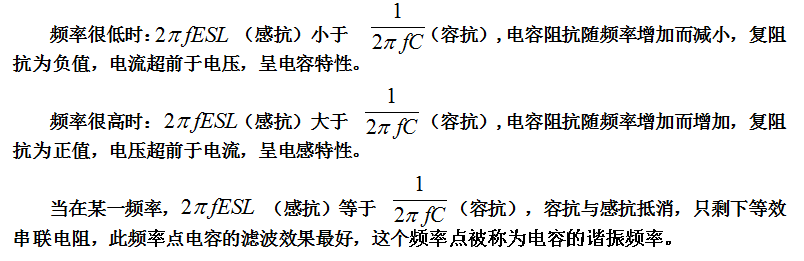

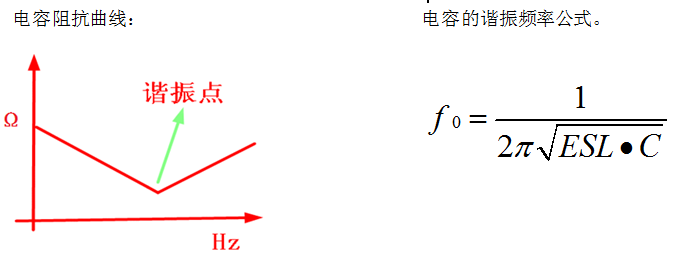

從公式可以總結以下三點:

由于容抗和感抗的影響,導致實際電容器的阻抗會隨頻率變化而變化。

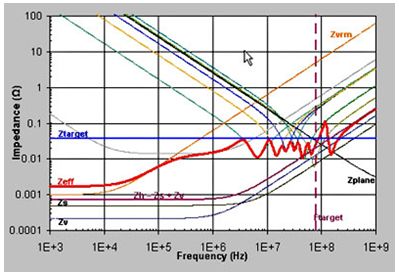

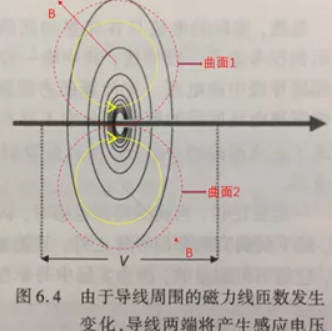

因為寄生參數對電容的影響,導致實際電容器只有在諧振頻率點附近頻段,才具有很好的濾波效果。根據電容阻抗公式可以知道容量大的電容諧振頻率點較低低,容量小的電容諧振頻率點較高。通過將不同容量的電容并聯使用,讓不同的諧振頻率覆蓋工作頻段,使工作頻段整體都能獲得很好的濾波效果。這就是電源通常需要使用大小不同的電容進行組合濾波的原因,由多種大小不同的電容阻抗曲線組合成的包線就是電源PDN阻抗曲線。如下圖紅色曲線:

電源PDN阻抗曲線就是PCB濾波能力的直觀體現(劃重點)。

通過使用頻域目標阻抗法分析PDN阻抗曲線,判斷我的PCB濾波能力是否滿足系統對電源質量的要求。說到這有的小伙伴就要問了,如果有的頻段PDN阻抗不滿足怎么辦,通常我們增加該諧振頻率的電容,或者調整周圍頻段的電容搭配降低該頻段的阻抗。

由于電源PDN曲線并不是固定不變的。電容自身封裝大小、容值公差等因素都會影響電容的阻抗曲線。除了器件自身的影響,設計引入的安裝電感,也會使電容的阻抗曲線偏移。不良設計會引入過量的安裝電感,甚至會使電容失去濾波效果。由于低電壓、大電流的電源對濾波能力要求更高,PDN阻抗裕量更小。所以需要通過仿真得到準確的電源PDN阻抗曲線。

-

電容器

+關注

關注

64文章

6217瀏覽量

99539 -

電容

+關注

關注

100文章

6036瀏覽量

150268 -

等效電路

+關注

關注

6文章

292瀏覽量

32756

原文標題:原來你是這樣的PDN

文章出處:【微信號:yes-easy-high-speed,微信公眾號:高速先生】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

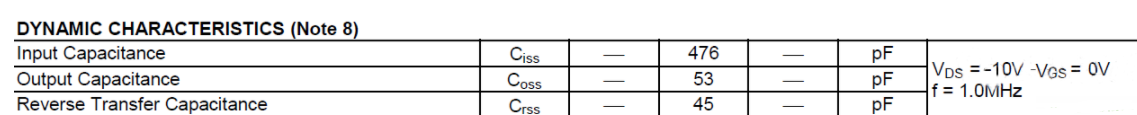

MOSFET寄生電容參數如何影響開關速度

濾波電容位置的相關資料分享

利用PCB 線圈消除濾波電容器的寄生電感

利用PCB線圈消除濾波電容器的寄生電感

什么是寄生電感_PCB寄生電容和電感計算

什么是寄生電容_寄生電容的危害

PDN設計關鍵點之濾波電容位置

如何實現高頻濾波 穿心電容濾波原理

了解寄生參數是怎么影響電容的濾波效果

了解寄生參數是怎么影響電容的濾波效果

評論