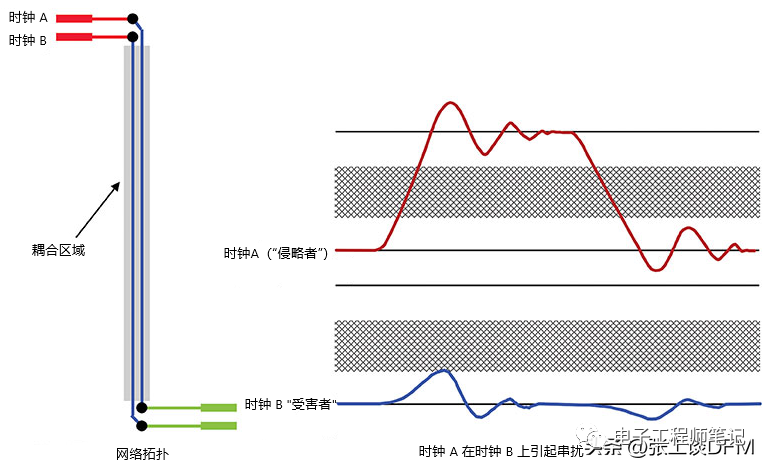

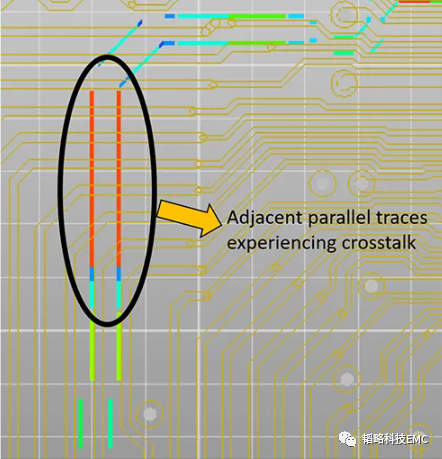

串?dāng)_是指一個(gè)信號(hào)在傳輸時(shí),因電磁耦合等原因,對(duì)相鄰的傳輸線產(chǎn)生不期望的影響,在被干擾信號(hào)表現(xiàn)為被注入了一定的耦合電壓和耦合電流。過(guò)大的串?dāng)_可能引起電路的誤觸發(fā),導(dǎo)致系統(tǒng)無(wú)法正常工作。

電子產(chǎn)品的發(fā)展,朝著小體積、高速度的方向發(fā)展,體積減小會(huì)導(dǎo)致電路的布局布線密度變大,而信號(hào)的頻率卻在提高,使得串?dāng)_高發(fā)。PCB的設(shè)計(jì)、生產(chǎn)中,串?dāng)_是一個(gè)必須嚴(yán)肅對(duì)待的問(wèn)題。

那么,我們?cè)谠O(shè)計(jì)PCB的時(shí)候,應(yīng)該注意什么呢?

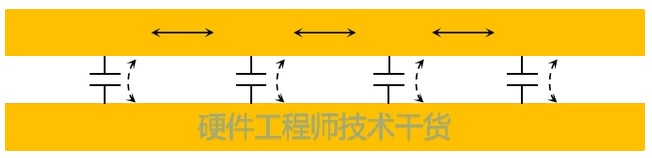

1.線之間的間距盡量大,因?yàn)殚g距越大,電容電感之間的影響就越小,電磁場(chǎng)耦合也會(huì)變小。

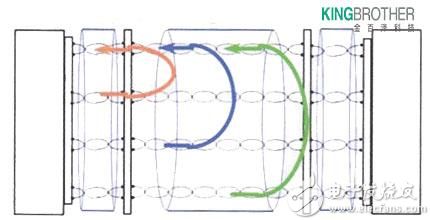

2.傳輸線和參考平面間的距離越小越好,這樣會(huì)使其更緊密地耦合,減少臨近線的干擾。

3.如果不同層的信號(hào)存在干擾,那么走線時(shí)讓這兩層走線方向垂直,因?yàn)橄嗷ゴ怪钡木€,電場(chǎng)和磁場(chǎng)也是相互垂直的,可以減少相互間的串?dāng)_。

4.盡可能使用介電常數(shù)最低的疊層介質(zhì)材料,這樣做可以在給定特性阻抗的情況下,使得信號(hào)路徑與返回路徑間的介質(zhì)厚度保持最小。

5.如果使用防護(hù)布線,盡量達(dá)到其所需要的寬度,并用過(guò)孔使防護(hù)線與返回路徑短接。

6.如果信號(hào)改變參考平面,則參考平面應(yīng)盡量靠近信號(hào)平面。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

淺談PCB串擾及降低方法

什么是串擾?PCB走線串擾詳解

PCB串?dāng)_如何解決

PCB串?dāng)_如何解決

評(píng)論