壹. RISC-V的簡單介紹

RISC-V(念做 Risk-Five)是一種起源于UC Berkeley大學(xué),具有High Quality(高質(zhì)量)、No license fee(無授權(quán)費)、No Royalty(無權(quán)利金)等主要特點的RISC ISA(指令集架構(gòu)標(biāo)準(zhǔn))。

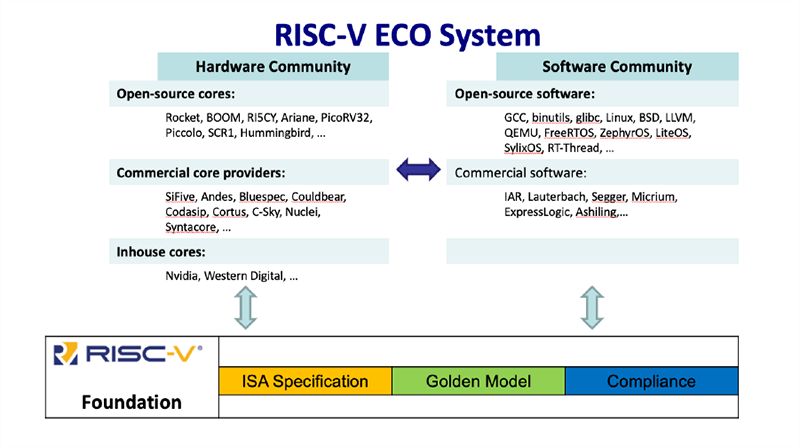

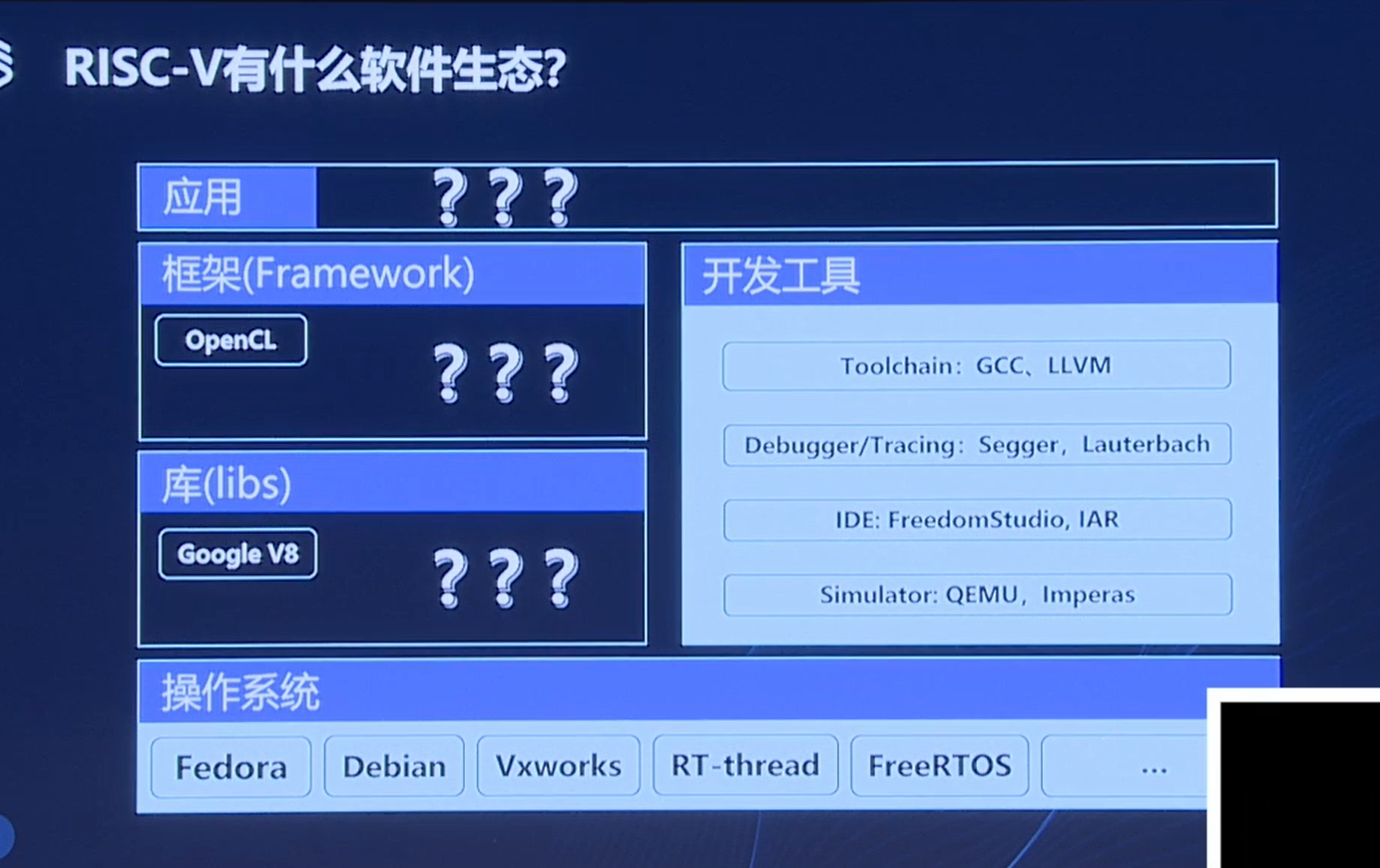

RISC-V標(biāo)準(zhǔn)是由非營利性組織RISC-V基金會維護。RISC-V ISA適用于從微控制器到超級計算機的各種計算體系。在現(xiàn)今的RISC-V業(yè)界已經(jīng)有了很多商用及開源的CPU core,工業(yè)界及學(xué)術(shù)界都在迅速采用該指令集架構(gòu),更重要是獲得越來越多高速成長且用戶共享的軟件生態(tài)支持。更有趣的是,RISC-V生態(tài)是一個不斷演進的,開放,靈活共生的社區(qū)型“生命體”。

貳. RISC-V究竟有何不同之處

1、簡潔

相較于其它商用的ISAs,RISC-V ISA要小很多

2、從零開始的設(shè)計

明確的分離了User及privileged ISA

具有避免對micro-architecture及技術(shù)依賴性的特征

3、為了擴展性及客制化而設(shè)計的模塊化ISA

小的標(biāo)準(zhǔn)化基本ISA,在此基礎(chǔ)上具有多種標(biāo)準(zhǔn)的擴展

用于大量opcode space的sparse和variable-length instruction encoding

4、穩(wěn)定性

基本及標(biāo)準(zhǔn)擴展ISA是固定不變的

通過可選擴展而非更新ISA的方式來增加指令

5、通過社區(qū)進行設(shè)計

由領(lǐng)先的行業(yè)或?qū)W術(shù)專家以及軟件開發(fā)者組成的社區(qū)進行設(shè)計

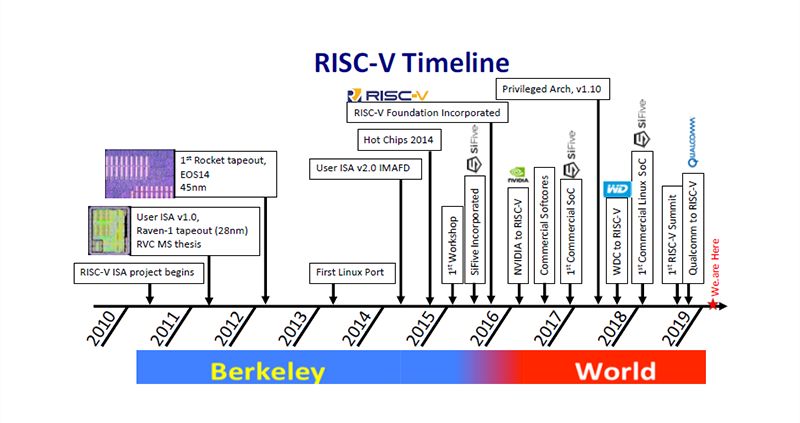

RISC-V的發(fā)展歷程

叁.RISC-V按照時間軸的演進路線

從2015年8月成立RISC-V基金會后,RISC-V ISA正式從UC Berkeley開始走向全世界,在世界范圍內(nèi)得到了極大的關(guān)注,下圖為RISC-V的演進過程中重要的事件。

肆.RISC-V越來越流行的原因

工程技術(shù)人員有時候是“見木不見林”,RISC-V流行的趨勢不是因為在有一些Benchmark方面有10%的提升或者在某一些應(yīng)用情況下能節(jié)省30%的功耗。這個趨勢的原因是新的商業(yè)模式的正在改變一切,新的模式是開發(fā)者先選擇ISA,然后選擇一個Processor的合作伙伴或者干脆選擇自行開發(fā),在此基礎(chǔ)上可以自主選擇是否添加自己的指令擴展甚至做功能裁剪。

Moore’s law(摩爾定律)正逐漸在失效,因為晶片的PPA(性能,功耗及面積)的提升,不再僅僅依靠芯片制造工藝的持續(xù)演進,從Intel,AMD等傳統(tǒng)處理器提供商最近新產(chǎn)品的發(fā)布就能明顯感覺得到。當(dāng)前PPA的提升很多都是基于晶片架構(gòu)的創(chuàng)新,各種AI處理器就是最好的例子, 當(dāng)前的AI晶片的架構(gòu)上有很多Coprocessor(協(xié)處理器),但似乎不需要在一顆芯片上有好多不同的ISA的Coprocessor(據(jù)統(tǒng)計,今天的SoC平均采用6種不同的ISA),如果采用RISC-V ISA的Coprocessor,工程人員可以自由實現(xiàn)不同特定應(yīng)用的Coprocessor,添加不同的功能和標(biāo)準(zhǔn)擴展指令,而全棧軟件依然可以在其上兼容運行。在ISA發(fā)展的歷史上,也出現(xiàn)過開源的ISA,例如很多年前Sun公司開源了Sparc ISA,但是沒有像現(xiàn)在RISC-V那么受到關(guān)注和應(yīng)用,因為在那個時代,Moore’s law依然有效,市場還是沒有對新的計算體系架構(gòu)有那么多的需求。

在現(xiàn)實中,圍繞著私有ISA所建立起來的軟件生態(tài),絕大部分都是ISA所有公司之外的開發(fā)者或者公司完成的,而不是擁有ISA的公司自己實現(xiàn)的。

一個優(yōu)秀ISA的定義和不斷優(yōu)化不是靠一家公司的技術(shù)專家和經(jīng)驗積累能夠完成的,通常需要巨量的工作和知識經(jīng)驗。對于一個開放,自由的ISA,會有很多公司甚至是個人參與標(biāo)準(zhǔn)的制定,設(shè)計和維護提升,而不會像Intel,AMD,ARM公司那樣,只有他們公司的人員才能進行其私有ISA的設(shè)計和相關(guān)工作。即便是某一家公司設(shè)計出來了ISA,但是ISA的驗證工作量是難以估量的,我們面對的現(xiàn)實狀況是,在我們看來像Intel這樣的大公司所采用的如此成熟的私有化ISA設(shè)計出的處理器,依然會有很多嚴(yán)重的ISA層面的漏洞,這是因為Intel一家公司和技術(shù)團隊是無法完成所有的驗證工作的,而且私有的ISA是很難得到開放社區(qū)共同的、透明的驗證的。就像在開源軟件的生態(tài)中,公司幾個人能夠利用社區(qū)中已經(jīng)成熟的開源的軟件設(shè)計或者模塊,這樣就能大大縮短設(shè)計開發(fā)周期和成本投入,真正得推動新應(yīng)用的實現(xiàn)。

如果一個ISA是私有的話,人們無法保證它的延續(xù)性,它將和擁有它的公司所綁定,如果這家公司不再存在,那么大部分情況下這個私有化ISA也將隨之失去延續(xù)性,Alpha以及VAX ISA就是一個非常好的例子,他們隨著DEC公司的消亡而失去了延續(xù)性。

所以綜上所述,我們看不出除了出于知識產(chǎn)權(quán)保護的原因之外,從技術(shù)的角度來講沒理由需要一個封閉的私有化的ISA,需要請各位注意的是,ISA和Processor IP是有區(qū)別,不能等同來看待。我們?yōu)槭裁葱枰媚敲炊嗖煌腎SA,特別是那么多不同的私有化ISA呢?我們?yōu)槭裁床豢紤]使用同一個自由、開放的ISA用于所有的應(yīng)用呢?我們認(rèn)為這就是RISC-V ISA越來越流行的原因。

伍.RISC-V的生態(tài)現(xiàn)狀

RISC-V的生態(tài)現(xiàn)狀

陸.RISC-V ISA設(shè)計認(rèn)證及擴展的過程

RISC-V的生態(tài)是如何通過基金會運營組織及社區(qū)討論及共同開發(fā)的方式進行演進的,這也決定RISC-V ISA所獲得的參與度必將飛速成長。以下,我們將通過RISC-V基金會運做方式進行分別說明。

RISC-V ISA標(biāo)準(zhǔn)的形成過程

RISC-V ISA 標(biāo)準(zhǔn)的形成總結(jié)來講其實就是“大家一起來,不斷迭代反復(fù)實踐,最終一起標(biāo)準(zhǔn)化”,過程步驟如下:

定義需求

收集輸入,舉行會議,“白板級”參數(shù)設(shè)計,完成并公開發(fā)布穩(wěn)定的標(biāo)準(zhǔn)初稿

根據(jù)標(biāo)準(zhǔn)初稿進行設(shè)計硬件實現(xiàn)

根據(jù)實施的硬件進行軟件實現(xiàn)

進行軟硬件的聯(lián)合評估,可能需要重新回到以上第2步進行多次迭代

RISC-V技術(shù)研究小組決定推進該ISA標(biāo)準(zhǔn)的批準(zhǔn)工作

RISC-V技術(shù)委員會將該ISA標(biāo)準(zhǔn)提交RISC-V基金會董事會

RISC-V基金會董事會進行投票批準(zhǔn)

RISC-V社區(qū)設(shè)計按照批準(zhǔn)后的標(biāo)準(zhǔn)進行實現(xiàn),并進行合規(guī)性測試

最終完成ISA標(biāo)準(zhǔn)的替換

柒.Edge Computing(邊緣計算)對處理器的需求

機器學(xué)習(xí)在當(dāng)前的AI應(yīng)用中快速的發(fā)展,系統(tǒng)也會增加更多智能功能。但是在云端的系統(tǒng)(例如數(shù)據(jù)中心)和邊緣系統(tǒng)(例如IoT設(shè)備)對運算能力的需求是不同的,在云端可以采用大型高效的GPU來提供千萬億次的浮點運算能力,Google的TPU 3.0的單芯片的浮點運算能力遠遠超過100 Petaflops (一千萬億的浮點運算),用于深度學(xué)習(xí)或者進行推理。但是在邊緣系統(tǒng)中,就很難采用功耗高的類似GPU或TPU的方案。系統(tǒng)開發(fā)人員必須要考慮采用效率更加高的解決方案,除了滿足計算精度問題外,必須考慮實際應(yīng)用場景對設(shè)備功耗,安裝尺寸以及綜合成本的問題。

將AI優(yōu)勢擴展至邊緣設(shè)備,取代以云端為基礎(chǔ)的資源,能夠大幅降低功耗,同時縮短反應(yīng)時間。 同時,本地數(shù)據(jù)儲存和處理不僅提高安全性,更節(jié)省寶貴的帶寬。通過將 AI整合至邊緣設(shè)備中,即使在網(wǎng)絡(luò)關(guān)閉以節(jié)省功耗的情況下,也能實現(xiàn)實時工作的智能功能。

低功耗解決方案可于網(wǎng)絡(luò)邊緣實現(xiàn)各類應(yīng)用。例如,智能門鈴可通過嵌入式AI功能自動進入待機模式,直到感應(yīng)到有人出現(xiàn);智能電視在沒有觀眾觀看的情況下自動關(guān)機;AI安防攝像頭,只在出現(xiàn)入侵者時才發(fā)出警報,而不是因為自己家里或者鄰居家里狗、貓等其他動物經(jīng)過而出現(xiàn)在攝像頭前的誤報。搭載臉部識別的移動設(shè)備和平板電腦需要用戶在進行臉部識別前喚醒裝置。該解決方案讓這一類設(shè)備能夠在低功耗的狀況下持續(xù)偵測人臉,再喚醒高功耗應(yīng)用處理器執(zhí)行深度識別任務(wù)。

在邊緣設(shè)備的芯片中很多都是以神經(jīng)網(wǎng)絡(luò)(NN)硬件進行機器學(xué)期,這樣就有需求為神經(jīng)網(wǎng)絡(luò)配置硬件加速器,RISC-V CPU中的ALU(算數(shù)邏輯單元) 就可以達到這樣的需求。在這樣的應(yīng)用中,RISC-V體現(xiàn)出了非常精簡高效的基礎(chǔ)指令的特點,用最少的資源進行運算。在基礎(chǔ)指令之上,開發(fā)人員通常采用各種標(biāo)準(zhǔn)的ISA Extension。例如采用Vector Extension ISA(向量擴展ISA)來增強RISC-V處理器,神經(jīng)網(wǎng)絡(luò)的矩陣運算的效率是通過從RISC-V ALU傳輸矩陣數(shù)據(jù),再通過Vector Extension ISA減少甚至消除循環(huán),memory load store(內(nèi)存存取)以及address mapping(地址映射)產(chǎn)生的成本等方法來提升的。

捌.Edge Computing中至關(guān)重要的Security問題

Security對于邊緣計算而言至關(guān)重要。那么RISC-V能否為Edge Computing提供可靠安全的整體方案?一個安全的RISC-V系統(tǒng)究竟有哪一些組件?還有哪一些新的安全技術(shù)?

當(dāng)前RISC-V的體系中有哪一些安全組件

RISC-V ISA中有3種模式,分別為User(用戶), Supervisor(管理員)以及 Machine(機器) 模式。

PMP(Physical Memory Protection) ,采用基礎(chǔ)加邊界的方案,沒有轉(zhuǎn)換,除非系統(tǒng)重置,否則禁止所有的訪問,包括所有模式下程序?qū)︽i定memory區(qū)域的訪問。

有2個保護邊界,第一個為在Supervisor和User模式之間具有保護,第二個為PMPs (Physical memory protection) 機制保護所有的訪問。

地址轉(zhuǎn)換和保護,是基于標(biāo)準(zhǔn)頁面的方案。

RISC-V的一些新的安全技術(shù)

傳統(tǒng)的計算的安全性不夠,因為幾乎所有的程序都能獲取到程序代碼和數(shù)據(jù),編譯器和連接器將源碼模塊合并成單個二進制文件;各個功能模塊(如Stack,Heap,Buffers)通過共享存儲單元來通信;任何bit的源碼都能得到任何bit的數(shù)據(jù);任何一個錯誤指令能夠癱瘓整個系統(tǒng)(如DOS)。

而RISC-V的Security Technical Group(安全技術(shù)組)中的成員 HEX Five公司,他們提出了一個更好的方法,也就是Multi-domain Trusted Execution Environment(多區(qū)域信任執(zhí)行環(huán)境),該技術(shù)也是基于RISC-V標(biāo)準(zhǔn)擴展指令。在2018年,Hex Five先后宣布完成了基于集成SiFive RISC-V CPU以及Andes RISC-V CPU的晶片開發(fā)了類似ARM TrustZone的Trusted Execution Environment。

玖.RISC-V在Edge Computing中的一些應(yīng)用案例

Canaan發(fā)布的Kendryte K210芯片

Kendryte K210芯片是一個非常典型的RISC-V應(yīng)用于Edge Computing的案例。其應(yīng)用包括:目標(biāo)檢測,目標(biāo)識別,聲源定位,聲場成像,語音識別。該SoC晶片的主要組成模塊為:

RISC-V CPU:雙核64bit RISC-V處理器,提供了高性能,高帶寬,高吞吐能力

KPU:神經(jīng)網(wǎng)絡(luò)加速單元,達到1 TOPS 0.35W@400MHz

APU:音頻處理器,支持8路麥克風(fēng)陣列預(yù)處理流程

FFT:512點FFT加速,高吞吐能力,支持16位定點運算

FPU:高性能浮點運算處理單元,雙精度浮點,單精度浮點加速

Kendryte K210芯片主要組成模組

圖片來源:Canaan Creative

Kendryte K210借助RISC-V的開源生態(tài),支持多種即時操作系統(tǒng)(RTOS),包括FreeRTOS,RT-Thread, XBoot, Zephyr, SylixOS等。

BITMAIN發(fā)布的Sophon BM1880芯片

BM1880是一個Coprocessor,在實際應(yīng)用時需要和類似Camera SoC這樣的Host進行連接,數(shù)據(jù)通過USB或者Ethernet進行傳輸,Edge Inference可以在BM1880上完成。應(yīng)用場景主要是Camera(攝像頭),Robot(機器人),Drone(無人機)。該SoC晶片的的主要組成模塊為:

雙核ARM A53處理器

單核64bit RISC-V處理器

16/32bit, 1866/3200MHz, DDR3/LPDDR3/DDR4/LPDDR4

TPU: 運算能力達到1 TOPS@INT8,Winograd convolution達到2 TOPS

On chip memory size:2MB

Video Decoder/Image Codec/VPP:支持2 ways 1080p@30fps H264 decode; JPEG Encode/Decode; Hardware video processing

Interface: Ethernet and USB3.0用于視頻數(shù)據(jù)的傳輸

讓我們來分析一下,BM1880使用的RISC-V core,采用了單核64bit CPU core,按照實際應(yīng)用選擇的ISA為RV64 IMAFDC, 最高頻率達到1GHz,16KiB L1 I-Cache/16KiB L1 D-Cache, RISC-V CPU和VAD (Voice Automatic Detection)模塊配合使用,提供很好的低功耗及VAD的硬件加速能力。我們進一步來分析,RISC-V的模塊化,靈活配置的ISA究竟能夠給BM1880帶來什么好處。

選擇了M extension ISA是因為,M extension提供了整數(shù)乘法及除法運算能力,能提供高性能的乘法及除法運算的硬件加速功能;

選擇A extension是因為應(yīng)用的軟件以及操作系統(tǒng)需要CPU支持Atomic Operation(原子操作);

選擇同時支持F及D extension是因為需要用到單精度及雙精度浮點運算能力;

選擇C extension是因為可以能夠通過該壓縮指令擴展,在編譯器編譯代碼時得到更高的code density(代碼密度)和更高的運行效率;

拾. 總結(jié)

RISC-V ISA在當(dāng)前的行業(yè)應(yīng)用中,主要是嵌入式應(yīng)用為主,在嵌入式應(yīng)用中,由以用于邊緣計算設(shè)備為主,邊緣設(shè)備的AI及Inference(推理)深度結(jié)合的設(shè)計架構(gòu),在未來很長一段時間內(nèi),都將是保持高增長的趨勢,這是RISC-V技術(shù)與Edge Computing最好的結(jié)合點,我們可以預(yù)期在2019年RISC-V將Vector Extension ISA 標(biāo)準(zhǔn)批準(zhǔn)通過后,有更多的Core以及軟體出現(xiàn),將更有利于邊緣計算晶片PPA和靈活度的提升,一定將助力其更上一層樓。

-

微控制器

+關(guān)注

關(guān)注

48文章

7570瀏覽量

151623 -

RISC-V

+關(guān)注

關(guān)注

45文章

2294瀏覽量

46249 -

邊緣計算

+關(guān)注

關(guān)注

22文章

3103瀏覽量

49133

原文標(biāo)題:RISC-V令A(yù)I邊緣計算晶片發(fā)展更上一層樓

文章出處:【微信號:RTThread,微信公眾號:RTThread物聯(lián)網(wǎng)操作系統(tǒng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

rIsc-v的缺的是什么?

2024 RISC-V 中國峰會:華秋電子助力RISC-V生態(tài)!

科普RISC-V生態(tài)架構(gòu)(認(rèn)識RISC-V)

RISC-V 生態(tài)架構(gòu)淺析

分析RISC-V架構(gòu)的不同之處

【RISC-V專題】芯昇科技RISC-V生態(tài)開發(fā)板首發(fā)試用

賽昉科技成立RISC-V Multimedia SIG,推動openKylin on RISC-V生態(tài)發(fā)展

RISC-V規(guī)范的演進 RISC-V何時爆發(fā)?

RISC-V中國峰會:RISC-V產(chǎn)業(yè)及生態(tài)發(fā)展

RISC-V有什么軟件生態(tài),RISC-V IP在芯片中的應(yīng)用

如何建設(shè)RISC-V軟件生態(tài)?

RISC-V究竟有何不同之處?RISC-V的生態(tài)現(xiàn)狀

RISC-V究竟有何不同之處?RISC-V的生態(tài)現(xiàn)狀

評論