摘要:提出了一種基于場路結合、對具有屏蔽機殼的電子設備進行系統級電磁敏感性(EMS)仿真分析的新方法. 該方法采用有限元法計算外部電場分布, 對電場沿固定路徑積分, 得到所需的表面干擾電壓, 將外部電磁干擾對內部電路的影響等效為電壓源的作用, 再利用基于電路模型和全波分析相結合的方法對內部高速電路進行EMS 仿真分析, 彌補了以往在EMS 分析時只以實驗為主,缺乏理論依據的缺陷. 實例仿真分析表明, 該方法簡單、直觀, 不僅可以詳細分析電子設備內部高速電路中干擾的傳播情況, 而且可以對內部高速電路進行優化設計, 提高了系統的抗干擾性.

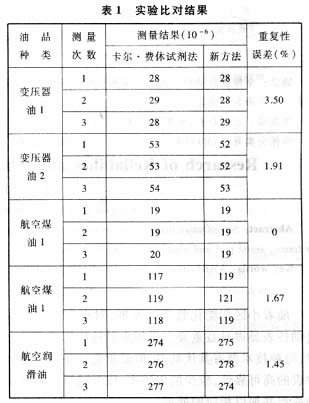

近年來, 由于電子設備的集成化和高速化, 加劇了印刷電路板(PCB)上連接線的傳輸線效應, 增大了電路間的互相干擾, 降低了電子設備受干擾信號的幅值和能量, 從而使得電子設備的電磁敏感性(EMS)問題變得越來越突出. 因此, 對電子設備的電磁敏感性進行仿真分析具有重要的理論和實用價值.

電子電路通常總是罩著金屬屏蔽機殼以減少周圍環境對電子電路的干擾, 然而機殼并不總是密封的, 周圍的電磁干擾會通過孔、槽和連接線這樣一些耦合通道進入電子設備內部的敏感器件, 影響其正常工作, 而對于大多數的電子設備, 連接在機殼外部的信號線和電源線是引進外部干擾的主要通道之一. 因此, 研究帶有屏蔽機殼和外部電纜的電子設備的電磁敏感性具有普遍意義.

目前, 人們已經在電子設備印刷電路板(PCB)的EMS 方面做了大量的仿真研究工作[ 1-9] , 但針對電子設備系統級的EMS 方面的仿真研究工作在國外還只是剛剛起步, 國內至今還未見文獻報道. 參考文獻[ 10] 首次提出了利用矩量法(MOM)計算流過信號線與機殼結合點處的感應電流, 將外部電磁干擾對內部電路的影響等效為由短路電流和等效電阻組成的等效源模型的思想, 并將其方法應用于多層PCB 板連接線的EMS 分析中. 參考文獻[ 11] 又將上述方法擴充到具有集成電路插件的多層PCB 板的EMS 仿真分析中. 但是, 由于電子設備的實際使用環境以及信號線與機殼內部電路連接方式的差別, 究竟應該如何計算外部電磁干擾, 以及如何等效外部電磁干擾對內部電路的影響, 還有待于進一步研究.

本文在對被屏蔽的電子設備的EMS 進行分析時, 提出了采用有限元法計算外部電場分布, 將外部電磁干擾對內部電路的影響等效為電壓源的方法, 在此基礎上采用基于電路模型和全波分析相結合的方法對內部高速電路進行了EMS 仿真分析,并對內部高速電路進行了優化設計.

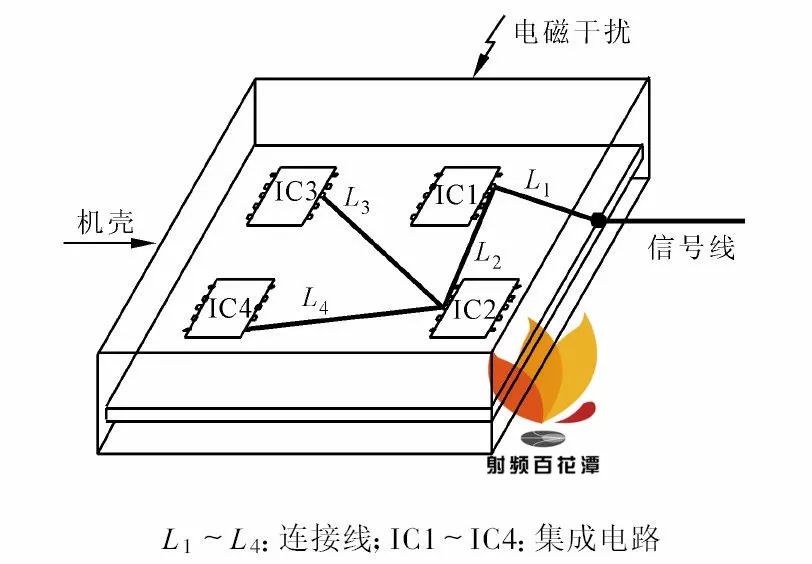

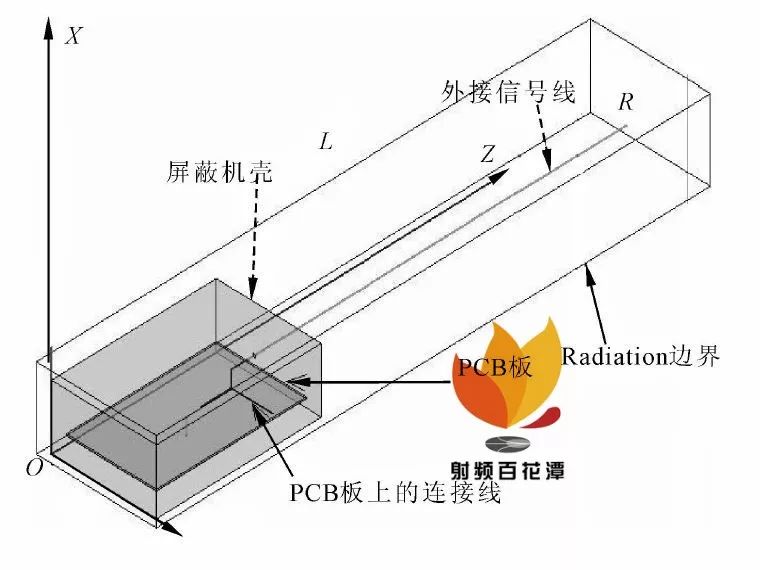

1 方法描述本文在對電子設備進行系統級電磁敏感性分析時將其分為內外兩個區域, 外部區域由屏蔽機殼和信號線組成, 內部區域由內部高速電路組成, 如圖1所示. 具體方法如下:

①利用有限元法仿真被平面電磁波干擾照射的外部屏蔽機殼和信號線, 計算電場分布, 將其電場沿固定路徑積分得到信號線與機殼結合處的表面干擾電壓, 此干擾電壓即為內部高速電路的輸入噪聲源;

②采用傳統的基于電路的模型、描述器件外部特性的IBIS(Input /output Buf fer Informatio n Specification)模型以及傳輸線的分布模型和全波模型來建立由PCB 板上的連接線、分立元件和集成電路(IC)插件組成的內部高速電路的仿真模型;

③將第①步計算得到的表面干擾電壓作為第②步得到的內部高速電路仿真模型的輸入, 分析由信號線耦合的輸入噪聲對內部高速電路的影響;

④對內部高速電路進行優化設計, 使其對輸入噪聲的敏感程度達到最低.

圖1電子設備結構圖

1. 1利用電磁場理論計算外部干擾電壓源

首先假設電子設備周圍的電磁干擾為均勻平面諧波, 且有

式中:Ei 表示入射電場;E0 是入射電場幅度;k 是傳播常數;^z 是諧波的傳播方向.

由于假設屏蔽機殼為理想導體, 因此電磁波不可能穿透導體, 而只是入射到機殼表面上感應出表面電流. 現假設由感應電流產生的散射電場為Es ,機殼表面的法向量為^n , 則在機殼表面上應用邊界條件^n ×(Ei +Es)=0 , 可得到機殼表面切線方向的散射電場為

而對于時諧電磁場而言, 在均勻、線性、各向同性、無源以及不導電的媒質區域中, 根據麥克斯韋方程組可得到如下表達式

式中:ε、μ分別為周圍媒質的介電常數和磁導率.時諧電場表達式為

于是, 可得到假設為均勻平面諧波的電磁干擾在傳播過程中滿足的關系式為

式中:傳播常數k =ω(με)12. 由(2)式知, 機殼表面的散射場應滿足邊界條件

因此, 求解式(5)就可得到機殼表面散射場的電場分布. 本文利用Ansof t HFSS 軟件求解該散射場. 在應用Ansof t HFSS 軟件求解式(5)時, 選擇矢量亥姆赫茲方程作為支配方程, 其形式為

式中:εr 、μr 分別為復相對介電常數和復相對磁導率(考慮了介質的損耗);k0 為真空中的傳播常數.根據變分原理可得到支配方程式(6)對應的泛函為

求解式(7)即可得到機殼表面的電場分布. 考慮到理想導體的趨膚效應, 對表面電場沿電場方向積分, 得到的就是信號線與機殼結合點處的表面干擾電壓,這個電壓即為內部高速電路的EMS 仿真分析的激勵源.

1. 2 建立內部高速電路模型通常, 電子設備的內部電路由分立器件、集成電路和高速傳輸線組成.對于電阻、電容、電感和晶體管一級的分立器件, 可采用建立在電路基本元器件(如晶管、電阻、電容等)工作機理和物理細節之上的SPICE 模型進行電路仿真.

對于集成電路, 應采用IBIS 模型對其進行仿真. IBIS 模型是通過一簇電流/電壓和電壓/時間曲線來描述各個器件管腳的輸入輸出特性的. 因為IBIS模型用一種標準的文件格式記錄了如驅動源輸出阻抗、上升/下降時間及輸入負載等參數, 因此適合于電子設備內部高速集成電路的振蕩和串擾等高頻效應的計算與仿真.

對于內部PCB 板上的連接線來說, 當工作在低頻時, 只須建立其集總模型, 將傳輸線用集總參數的電路等效即可, 而當傳輸線工作在較高頻率時, 由于會產生較明顯的傳輸線效應, 故必須為其建立分布模型, 即在準TEM 模式假設時, 將傳輸線劃分為若干單元段, 每段用特征參數R 、L 、G、C 組成的網絡等效, 建立其電報方程, 用Hspice 軟件進行仿真, 當時鐘頻率繼續上升到達GHz 時, 就必須建立其全波模型, 利用A nsof t HFSS 軟件對其進行三維空間等效分析.

2 仿真實例為了說明上述方法, 本文所使用的仿真模型由3 部分組成:①金屬屏蔽機殼;②連接內部PCB 板的信號線或電源線;③放置在金屬機殼內部的雙層PCB 板和4 片集成電路插件. 其結構如圖1 所示.仿真步驟如下:

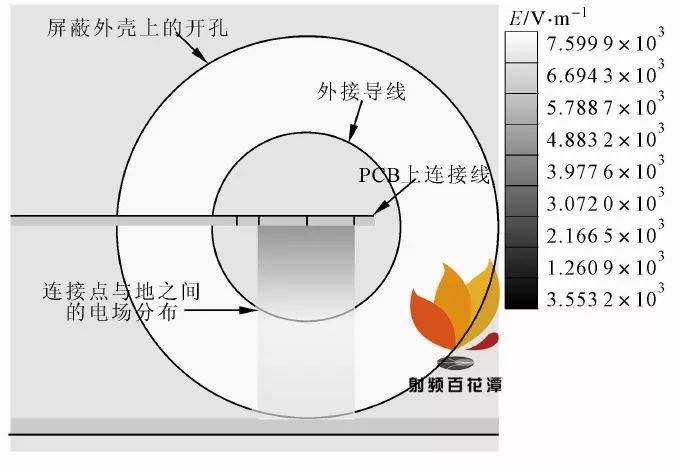

(1)計算當入射電場幅值E0 =1 V /m 時的干擾電壓. 采用Ansof t HFSS 軟件仿真時的HFSS 模型如圖2 所示, 其中金屬屏蔽機殼外形尺寸為L ×W ×H =14 cm ×10 cm ×6 cm , 圓柱體的外接信號線直徑為2 mm , 長度為40 cm , 材質為銅, PCB 板為雙面板, 上層為銅質帶狀連接線和集成電路插件, 下層為銅質接地層, 中間是介電常數為2. 2 的絕緣介質Rogers RT /duroid 5880. 圓柱體的外接信號線通過屏蔽機殼上的一個直徑為0. 2 mm 的圓孔與PCB板上的第一段帶狀連接線L1 相連(參考圖1), 接地層的外形尺寸為L ×W ×H =12 cm ×8 cm ×0. 01cm , 通過一條短的細線與機殼相連. PCB 板上的4段帶狀連接線都為銅線, 其橫截面相同, 為W ×H=0. 5 mm ×0. 06 mm , 長度分別為L1 =1 cm , L2 =1. 37 cm , L3 =2 cm , L4 =2. 75 cm(參考圖1).

圖2HFSS 模型

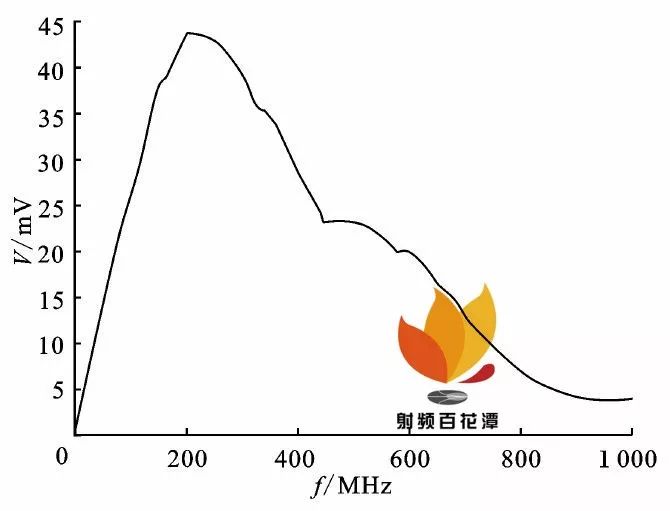

當頻率為200 MHz 時, 外部干擾在信號線與PCB 連接點處的積分路徑上的電場分布如圖3 所示, 由此得到的連接點處不同頻率時的干擾電壓如圖4 所示.由于假設屏蔽機殼為理想導體, 因此, 建模時將其設為“perfect E”邊界條件, 按照軟件要求在模型外面加了一個外形尺寸為L ×W ×H =46 cm ×12 cm ×7 cm 的長方體, 作為“Radiatio n”邊界條件.

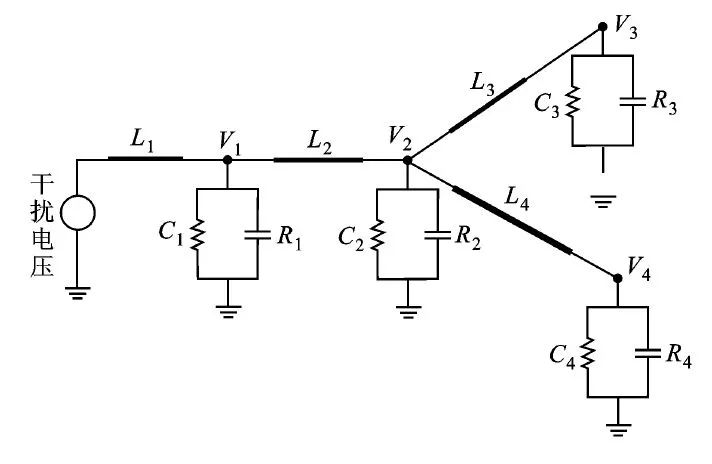

(2)建立內部高速電路的仿真模型. 建模時首先將圖1 所示的內部PCB 板上的互連網絡等效為由電阻R 和電容C 組成的電氣等效電路, 如圖5 所示. 利用A nsof t HFSS 軟件建立帶狀連接線的全波模型, 輸出其Hspice 等效電路仿真文件.

圖3 200 M Hz 時連接點處的電場分布

圖4 連接點處的干擾電壓

再利用Hspice 建立整個內部高速電路的仿真模型.

圖5 內部PCB 板的電氣等效電路

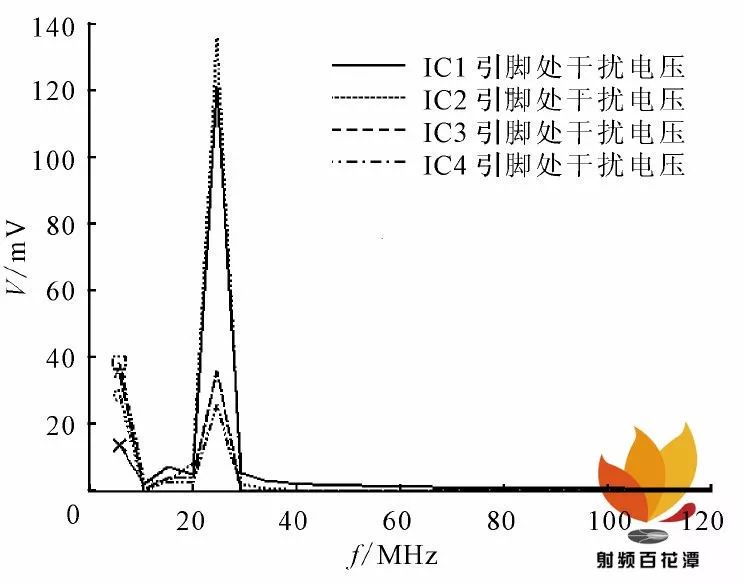

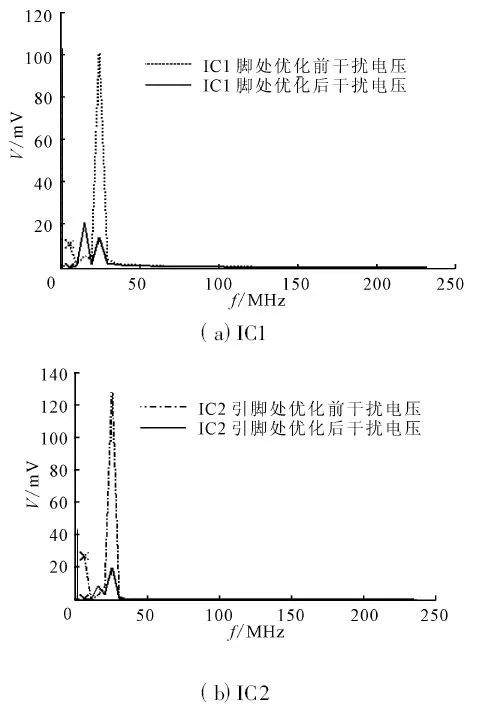

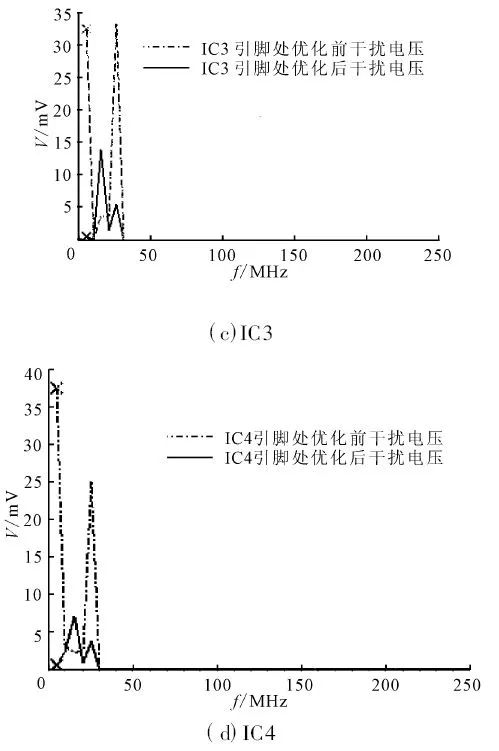

(3)將第(1)步得到的干擾電壓, 作為第(2)步得到的模型的輸入, 由H spice 軟件仿真分析感應到各個芯片輸入端的干擾電壓. 仿真結果如圖6 所示. 由圖6 可知, 當幅值為1 V /m 的平面電磁波干擾照射到圖1 所示的具有屏蔽機殼的電子設備上時, 由信號線引入并感應到電路各處的干擾電壓頻率主要集中于25 MHz 左右, 感應到芯片IC1 和IC2 處的干擾電壓幅值高于芯片IC3 和IC4 處的干擾電壓幅值, 且幅值較大.

圖6內部電路各處的干擾電壓

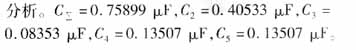

(4)為了使內部電路各處的干擾電壓盡量小, 對圖5 所示的網絡結構進行了優化設計. 優化前各段連接線長度分別為L1 =1 cm , L2 =1. 37 cm , L3 =2cm , L4 =2.75 cm , 優化設計在各連接線原來長度的±20 %范圍內進行. 優化設計結果為:當各連接線長度分別為L1 =1. 2 cm , L2 =1. 37 cm , L3 =1. 8 cm ,L4 =2. 75 cm 時, 感應到各處的干擾電壓信號最小,如圖7 所示. 由圖可知, 優化設計后的內部電路各處感應的干擾電壓確實比優化前減小了很多, 最為明顯的是在IC2 處, 干擾電壓從原來的138 mV 減小到優化后的20 mV. 由此可以得出結論:PCB 板上的連接線長度的匹配對提高系統的抗干擾能力起著至關重要的作用.

3 結論本文提出了一種分析具有屏蔽機殼的電子設備系統級EMS 的場路結合的新方法, 其特點是:對采用有限元法計算的屏蔽機殼表面電場直接積分, 得到信號線與機殼結合點處的表面干擾電壓;將外部干擾對內部高速電路的影響等效為電壓源的作用.本文提出的方法簡單、直觀, 避免了以往在EMS 分析時只以實驗為主、缺乏理論依據的缺陷, 適用于大多數工作在電磁波干擾環境中的電子設備系統級的EMS 仿真分析. 另外, 利用本文所述方法建立的高速電路仿真模型, 不僅可以詳細分析電子設備內部高速電路中干擾的傳播情況, 對諸如串擾、延遲等信號完整性進行仿真, 而且可以對內部高速電路進行優化設計, 以提高系統的抗干擾性.(參考文獻略)

-

集成電路

+關注

關注

5387文章

11530瀏覽量

361633 -

印刷電路板

+關注

關注

4文章

793瀏覽量

35157 -

電磁

+關注

關注

15文章

1133瀏覽量

51795

原文標題:20190317---具有屏蔽機殼的電子設備系統級電磁敏感性分析方法

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

電子設備中基于接地與屏蔽的電磁兼容性設計

基于頻響函數測量脈沖磁場屏蔽效能的新方法

分析芯片內部不同硬件資源對于SEU效應敏感性的問題

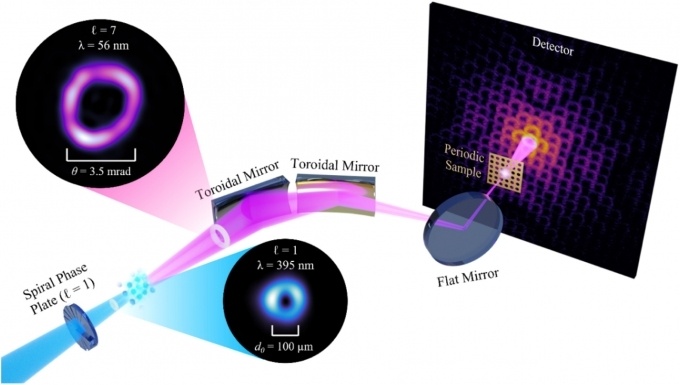

研究人員創造了一種產生與激光密切相關的超短光脈沖新方法

一種復制和粘貼URL的新方法

溫度敏感性藥品不同儲運容器的溫度監測方法

一種基于場路結合、對具有屏蔽機殼的電子設備進行系統級電磁敏感性仿真分析的新方法.

一種基于場路結合、對具有屏蔽機殼的電子設備進行系統級電磁敏感性仿真分析的新方法.

評論