這次奉上與LPC5500“核心”相關的“硬核”技術——雙核,以饗讀者。誠然,MCU雙核已不是什么新鮮玩意兒。但是,LPC5500博采了LPC4300和LPC54110這兩個系列所長,使得雙核更簡單實用。

LPC5500雙核基本架構

雙核并不高深,所謂雙核就是兩個CPU——中央處理單元,也就是一個MCU芯片內置了兩個CPU。

和之前支持雙核的LPC系列一樣,針對于MCU嵌入式應用,LPC5500依然采用簡單的非對稱架構,即一個主CPU,一個從CPU,這類似于有些產品采用主MCU和從MCU的設計。只是支持雙核的MCU,是共享此MCU所有的存儲器和外設接口資源。

共享就帶來競爭的問題,處理不當則影響性能。LPC5500有配套的系統架構來使得此共享可轉化為并行的,從而盡量避免競爭,來保證性能不被影響。

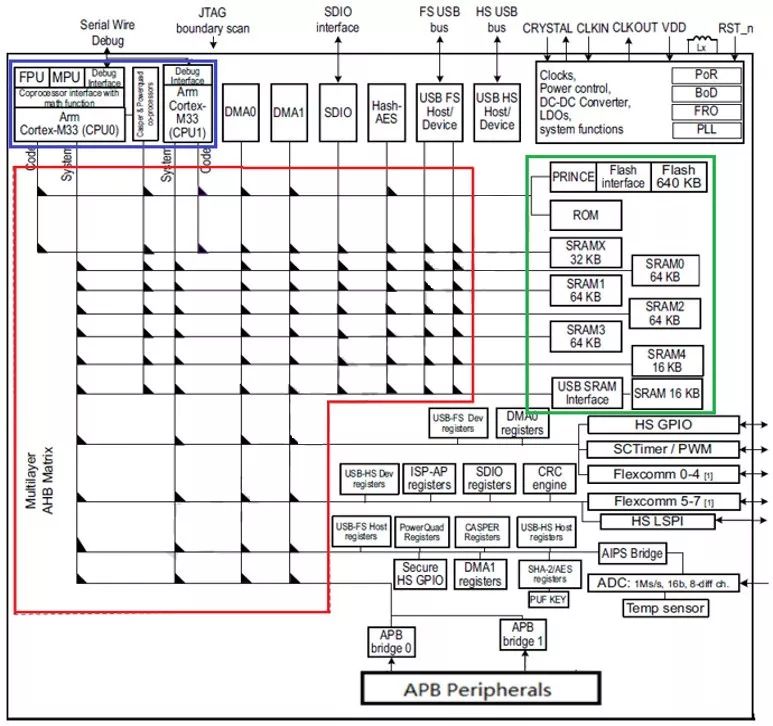

應對競爭架構上的考慮,如下圖所示,主要有兩條:

內部AHB總線是多層矩陣架構;

分離出多塊獨立的SRAM。

圖中所示:紅色框是多層AHB矩陣總線;綠色框是多塊分立的存儲塊。主CPU和從CPU的代碼數據可存放在不同存儲塊中,它們和圖中左下角大量外設接口并行的掛在矩陣總線上。

這樣,藍色框中的雙核CPU0和CPU1,可以同時并行地對存儲塊和外設接口進行訪問,即程序可以同時運行。如此,則雙核的威力能夠得以充分的發揮。

至此,我們初步認識了LPC5500雙核,了解了其基本框架。但是,這好比我們只是遠遠的看見了一個人,大概知道其身形,他具體容貌怎樣的呢?讓我們一起往下看

LPC5500雙核面貌特征

上面提到,LPC5500雙核分為主從,主CPU命名為CPU0,從CPU命名為CPU1。它們都是基于ARM Cortex-M33的。

它們的基本配置構成如下:

1、CPU0 (r0p3版):

頻率最高可達100MHz

TrustZone、DSP、浮點單元和存儲保護單元(MPU)

內置嵌套向量中斷控制器(NVIC)

串行線調試接口(SWD)

內置嵌套向量中斷控制器(NVIC)

串行線調試接口(SWD)

系統嘀嗒定時器(System tick timer)

2、CPU1 (r0p3版):

頻率最高可達100 MHz

內置嵌套向量中斷控制器(NVIC)

串行線調試接口(SWD)

系統嘀嗒定時器(System tick timer)

顯然,作為從的CPU1比主CPU0少了TrustZone、浮點單元(FPU)等,這使得主CPU0天然地計算處理能力更強。

但是賦予主CPU0這些亮點,不是讓它做顏值擔當,而是任務擔當的。這讓我們自然想到雙核的典型應用——相信這也是大家很關心的。

LPC5500雙核典型應用

LPC5500的雙核典型應用,即基本應用思路,與之前LPC4300和LPC54110一樣。

主CPU用來做處理計算任務(比如算法),從CPU負責外設實時控制和數據傳輸。

這樣,能充分利用雙核達到更好性能。參見下圖:

哦,LPC5500雙核很“酷”的樣子,有點“喜歡”上它了,可是,相愛容易相處難啊?!

不要擔心,難,那是因為不懂得如何“相處”。

接下來,讓我們來聊聊如何和LPC5500雙核“相處”——雙核的實現,這主要涉及到以下內容:雙核啟動;雙核通訊;雙核調試。

1雙核啟動

對于單核MCU,上電啟動過程簡單明了,如單身狗的生活簡單自由,該干啥干啥,不能指望也無需考慮他人。

兩人世界就需要協商著行動了,LPC5500采取了和最早LPC4300系列類似的雙核啟動機制,即出廠默認并固定一個核為主,另一個為從,不能更改,“專制”卻簡單易用。

隨后的LPC54110系列則實行“民主”機制,兩個核可以輪流坐莊,即用戶可以在啟動過程中選擇其中之一為主核,這樣提供了靈活性,但略微復雜。

為了簡單起見,如今新的LPC5500雙核使用固定的主從模式。

LPC5500上電時,自然地按照主從,主核CPU0如單核一樣直接啟動,從核CPU1則hold住不動——這由硬件自動完成。

主核啟動后負責初始化運行環境,然后配置好從核的啟動地址(即從核代碼映像運行的起始地址),最后釋放從核CPU1——這些由軟件完成。這時,主從雙核就分別如同單核一樣同時運行它們各自的代碼了。

要讓雙核“和諧”運作,關鍵是要讓兩個核的代碼映像存儲和運行空間獨立互不干擾(參見前面關于多層總線矩陣和多塊存儲塊的介紹),這點具體實現方法是靈活的,比單核來得復雜些。這里就不具體展開,有需要的可找相關資料學習,比如,我們有篇應用筆記通過測試雙核coremark分數,提供了一種達到最好性能的實現方法。不關心這些細節也不用擔心,NXP已經提供了相關SDK庫可直接借用。

2雙核通訊

當兩個核都運行起來后,它們可以像兩個不同行業的人,各自做著自己的本職工作,默默為社會貢獻自己的力量,老死不相往來。但大多數應用中,兩個核除了各司其職,還需要互相通訊,協同工作。

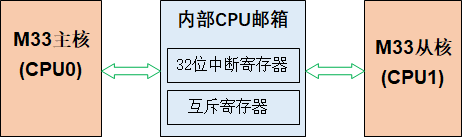

LPC5500提供了一套簡單的硬件通訊機制,叫內部CPU郵箱通訊機制,可以適用于大多數嵌入式系統雙核的通訊應用。

這套機制從LPC54110系列繼承而來,最早的LPC4300系列雙核通訊幾乎完全靠軟件來實現,占用資源,且給使用帶來不少難度。目前這套機制,簡單易用,但不死板,留給用戶一定靈活發揮空間。

它主要提供了兩種寄存器,一種是32位的CPU中斷寄存器,兩個CPU都能訪問它,32位中只要有一位不為零,就能產生中斷請求,且每一位可代表一個不同狀況,比如事件或者狀態,這完全可由用戶自己定義。

這樣CPU間就可相互實時通訊了,比如一個CPU完成某項任務,寫入一個非0值到此寄存器,發出中斷信號,另一CPU中斷后讀取此值,來決定后續工作。

通訊的一大需求就是同步,這就需要另一個叫做互斥寄存器的來完成,它只有第0位(bit0)可用,復位后默認值為1。當讀此寄存器時,讀出數值的同時這位自動被清0;當寫它時,這位將再次被置為1。

此正是互斥量的特性,以用于實現CPU間對任何共享資源的握手同步。例如,當一個CPU要訪問某共享資源時,先讀此寄存器,若讀到的是1,表示資源可用,同時1被自動清為0;若讀到0,則表示資源被占用;在CPU用完共享資源時,即寫此寄存器,使其置1,表示釋放了資源為可用。

這套郵箱機制簡單框架圖如下:

順便提下,我們在LPC5500 SDK包中還提供了一套開源多核軟件開發包,包括庫和大量例程。通過庫的API提供了支持用戶實現復雜的多核通訊機制。

這套多核SDK的庫代碼包含在LPC5500SDK包以下路徑:

例程則在:

3雙核調試

LPC5500的雙核都支持SWD調試模式,就調試的級別來說,它們是”平等”的。實際實現時,每個核一般有自己的工程,它們各自的調試和單核無異。

但在兩個核有關聯時(即前面提到的雙核啟動和雙核通訊過程),調試要有所注意,關鍵就是要真正理解了這兩個過程機制,依據這兩個機制的特點進行調試,則基本沒什么問題。

-

mcu

+關注

關注

146文章

17141瀏覽量

351061 -

存儲器

+關注

關注

38文章

7485瀏覽量

163790 -

cpu

+關注

關注

68文章

10858瀏覽量

211643

原文標題:【硬核干貨】LPC5500——簡便易用的雙核技術

文章出處:【微信號:Zlgmcu7890,微信公眾號:周立功單片機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于恩智浦LPC5500系列MCU的OKDO E1開發板詳解

基于Cortex M33的LPC5500系列MCU主要功能特性介紹

恩智浦LPC55S16 MCU獲得了PSA 2級和SESIP 2級保證認證

非對稱雙核MCU基礎知識及核間通信

LPC55S69 Flashmagic不編程的原因?

LPC55S69的雙核性能技巧是什么?

LPC5500 Flash過度編程是否可行?

非對稱雙核MCU基礎知識及核間通信

LPC5500雙核基本架構!LPC5500雙核面貌特征

LPC5500雙核基本架構!LPC5500雙核面貌特征

評論