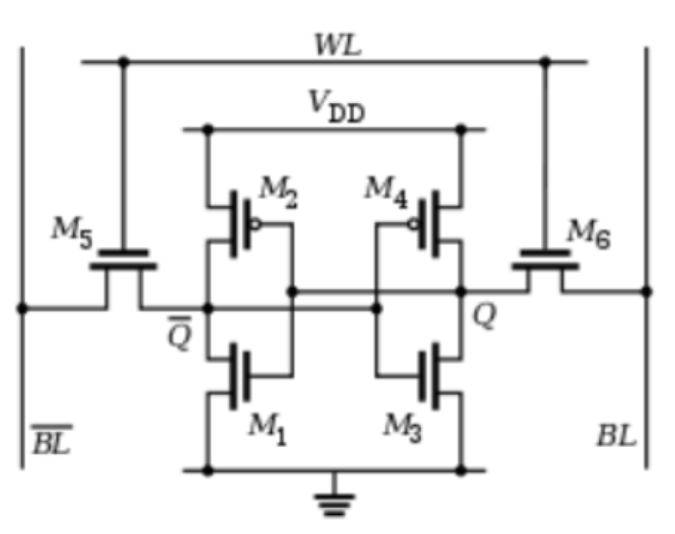

靜態(tài)隨機存取存儲器(SRAM)是隨機存取存儲器的一種。所謂的“靜態(tài)”,是指這種存儲器只要保持通電,里面儲存的數據就可以恒常保持。相對之下,動態(tài)隨機存取存儲器(DRAM)里面所儲存的數據就需要周期性地更新。然而,當電力供應停止時,SRAM儲存的數據還是會消失,這與在斷電后還能儲存資料的ROM或閃存是不同的。

SRAM不需要刷新電路即能保存它內部存儲的數據。而DRAM每隔一段時間,要刷新充電一次,否則內部的數據即會消失,因此SRAM具有較高的性能,但是SRAM也有它的缺點,即它的集成度較低,功耗較DRAM大 ,相同容量的DRAM內存可以設計為較小的體積,但是SRAM卻需要很大的體積。同樣面積的硅片可以做出更大容量的DRAM,因此SRAM顯得更貴。

一種是置于cpu與主存間的高速緩存,它有兩種規(guī)格:一種是固定在主板上的高速緩存;另一種是插在卡槽上的COAST擴充用的高速緩存,另外在CMOS芯片1468l8的電路里,它的內部也有較小容量的128字節(jié)SRAM,存儲我們所設置的配置數據。

還有為了加速CPU內部數據的傳送,自80486CPU起,在CPU的內部也設計有高速緩存,故在Pentium CPU就有所謂的L1 Cache(一級高速緩存)和L2Cache(二級高速緩存)的名詞,一般L1 Cache是建在CPU的內部,L2 Cache是設計在CPU的外部,但是Pentium Pro把L1和L2 Cache同時設計在CPU的內部,故Pentium Pro的體積較大。Pentium Ⅱ又把L2 Cache移至CPU內核之外的黑盒子里。SRAM顯然速度快,不需要刷新操作,但是也有另外的缺點,就是價格高,體積大,所以在主板上還不能作為用量較大的主存。

-

sram

+關注

關注

6文章

767瀏覽量

114675 -

隨機存取存儲器

+關注

關注

0文章

44瀏覽量

8960

發(fā)布評論請先 登錄

相關推薦

關于hpm6364的femc同時使用外接sdram和sram的問題

SRAM和DRAM有什么區(qū)別

SRAM1/2/3可以使用LPDMA通過LPTIM觸發(fā)ADC4搬運數據到SRAM4嗎?

請問如何使用片外SRAM?

C語言指針存在SRAM里面嗎

Microchip推出容量更大、速度更快的串行SRAM產品線

先進工藝下的SRAM功耗和性能挑戰(zhàn)

Microchip推出容量更大、速度更快的串行 SRAM產品線

Microchip Technology擴展了旗下串行SRAM產品線,容量最高可達4Mb

GPIF ii sram-master mode如何配讀寫地址?

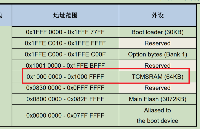

GD32F4的TCMSRAM(緊耦合SRAM)該如何使用?

SRAM CLA和SRAM有什么區(qū)別

賽普拉斯的NV-SRAM接口解決方案

sram是什么意思

sram是什么意思

評論