隨著低功耗的手持式設(shè)備越來越多,混合有 5 V、3.3 V、2.5 V 和 1.8 V 器件的印刷電路板也越來越多普遍,這使得 JTAG 鏈的設(shè)計成為一項極具挑戰(zhàn)性的任務(wù)。設(shè)計者師不僅必須確定 JTAG 鏈的工作電壓,同時還必須確定這些使用不同電壓的器件的安放順序。本文比較了多種設(shè)計多電壓 JTAG 鏈的方法,并提供了一些有關(guān)執(zhí)行強(qiáng)大的無故障設(shè)計的提示和技巧。

菊花鏈,或通過其 JTAG 端口連接多個 DSP、FPGA、CPLD 和其他邏輯器件,使得它們可以通過單個 JTAG 連接器進(jìn)行控制。菊花鏈常用于具有多個 JTAG 器件的電路板,它可以將 TDI 和 TDO 引腳連接在一起以形成一個串行路徑。鏈的輸入是第一 個器件的 TDI;鏈的輸出是最后一個器件的 TDO。所有器件的 TRST、TCK 和 TMS 引腳均并行連接。通過提供一些可安裝或移除(具體取決于所需的目標(biāo)器件)的跳線,菊花鏈允許鏈中的一個或多個器件被繞過以進(jìn)行調(diào)試目的。理論上,通過菊花鏈連接的器件數(shù)量可以是無限的,但是如果菊花鏈中的器件數(shù)量超過八個,就會經(jīng)常出現(xiàn)時序問題和間歇性的崩潰,特別是時鐘速率較高時,更是如此。

當(dāng)一個鏈中有超過四個左右的器件時,為了滿足 JTAG 時序要求,應(yīng)在 TCK 和 TMS 上安裝緩沖器以保持信號的完整性,并且每個緩沖器驅(qū)動的器件數(shù)量不應(yīng)超過四個。例如,一個具有六個器件的菊花鏈需要兩個用于 TCK 的緩沖器和兩個用于 TMS 的緩沖器。驅(qū)動器必須高速運行(低傳播延遲),并有足夠的力量來驅(qū)動四個或更多個器件。

硬件工程師可能需要用菊花鏈連接多個具有不同 I/O 電壓的器件。通過一個鏈連接所有器件可能并非是一個最佳的解決方案,因此設(shè)計師應(yīng)該考慮對菊花鏈進(jìn)行分區(qū),從而滿足專有調(diào)試工具的要求。可能需要電平轉(zhuǎn)換器來應(yīng)對多種電壓水平,并且必須保持信號的完整性。設(shè)計和測試的復(fù)雜性日益增加,并且需要具有 IEEE 1149.1 專業(yè)知識來集成和測試系統(tǒng)。下面介紹了兩種實現(xiàn)多電壓 JTAG 鏈的方法。

適用于每個電壓系列的單獨 JTAG 鏈

這種方法推薦用于多個器件具有相同 I/O 電壓的場合,它把所有具有相同 JTAG I/O 電壓的器件放在一個鏈中,從而為每個電壓使用單獨的鏈。每個鏈支持同一類別的所有器件,消除了其他器件無法正常工作的機(jī)率,并且在其他廠商必須連接 JTAG 鏈時可以減少混淆。圖 1 顯示了具有相同 I/O 電壓器件的 JTAG 鏈。在此情況下,不需要使用電壓轉(zhuǎn)換器 (VT)。

多電壓 JTAG 鏈

有時, 把所有 JTAG 器件放在單個鏈中會更好。當(dāng)每個電壓系列中的器件數(shù)量不足以創(chuàng)建單獨的 JTAG 鏈時,推薦采用此方法。要在一個 JTAG 鏈中成功連接兩個具有不同電壓的器件,必須滿足以下要求:

驅(qū)動器的 VOHmin(最低高輸出電壓)必須大于接收器的 VIHmin(最低輸入高電壓)。

驅(qū)動器的 VOLmax(最高輸出低電壓)必須小于接收器的 VILmax(最高輸入低電壓)。

來自驅(qū)動器的輸出電壓不得超過接收器的 I/O 電壓容差。

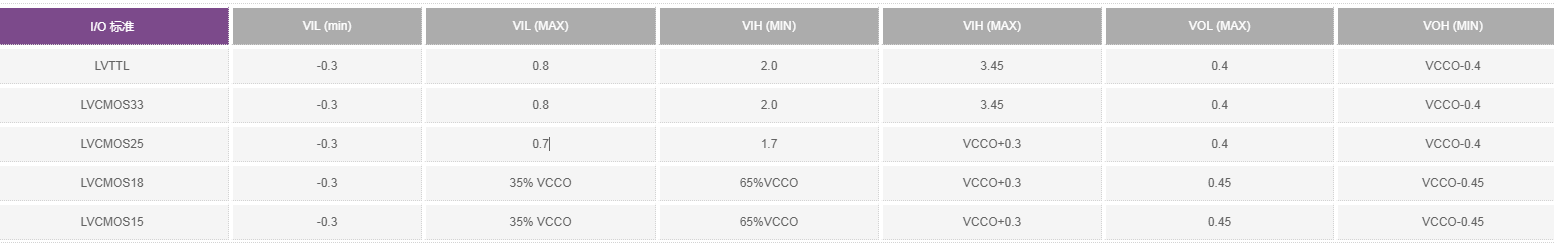

表 1 顯示了不同電壓標(biāo)準(zhǔn)的常見最低和最高電壓。如需了解更具體的數(shù)據(jù),設(shè)計師應(yīng)參考零件的數(shù)據(jù)手冊。

表 1:典型 I/O 標(biāo)準(zhǔn)及其相關(guān)的最低和最高電壓

多電壓 JTAG 鏈的設(shè)計指南

把電壓最高的器件放在鏈的開頭,接下來是電壓第二高的器件,依次類推,最后放置電壓最低的器件。按照從最高電壓到最低電壓的順序放置 JTAG 信號,允許一個器件的 TDO 輸出上的邏輯高電平可由下一個器件的輸入正確解譯。

確認(rèn)每個器件可以承受來自上一個器件的最高電壓。例如,如果第一個器件的電壓為 3.3 V,下一個器件的電壓為 1.8 V,請確保 1.8 V 器件的輸入可以至少承受 3.6 V 的電壓。

確認(rèn)來自最低電壓器件的 TDO 可由仿真器正確解譯。在本示例中,請確保 1.8 V 器件的 VOHmin 大于 3.3 V 器件的 VIHmin。否則,應(yīng)使用高速電壓轉(zhuǎn)換器將 TDO 轉(zhuǎn)換成仿真器的正確電壓。VT 不應(yīng)該寄存(時鐘)信號,因為這將延遲一個時鐘的信號,導(dǎo)致 JTAG 鏈?zhǔn) ?a href="http://www.1cnz.cn/analog/" target="_blank">模擬裝置的 ADG3304 雙向邏輯電平轉(zhuǎn)換器包含四個雙向通道,可用于多電壓數(shù)字系統(tǒng)應(yīng)用中。圖 2 顯示了具有 3.3 V、2.5 V 和 1.8 V I/O 電壓的器件,其中最低電壓器件的 I/O 可以承受上一器件的更高電壓。對 TDO 采用了電壓轉(zhuǎn)換器 (VT),以將電壓從 1.8 V 提升到 3.3 V。

當(dāng)具有較低電壓的器件不能承受上一器件的高電壓時,應(yīng)在所有 JTAG 信號上使用高速電壓轉(zhuǎn)換器。除了 TDO 外,應(yīng)將仿真器用作所有電壓轉(zhuǎn)換器的輸入。不要串聯(lián)電壓轉(zhuǎn)換器,因為這會增加傳播延遲。圖 3 說明了較低電壓器件不能承受更高電壓 I/O 的情況,因此每個信號都需要使用電壓轉(zhuǎn)換器。

如果僅有一個器件不能承受來自上一個器件的 I/O 電壓,則只需在該器件上使用電壓轉(zhuǎn)換器。例如,JTAG 鏈中具有 3.3 V、2.5 V 和 1.8 V 的 I/O 電壓,1.8 V 器件具有可以承受 2.5 V 的 I/O,因此 2.5 V 信號可由 1.8 V 器件使用。在圖 4 中,2.5 V 器件不具有可以承受 3.3 V 的 I/O,但 1.8 V 器件可以承受 2.5 V,因此只需對 2.5 V 器件使用電壓轉(zhuǎn)換器。

如果大約 0.4 V 的壓降足以將電壓從較高的水平調(diào)整到較低的水平,則可以使用具有快速恢復(fù)時間的肖特基二極管來代替電壓轉(zhuǎn)換器。ON Semiconductor 提供的 1SS383T1G 肖特基二極管具有 0.48 V 的正向電壓降和 25 pF 的容性負(fù)載。在此應(yīng)用中,也可使用 Diodes Inc. 提供的 SD103ATW,它包含三個完全隔離的肖特基二極管,具有大約 0.3 V 的正向電壓降和 50 pF 的容性負(fù)載。

-

JTAG

+關(guān)注

關(guān)注

6文章

399瀏覽量

71673 -

肖特基二極管

+關(guān)注

關(guān)注

5文章

927瀏覽量

34806 -

電壓轉(zhuǎn)換器

+關(guān)注

關(guān)注

0文章

115瀏覽量

21646

發(fā)布評論請先 登錄

相關(guān)推薦

構(gòu)建多電壓JTAG鏈的技巧

是否有可能擁有3.3V和2.5V JTAG鏈?

有什么辦法能成功編程JTAG鏈上的任何設(shè)備嗎?

如何調(diào)試JTAG鏈與非xilinx器件?

多個MCU使用的菊花鏈是怎樣通過JTAG連接的呢

PE多鏈路JTAG/BDM Kinetis編程報錯怎么解決?

T1024 codewarrior無法正確配置JTAG鏈怎么解決?

淺談參考電壓(Voltage Reference)

構(gòu)建多電壓JTAG鏈

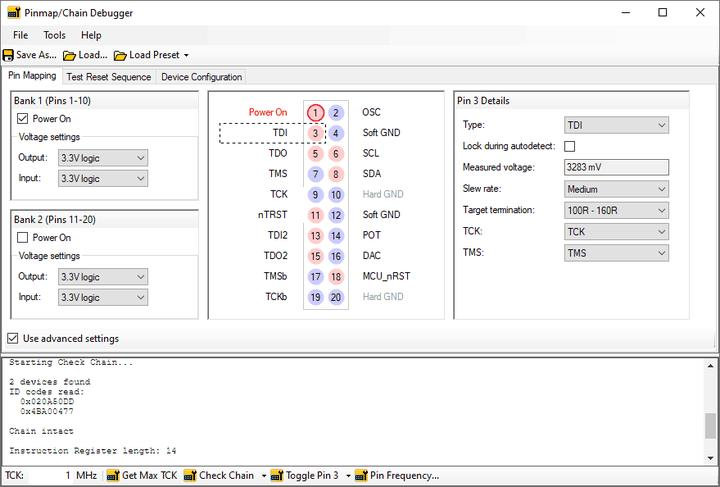

XJTAG邊界掃描—JTAG鏈調(diào)試器

SPI、UART、RGMII、JTAG接口的低電壓轉(zhuǎn)換

淺談多電壓JTAG鏈設(shè)計實現(xiàn)

淺談多電壓JTAG鏈設(shè)計實現(xiàn)

評論