簡介

LTC2387-18是一款低噪聲,高速,18位15Msps逐次逼近型寄存器(SAR)ADC。良好的線性度和寬動態(tài)范圍的結(jié)合使LTC2387-18成為高速成像和儀器儀表應(yīng)用的理想選擇。無延遲操作為高速控制環(huán)路應(yīng)用提供了獨特的解決方案。高輸入頻率下的低失真使通信應(yīng)用成為需要寬動態(tài)范圍和顯著信號帶寬的應(yīng)用。 LTC2387-18支持高速運行,同時最大限度地減少數(shù)據(jù)線數(shù)量,具有串行LVDS數(shù)字接口,可輕松連接到FPGA。 LVDS接口具有單通道和雙通道輸出模式,允許用戶優(yōu)化每個應(yīng)用的接口數(shù)據(jù)速率。

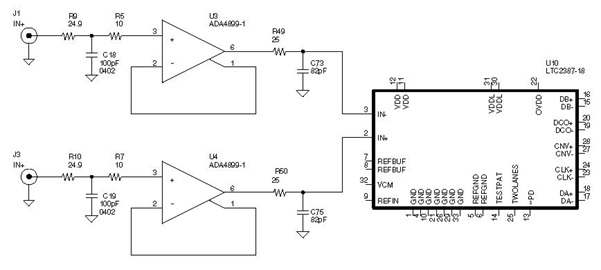

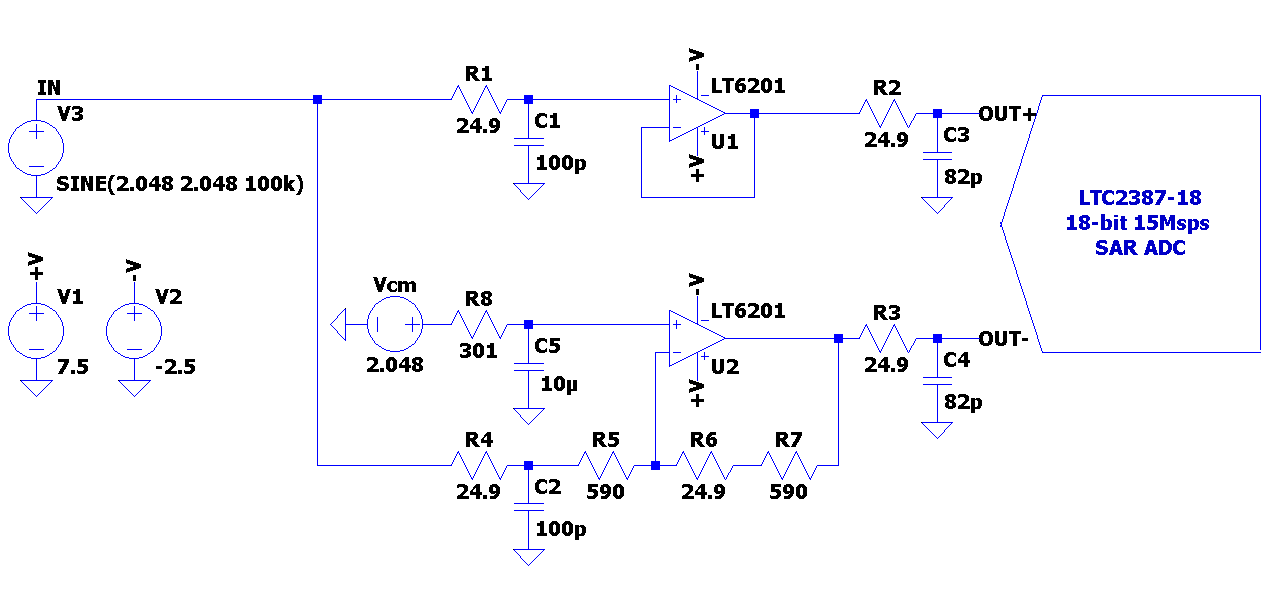

DC2290A-A是LTC2387-18的演示電路。該電路板的采樣率(Fs)為15Msps,數(shù)字化數(shù)據(jù)以串行方式退出ADC。以下是LTC2387-18,但適用于LTC2387系列的所有成員(LTC2386和LTC2385)以及DC2290A演示電路的其他變化,唯一的區(qū)別是采樣率和位數(shù)。

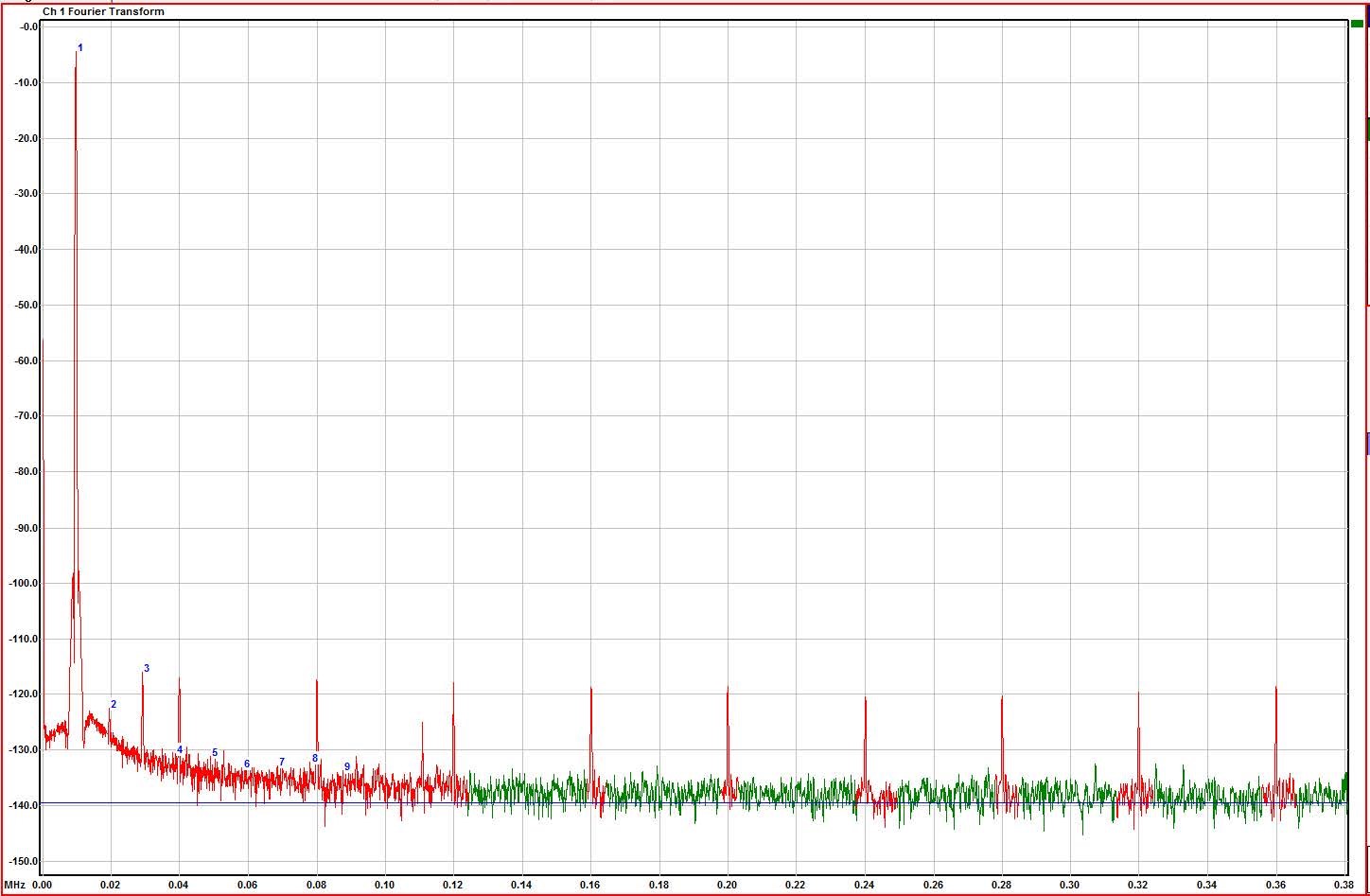

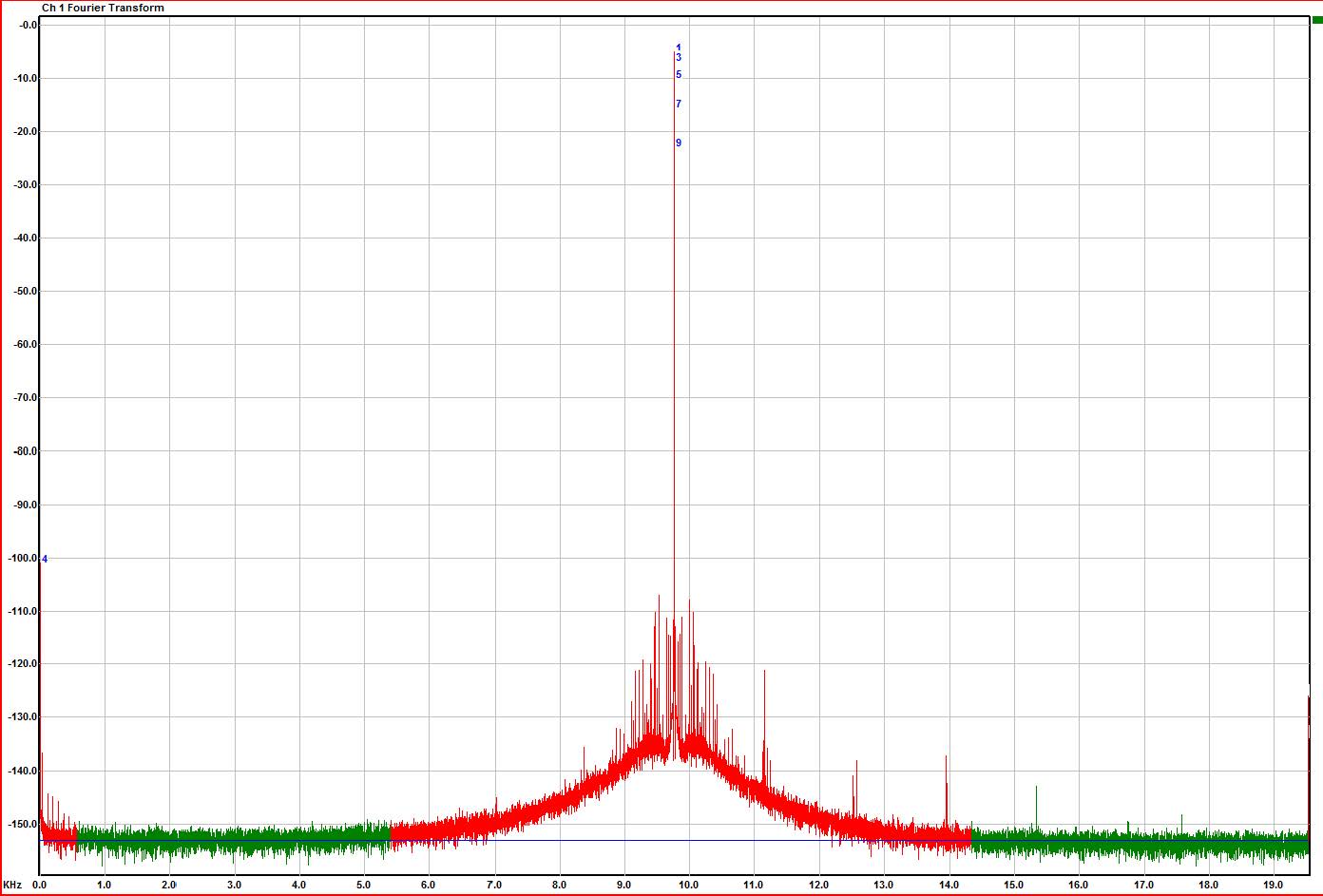

DC2290A演示電路包括一個Altera Cyclone III FPGA,它采用Verilog編程,用于對ADC輸出數(shù)據(jù)流進行反串行化,并將其傳送到DC890B USB數(shù)據(jù)采集卡的18位并行總線上。 DC890B對這些數(shù)據(jù)進行調(diào)節(jié),以便將其傳遞到PC并顯示在PSCOPE中。 PScope軟件在時域和頻域中收集和分析來自ADC的數(shù)據(jù),并顯示被評估設(shè)備的相關(guān)參數(shù)。 PSCOPE的最大FFT大小為131K,在這種情況下,每個箱的光譜分辨率約為114Hz。下面是在這些條件下9.76KHz音調(diào)的典型65K點FFT的一部分,每箱的噪聲為-139.4dBFS。

通過下采樣提高頻率分辨率&低通濾波器

如果我們想要更高的頻率分辨率或想要觀察非常接近零頻率的噪聲水平和信號怎么辦?降低采樣率是一種選擇。這應(yīng)該具有縮小箱尺寸并因此降低每箱的噪音水平的效果。這種方法的問題是混疊。別名是采樣過程的正常結(jié)果。這意味著模擬輸入光譜被切成Fs / 2寬的塊,它們彼此重疊以構(gòu)成最終輸出光譜。通常,選擇采樣率使得模擬輸入信號內(nèi)容的大部分低于Fs / 2。通過對模擬輸入信號和噪聲進行低通濾波,信號內(nèi)容限于該頻譜區(qū)域。這就是簡單地降低采樣率的問題 - 這意味著用戶必須降低模擬輸入信號或ADC之前的低通濾波器的帶寬。這些措施都不實用。

更好的選擇是單獨保留采樣率并對ADC的數(shù)字化輸出進行下采樣。注意,為了避免信號和噪聲的混疊(如上所述),我們必須在下采樣之前對輸出進行低通濾波。這是使用數(shù)字濾波器而不是模擬濾波器完成的。因為這可以在FPGA中完成,所以很容易實現(xiàn)和修改。例如,如果我們有一個通過15Msps采樣獲得的頻譜,我們可能希望將頻率分辨率提高128倍。為了有效地做到這一點,輸出樣本必須限制在介于0Hz和7.5之間的頻譜。 / 128MHz,或58.593KHz。然后可以將樣本下采樣128倍,很少或沒有混疊。分辨率將增加128倍,每個bin的噪聲應(yīng)比原始頻譜低21dB。

這個處理可以通過在現(xiàn)有的Verilog代碼上添加一個模塊來完成。 18位數(shù)據(jù)字在傳遞到數(shù)據(jù)收集系統(tǒng)之前。然后編譯新版本的代碼,可用于在JTAG或主動串行編程模式下對DC2290A演示板進行編程。

梳狀積分器級聯(lián)濾波器

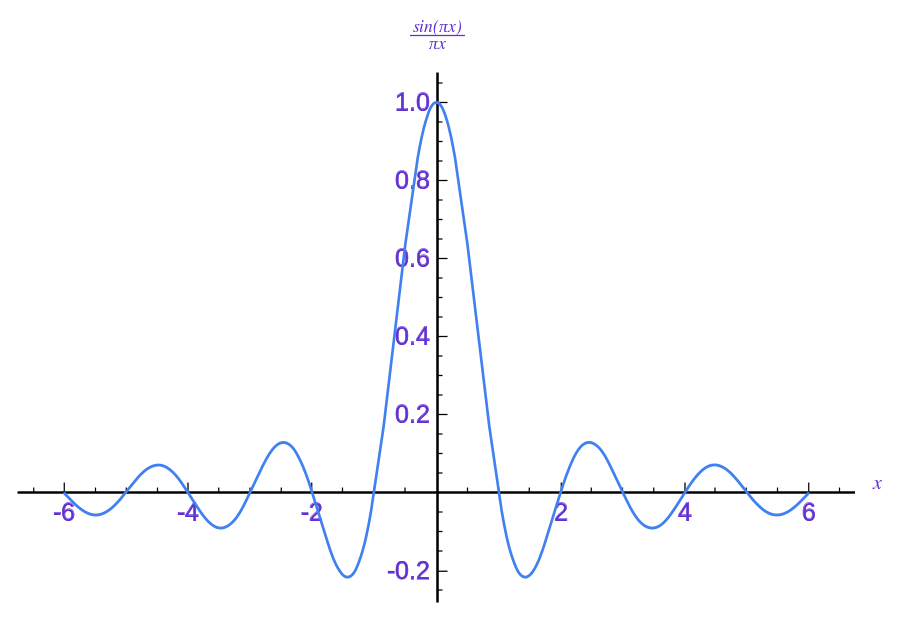

《 p》低通濾波器和下采樣的一種簡單方法是使用梳狀積分器級聯(lián)(CIC)濾波器。該過濾器的獨特之處在于它不需要乘法。 CIC過濾器實際上只是移動平均(或boxcar)過濾器的另一個名稱,后面跟著一個下采樣器。注意,該濾波器的脈沖響應(yīng)僅僅是一系列N個單位幅度樣本。由于濾波器的時間響應(yīng)是矩形脈沖,因此頻率響應(yīng)是Dirichlet函數(shù)。

sin(πfN)/(Nsin(πf))

此函數(shù)的第一個空值為Fs / N,在本例中為117.187KHz。下面是此過濾器的低頻響應(yīng)示例。

在Verilog中實現(xiàn)CIC過濾器

有幾種方法可以實現(xiàn)此目的在Verilog過濾。一種方法是建立一個移位寄存器,該寄存器保存N個數(shù)據(jù)字,在加載每個新字時對寄存器的N個位置求和。然后對求和的輸出進行下采樣以形成最終輸出。以下是N = 128的示例。

首先,F(xiàn)PGA對18位數(shù)據(jù)字進行反序列化。

該字以及運行頻率為15MHz的時鐘傳遞給模塊cic_128

wire [17:0] dout,dout_f;

cic_128 fir(

.clk(fir_clk),

.din (DOUT),結(jié)果,.dout(dout_f),點擊);

第一個變量是時鐘;在轉(zhuǎn)換的反序列化數(shù)據(jù)可用之后,此時鐘的上升沿出現(xiàn)。接下來的兩個變量是18位數(shù)據(jù)字 - 第一個是濾波器輸入,第二個是輸出。以下是模塊本身的代碼。

clk,

din,

dout

);

輸入clk;

輸入[17:0] din; //未過濾的樣本

輸出[17:0] dout; //過濾樣本

reg [2303:0] shift_reg;

reg [24:0] regout;

reg [17:0] dout;

initial

shift_reg = 0;

wire [24:0] regout_a [63:0];

wire [24:0] regout_b [31:0];

wire [24:0] regout_c [15:0] ;

wire [24:0] regout_d [7:0];

wire [24:0] regout_e [3:0];

wire [24:0] regout_f [1:0]; 《 br》 wire [24:0] regout_g;

始終@(posedge clk)//在‘clk’的每個上升沿將最新的位加載到串行位數(shù)組中《 br》開始

:7];

end

genvar j;

生成

for(j = 0; j 《64; j = j + 1)

begin:echelon_a

assign regout_a [j] = {{7 {shift_reg [j * 18 + 17]}},shift_reg [j * 18 + 17:j * 18]} + {{7 {shift_reg [(j 64)* 18 + 17]}},shift_reg [第(j + 64)* 18 + 17:(J + 64)* 18]};結(jié)果,端

《跨度》 for(j = 0; j 《32; j = j + 1)開始:echelon_b

分配regout_b [j] = regout_a [j] + regout_a [j + 32];

結(jié)束

for(j = 0; j 《16; j = j + 1)開始:echelon_c

assign regout_c [j] = regout_b [j] + regout_b [ J + 16];結(jié)果,端

for(j = 0; j 《8; j = j + 1)開始:echelon_d

分配regout_d [j] = regout_c [j] + regout_c [j + 8]; 《 br》結(jié)束

for(j = 0; j 《4; j = j + 1)開始:echelon_e

assign regout_e [j] = regout_d [ j] + regout_d [j + 4];

end

for(j = 0; j 《2; j = j + 1)開始:echelon_f

分配regout_f [j] = regout_e [j] + regout_e [j + 2];

end

endgenerate

分配regout_g = regout_f [0] + regout_f [1];

endmodule

模塊的核心是 shift_reg ;這是一個移位寄存器,可容納128 x 18位字。這些字是一個接一個地加載到移位寄存器中的數(shù)據(jù)輸入 din 。在每個時鐘上升沿,最新的數(shù)據(jù)字被加載到寄存器中,最舊的數(shù)據(jù)字被丟棄。寄存器中128個位置的總和是濾波器的輸出。然后將該輸出按比例縮小7位以適合18位字,并作為 dout 傳遞回主模塊。此時,這些樣本的頻譜只是ADC輸出的低通濾波副本。

下一步是下采樣,通過傳遞每128個濾波器樣本來完成到數(shù)據(jù)采集板

第1部分的結(jié)果

結(jié)果是一個覆蓋從DC到58.593KHz的奈奎斯特區(qū)域的光譜。使用65K點的FFT,箱寬為1.78Hz。這是濾波和下采樣信號的FFT,每個區(qū)間的噪聲為-151.3dBFS。

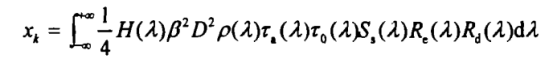

每個區(qū)間的噪聲水平每箱減少了近12dB。由于兩個原因,這低于預(yù)測的21dB減少。首先,因為濾波器不理想,所以在通帶外存在非零響應(yīng)。下采樣過程會將這些非零波瓣中的噪聲混疊回通帶。這些旁瓣的總功率大約是主瓣功率的十分之一。其次,更重要的是,最終頻譜中的量化噪聲。對于正弦波,量化噪聲使用以下公式計算,其中N是位數(shù)。

SNR = 1.76 + 6.02 * N

最終樣本量化為18位,量化噪聲約等于110.1dB,或每箱為155.3dBFS。通過濾波和下采樣獲得的結(jié)果接近這一水平,揭示了更多的光譜細節(jié)和分辨率。

使用Altera Cyclone III FPGA對這些數(shù)據(jù)進行反序列化和過濾是資源密集型的。 Verilog代碼的編譯報告顯示該實現(xiàn)使用了74%的可用邏輯元素。原因是所需的寄存器和加法器的數(shù)量。在每個采樣時刻,所有128個寄存器以二進制方式加在一起,梯隊后梯隊。嘗試構(gòu)建具有更高下采樣率的濾波器將失敗,因為該設(shè)計將不適合該FPGA。還有其他更簡化的方法來構(gòu)建這種類型的過濾器,我們將在下一部分中介紹它。右側(cè)面板上提供了Verilog和本文所述代碼的編程文件。

-

寄存器

+關(guān)注

關(guān)注

31文章

5336瀏覽量

120237 -

usb

+關(guān)注

關(guān)注

60文章

7939瀏覽量

264494 -

adc

+關(guān)注

關(guān)注

98文章

6496瀏覽量

544477

發(fā)布評論請先 登錄

相關(guān)推薦

高光譜成像系統(tǒng):高光譜數(shù)據(jù)光譜分辨率對礦物識別的影響分析

貿(mào)澤開售Analog Devices LTC6228和LTC6229運算放大器

[轉(zhuǎn)帖]儀器儀表應(yīng)用領(lǐng)域

【AD新聞】中國深圳先進院在高分辨率超聲成像領(lǐng)域取得重要進展

LTC2386CUH-18PBF模數(shù)轉(zhuǎn)換器

RF成像分辨率怎么提高

LTC2387-18正弦信號驅(qū)動器的設(shè)計要求

LT6201/LTC6655 Demo Circuit - Single-Ended to Differential Amplifier for LTC2387-18

LTC2387-18:18位,15mps SAR數(shù)據(jù)Sheet

LT6201LTC6655演示電路-LTC2387-18的單端至差分放大器

成像光譜儀是一款具有高光譜分辨率方式獲取圖像信息的儀器

用于LTC2387-18 SAR ADC的單端至差分驅(qū)動器電路

什么是光譜分辨率東方閃光告訴您

大視場超分辨率高速成像的優(yōu)勢分析

基于圖像光譜超分辨率的蘋果糖度檢測

提高LTC2387-18在高速成像和儀器儀表應(yīng)用中的光譜分辨率

提高LTC2387-18在高速成像和儀器儀表應(yīng)用中的光譜分辨率

評論